在 FPGA 学习过程中,你是否也曾遇到过这些问题:

教材晦涩难懂,电路图和代码脱节?

找不到既系统又实战的开源学习资料?

工具链配置复杂,不知从何下手?

如果你点头了,那么今天推荐的开源项目 Project F,可能就是你期待已久的答案。

什么是 Project F?

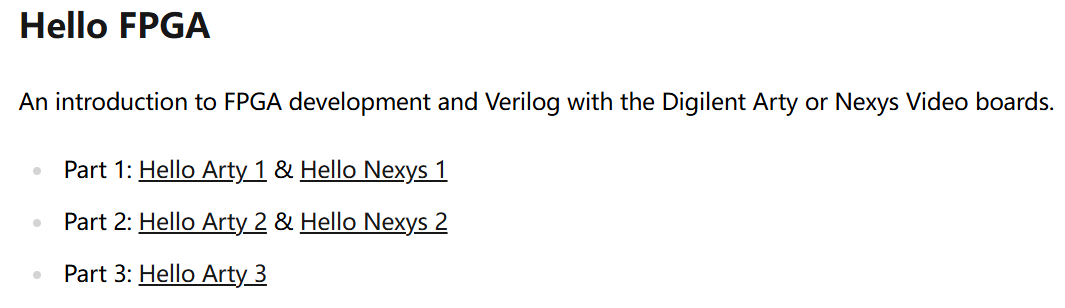

Project F 是一个完全开源的、面向学习者的 FPGA 教程项目,由英国开发者 Will Green 维护,旨在帮助开发者从零开始学习数字逻辑和硬件设计。

项目口号非常朴素:“People who are really serious about software should make their own hardware.”

Project F 的特色在于:

✅ 清晰的结构

✅ 基于 Verilog 语言

✅ 配套图文教程

✅ 开源工具链优先支持(如 Yosys/NextPNR)

✅ 支持多个开源开发板:iCEBreaker、ULX3S、Tang Nano 9K、Nexys A7 等

Project F 是一个系统性的教程集合,涵盖多个方面的数字设计知识:

入门篇:基础逻辑

👉 适合初学者快速上手 FPGA 开发流程。

图形篇:像素级硬件乐趣

👉 用 HDL 实现复古风游戏图形,学习时钟控制、缓冲区与同步技术。

数学篇:在电路中运算

👉 适合工程专业的计算机图形学/算法硬件化设计课题实践。

还有很多中高级教程可以自己去探索~

为什么值得推荐?

✅ 学术 + 实战结合

作者本身具备工程背景,所有设计都可直接运行在实板上,不是“空中楼阁”。

✅ 不依赖昂贵软件

教程默认基于开源工具链(Yosys + NextPNR),也支持 Vivado,让学习不再被 EDA 软件绑架。

✅ 项目结构清晰

每一个例子都有独立的目录、Makefile 构建系统、README 指南和 Block Diagram 图。

✅ 社区友好

项目作者更新频繁,回复 issues 积极,也推荐大量其它优秀资源。

支持的开发板示例

开发板 | FPGA芯片 | 是否支持 |

|---|---|---|

iCEBreaker | iCE40UP5K | ✅ |

ULX3S | ECP5 | ✅ |

Tang Nano 9K | GW1NR-9C | ✅ |

Nexys A7 | Artix-7 | ✅ |

如果你有一块 Lattice 或 Xilinx 开发板,几乎可以无缝上手。

项目链接

https://github.com/projf/projf-explore

项目主页

https://projectf.io/

写在最后:让 FPGA 不再“高不可攀”

Project F 不是另一个纸上谈兵的教学框架,而是一整套“能跑起来”的真实工程逻辑项目。它就像嵌入式开发的 STM32CubeMX 或 Arduino IDE —— 帮助你快速构建出第一个作品。

如果你是一位:

数电/嵌入式专业的学生

想入门 FPGA 的程序员

高校老师/训练营主理人

爱好 DIY 的创客

那么请不要错过这个宝藏项目,它正是你通向硬件世界的桥梁。

2869

2869

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?