系列文章目录

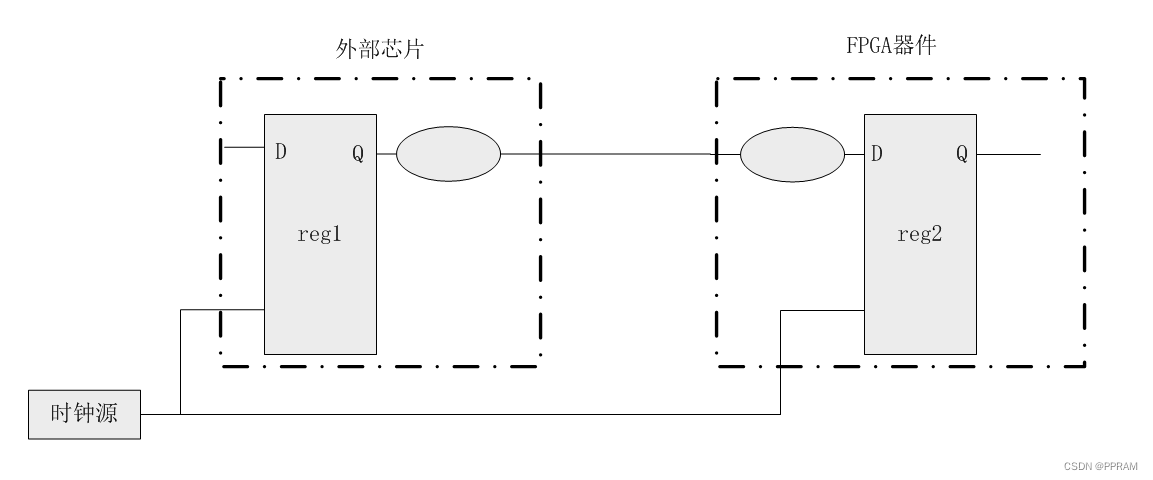

一、系统同步接口

二、系统同步接口路径分析

- Tci_pcb:时钟从时钟源到达外部芯片所经过的PCB走线延迟;

- Tco:时钟到达外部芯片引脚,一直到外部芯片数据输出所经过的延迟;(源时钟到寄存器引脚+数据经过寄存器时间)

- Td_pcb:数据信号在PCB线上经过的延迟;

- Tpin2reg:数据信号从FPGA引脚到达目的寄存器reg2所经过的延迟;

- Tc2j_pcb:源时钟经过PCB到达FPGA所经过的延迟;

- Tc2j_fp:时钟从FPGA引脚到达reg2寄存器所经过的延迟;

建立时间:

Data Arrival Time = Launch Edge + Tc2i_pcb(max) + Tco(max) + Td_pcb(max) + Tpin2reg(max)

Data Required Time = Latch Edge + Tc2j_pcb(min) + Tc2j_fp(min) - Tsu -Clock Uncertain

Setup Time = Data Required Time - Data Arrival Time = Latch Edge - Launch Ed

该文详细阐述了基于FPGA的时序分析,主要关注系统同步接口和源同步接口路径的分析。讨论了关键参数如时钟延迟、数据延迟和建立/保持时间,并提供了输入延迟约束的计算方法。

该文详细阐述了基于FPGA的时序分析,主要关注系统同步接口和源同步接口路径的分析。讨论了关键参数如时钟延迟、数据延迟和建立/保持时间,并提供了输入延迟约束的计算方法。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

585

585

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?