在Verilog中,所有的线网和变量都是使用四态值,因此没必要也不能清晰的区分信号类型。

为了增强灵活性,SystemVerilog中定义信号同时具有类型和数据类型两个属性。

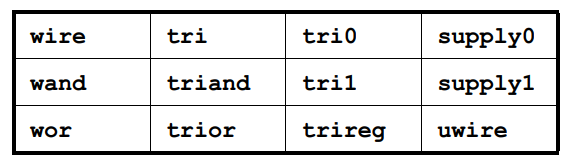

类型指示信号是属于线网(net)还是变量(var)。SV使用所有的Verilog线网类型,并且没有进行任何拓展。

需要注意的是,线网类型必须配合使用四态数据类型,一般情况下省略数据类型,默认为四态。

数据类型指示线网或者变量的值系统。对于四态数据类型就是0、1、Z或X,对于两态数据类型就是0或1。

关键字logic是一个数据类型。当logic单独使用时,则隐含这是一个变量var,四态变量可以使用一对关键字var logic进行显式声明。例如:

var logic [31:0] data; //一个32位宽的变量

当然,线网类型也可以使用logic显示声明为四态数据类型。如下:

wire logic [31:0] addr; //一个32位宽的线网

从语义上来说,SV中的logic数据类型和Verilog中的reg类型是一样的,可以互换使用,更多的是兼容wire类型。

SV中的两态数据变量

相比Verilog中的四态数据类型,SV中引入了两状态的数据类型,有利于提高仿真器的性能并且减少内存的使用量,更加适合在高层次建模和验证。两态数据类型只能用于变量类型。这些类型如下:

bit --1位两态无符号整数

byte --8位两态有符号整数

shortint --8位两态有符号整数

int --16位两态有符号整数

longint --32位两态有符号整数

本文介绍了SystemVerilog中的信号类型,包括线网和变量的区别,四态和两态数据类型的使用及特性,以及如何声明不同类型的信号。

本文介绍了SystemVerilog中的信号类型,包括线网和变量的区别,四态和两态数据类型的使用及特性,以及如何声明不同类型的信号。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2892

2892

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?