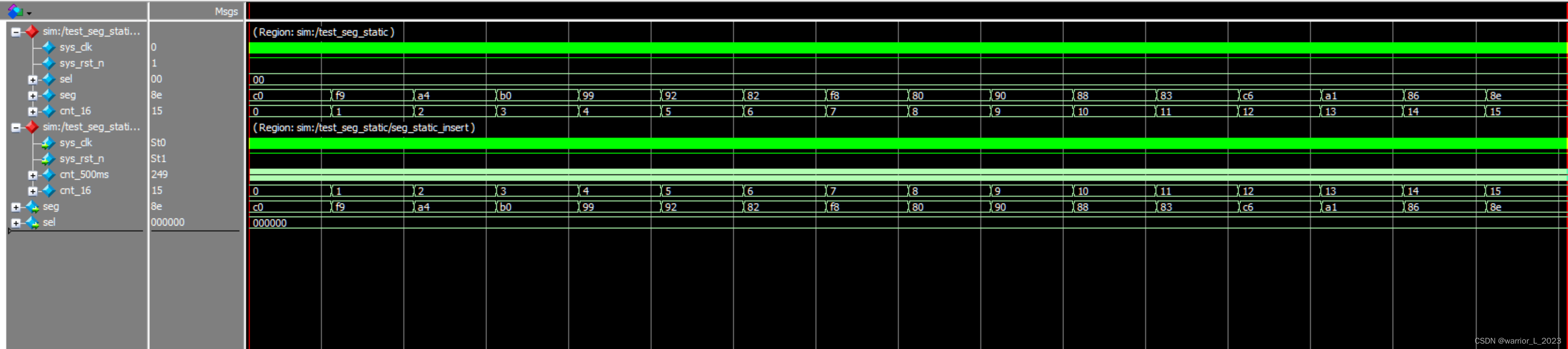

`timescale 1ns/1ns

module test_seg_static();

reg sys_clk ;

reg sys_rst_n ;

wire [5:0] sel ;

wire [7:0] seg ;

wire [5:0] cnt_16 ;

assign cnt_16 = seg_static_insert.cnt_16 ;

seg_static

#(

.MAX_500ms ( 25_0 ) ,

.M_16 ( 16 )

)

seg_static_insert (

.sys_clk ( sys_clk ) ,

.sys_rst_n ( sys_rst_n ) ,

.sel ( sel ) ,

.seg ( seg )

);

parameter CYCLE = 20 ;

initial begin

sys_clk = 1'b1 ;

sys_rst_n <= 1'b0 ;

#( CYCLE * 10 ) ;

sys_rst_n <= 1'b1 ;

#( 210 ) ;

sys_rst_n <= 1'b0 ;

#( 10 ) ;

#( CYCLE * 10 ) ;

sys_rst_n <= 1'b1 ;

#( CYCLE * 1000 ) ;

end

always #( CYCLE / 2 ) sys_clk = ~sys_clk ;

initial begin

$timeformat(-9,0,"ns",6) ;

/* (第一个位置)

-9 是10 的负9次方 表示纳秒

-3 表示毫秒

*/

/* (第二个位置)

0 表示,小数点后显示的位数

*/

/* (第三个位置)

“打印字符” 与单位相对应

*/

/* (第四个位置)

6 表示 打印的最小数字字符 是6个

*/

$monitor("@time %t:sel=%b,seg=%b,cnt_16=%b",$time,sel,seg,cnt_16) ; // 监测函数

end

endmodule

module seg_static

#(

parameter MAX_500ms = 25'd25_000_000 ,

M_16 = 5'd16

)(

input wire sys_clk ,

input wire sys_rst_n ,

output reg [5:0] sel ,

output reg [7:0] seg

);

// localparam

localparam ZERO = 8'hc0 ,

ONE = 8'hf9 ,

TWO = 8'ha4 ,

THREE = 8'hb0 ,

FOUR = 8'h99 ,

FIVE = 8'h92 ,

SIX = 8'h82 ,

SEVEN = 8'hf8 ,

EIGHT = 8'h80 ,

NINE = 8'h90 ,

A = 8'h88 ,

B = 8'h83 ,

C = 8'hc6 ,

D = 8'ha1 ,

E = 8'h86 ,

F = 8'h8e ;

// reg signal define

reg [24:00] cnt_500ms ;

reg [04:00] cnt_16 ;

reg add_flag ;

// cnt_500ms

always @(posedge sys_clk or negedge sys_rst_n) begin

if(~sys_rst_n) begin

cnt_500ms <= 25'd0 ;

end else begin

if(cnt_500ms == (MAX_500ms - 25'b1)) begin

cnt_500ms <= 25'd0 ;

end else begin

cnt_500ms <= cnt_500ms + 25'b1 ;

end

end

end

// add_flag

always @(posedge sys_clk or negedge sys_rst_n) begin

if(~sys_rst_n) begin

add_flag <= 1'b0 ;

end else begin

if(cnt_500ms == (MAX_500ms - 25'd2)) begin

add_flag <= 1'b1 ;

end else begin

add_flag <= 1'b0 ;

end

end

end

// cnt_16

always @(posedge sys_clk or negedge sys_rst_n) begin

if(~sys_rst_n) begin

cnt_16 <= 5'd0 ;

end else begin

if( add_flag && cnt_16 == (M_16 - 5'd1) ) begin

cnt_16 <= 5'd0 ;

end else begin

if(cnt_500ms == (MAX_500ms - 5'd1)) begin

cnt_16 <= cnt_16 + 5'd1 ;

end else begin

cnt_16 <= cnt_16 ;

end

end

end

end

// sel

always @(posedge sys_clk or negedge sys_rst_n) begin

if(~sys_rst_n) begin

sel <= 6'b000_000 ;

end else begin

sel <= 6'b111_111 ;

end

end

// seg

always @(posedge sys_clk or negedge sys_rst_n) begin

if(~sys_rst_n) begin

seg <= 8'hff ;

end else begin

case (cnt_16)

0 : begin

seg <= ZERO ;

end

1 : begin

seg <= ONE ;

end

2 : begin

seg <= TWO ;

end

3 : begin

seg <= THREE ;

end

4 : begin

seg <= FOUR ;

end

5 : begin

seg <= FIVE ;

end

6 : begin

seg <= SIX ;

end

7 : begin

seg <= SEVEN ;

end

8 : begin

seg <= EIGHT ;

end

9 : begin

seg <= NINE ;

end

10 : begin

seg <= A ;

end

11 : begin

seg <= B ;

end

12 : begin

seg <= C ;

end

13 : begin

seg <= D ;

end

14 : begin

seg <= E ;

end

15 : begin

seg <= F ;

end

default: seg <= 8'hff ;

endcase

end

end

endmodule

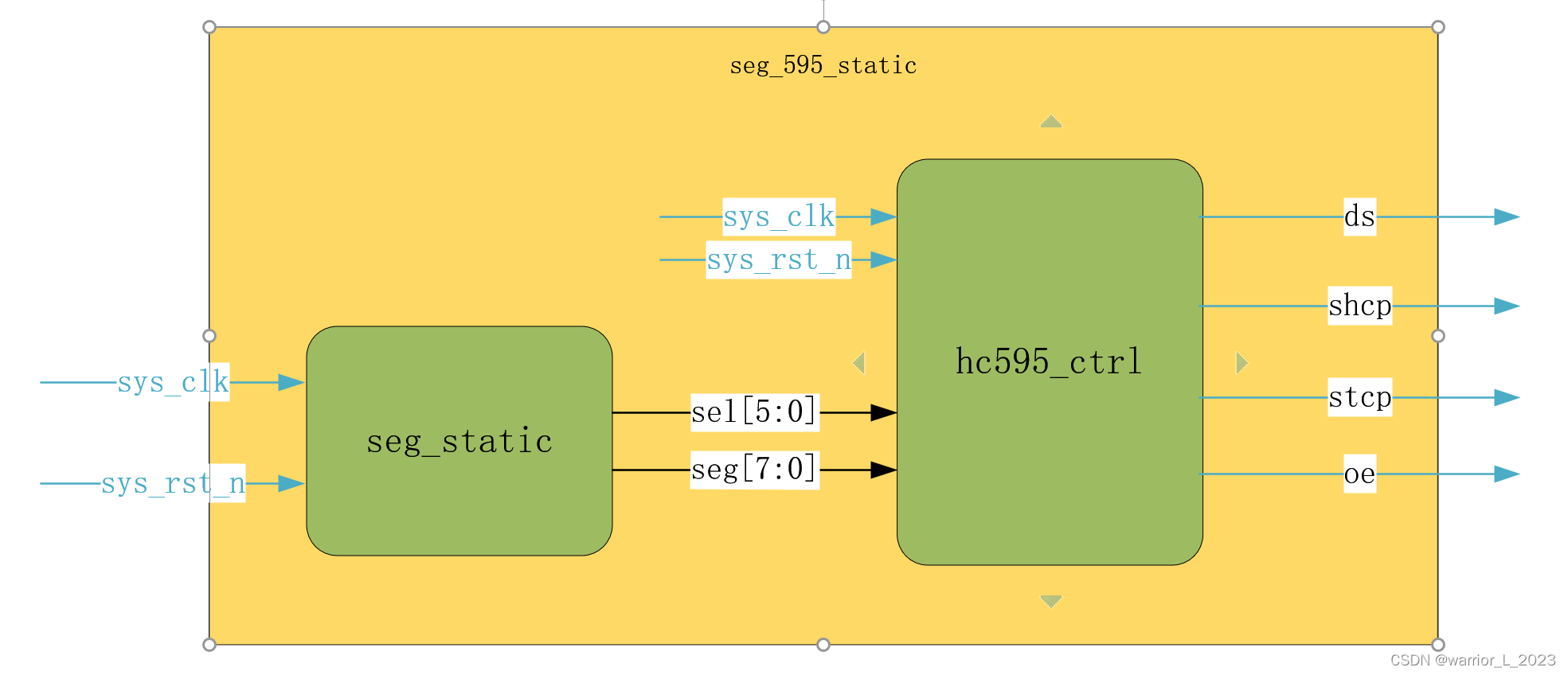

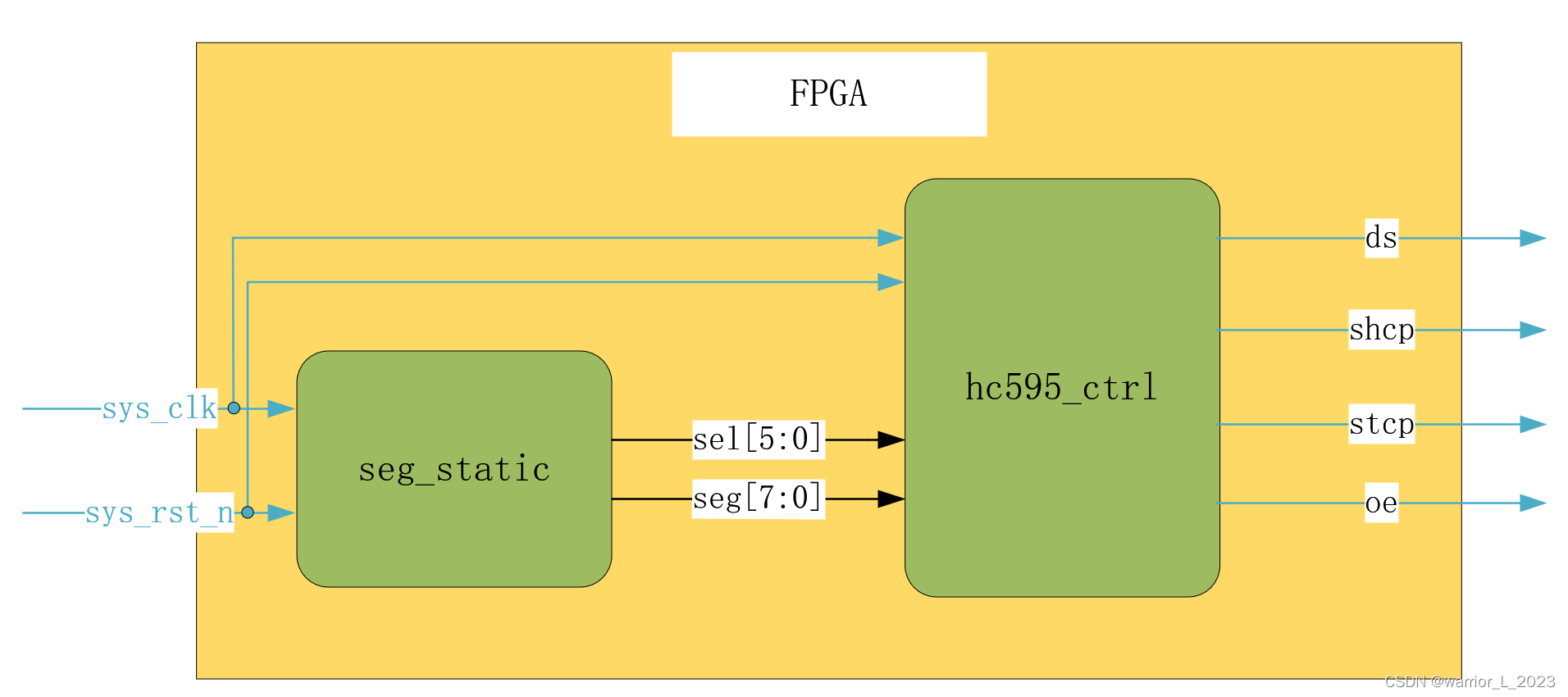

module top(

input wire sys_clk ,

input wire sys_rst_n ,

output wire ds ,

output wire shcp ,

output wire stcp ,

output wire oe

);

wire [5:0] sel ;

wire [7:0] seg ;

seg_static seg_static_insert (

.sys_clk ( sys_clk ) ,

.sys_rst_n ( sys_rst_n ) ,

.sel ( sel ) ,

.seg ( seg )

);

hc595_ctrl hc595_ctrl_insert (

.sys_clk ( sys_clk ) ,

.sys_rst_n ( sys_rst_n ) ,

.seg ( seg ) ,

.sel ( sel ) ,

.ds ( ds ) ,

.shcp ( shcp ) ,

.stcp ( stcp ) ,

.oe ( oe )

);

endmodule

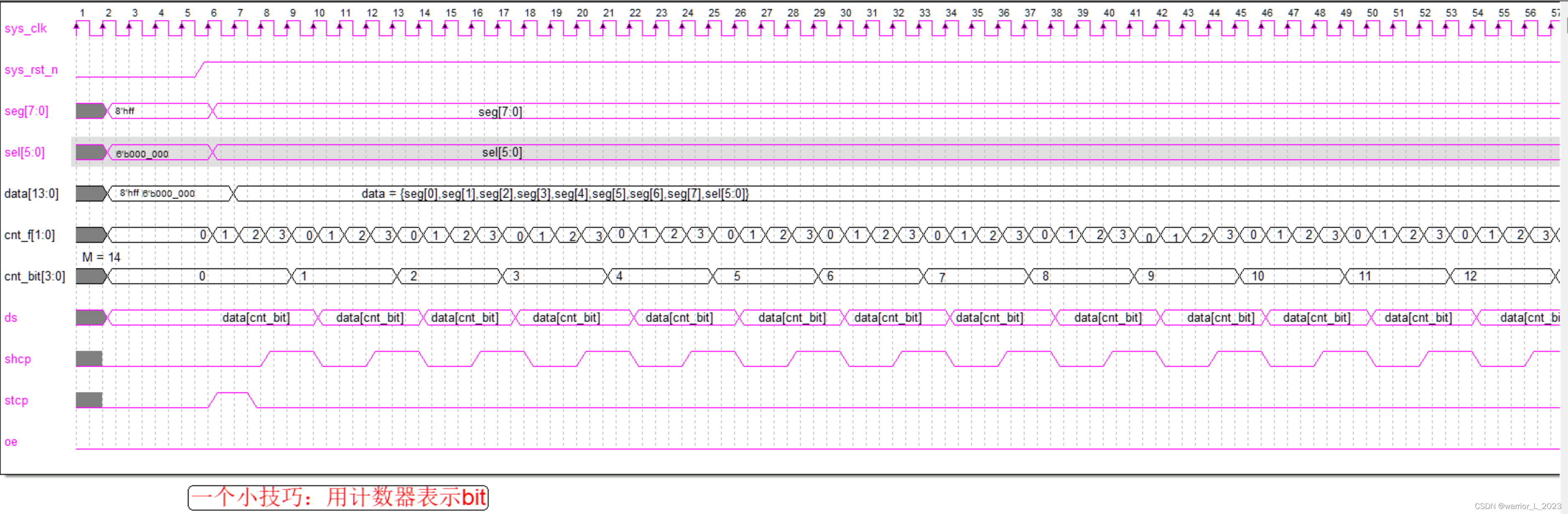

module hc595_ctrl(

input wire sys_clk ,

input wire sys_rst_n ,

input wire [7:0] seg ,

input wire [5:0] sel ,

output wire ds ,

output reg shcp ,

output reg stcp ,

output wire oe

);

// reg signal define

wire [13:00] data ;

reg [01:00] cnt_f ;

reg [03:00] cnt_bit ;

// data

// reg [13:00] data ;

// always @(posedge sys_clk or negedge sys_rst_n) begin

// if(~sys_rst_n) begin

// data <= {seg[0],seg[1],seg[2],seg[3],seg[4],seg[5],seg[6],seg[7],sel[5:0]} ;

// end else begin

// data <= {seg[0],seg[1],seg[2],seg[3],seg[4],seg[5],seg[6],seg[7],sel[5:0]} ;

// end

// end

assign data = {seg[0],seg[1],seg[2],seg[3],seg[4],seg[5],seg[6],seg[7],sel[5:0]} ;

// cnt_f

always @(posedge sys_clk or negedge sys_rst_n) begin

if(~sys_rst_n) begin

cnt_f <= 2'd0 ;

end else begin

if(cnt_f == 2'd3) begin

cnt_f <= 2'd0 ;

end else begin

cnt_f <= cnt_f + 2'd1 ;

end

end

end

// cnt_bit

always @(posedge sys_clk or negedge sys_rst_n) begin

if(~sys_rst_n) begin

cnt_bit <= 4'd0 ;

end else begin

if(cnt_f == 2'd3) begin

if(cnt_bit == 4'd13) begin

cnt_bit <= 4'd0 ;

end else begin

cnt_bit <= cnt_bit + 4'd1 ;

end

end else begin

cnt_bit <= cnt_bit ;

end

end

end

// out signal

// ds

// always @(posedge sys_clk or negedge sys_rst_n) begin

// if(~sys_rst_n) begin

// ds <= data[cnt_bit] ;

// end else begin

// ds <= data[cnt_bit] ;

// end

// end

assign ds = data[cnt_bit] ;

// shcp

always @(posedge sys_clk or negedge sys_rst_n) begin

if(~sys_rst_n) begin

shcp <= 1'b0 ;

end else begin

if(cnt_f == 2'd2 || cnt_f == 2'd3) begin

shcp <= 1'b1 ;

end else begin

shcp <= 1'b0 ;

end

end

end

// stcp

always @(posedge sys_clk or negedge sys_rst_n) begin

if(~sys_rst_n) begin

stcp <= 1'b0 ;

end else begin

if(cnt_bit == 4'd0 && (cnt_f == 2'd0 || cnt_f == 2'd1)) begin

stcp <= 1'b1 ;

end else begin

stcp <= 1'b0 ;

end

end

end

// oe

assign oe = 1'b0 ;

endmodule

module seg_static

#(

parameter MAX_500ms = 25'd25_000_000 ,

M_16 = 5'd16

)(

input wire sys_clk ,

input wire sys_rst_n ,

output reg [5:0] sel ,

output reg [7:0] seg

);

// localparam

localparam ZERO = 8'hc0 ,

ONE = 8'hf9 ,

TWO = 8'ha4 ,

THREE = 8'hb0 ,

FOUR = 8'h99 ,

FIVE = 8'h92 ,

SIX = 8'h82 ,

SEVEN = 8'hf8 ,

EIGHT = 8'h80 ,

NINE = 8'h90 ,

A = 8'h88 ,

B = 8'h83 ,

C = 8'hc6 ,

D = 8'ha1 ,

E = 8'h86 ,

F = 8'h8e ;

// reg signal define

reg [24:00] cnt_500ms ;

reg [04:00] cnt_16 ;

reg add_flag ;

// cnt_500ms

always @(posedge sys_clk or negedge sys_rst_n) begin

if(~sys_rst_n) begin

cnt_500ms <= 25'd0 ;

end else begin

if(cnt_500ms == (MAX_500ms - 25'b1)) begin

cnt_500ms <= 25'd0 ;

end else begin

cnt_500ms <= cnt_500ms + 25'b1 ;

end

end

end

// add_flag

always @(posedge sys_clk or negedge sys_rst_n) begin

if(~sys_rst_n) begin

add_flag <= 1'b0 ;

end else begin

if(cnt_500ms == (MAX_500ms - 25'd2)) begin

add_flag <= 1'b1 ;

end else begin

add_flag <= 1'b0 ;

end

end

end

// cnt_16

always @(posedge sys_clk or negedge sys_rst_n) begin

if(~sys_rst_n) begin

cnt_16 <= 5'd0 ;

end else begin

if( add_flag && cnt_16 == (M_16 - 5'd1) ) begin

cnt_16 <= 5'd0 ;

end else begin

if(cnt_500ms == (MAX_500ms - 5'd1)) begin

cnt_16 <= cnt_16 + 5'd1 ;

end else begin

cnt_16 <= cnt_16 ;

end

end

end

end

// sel

always @(posedge sys_clk or negedge sys_rst_n) begin

if(~sys_rst_n) begin

sel <= 6'b000_000 ;

end else begin

sel <= 6'b111_111 ;

end

end

// seg

always @(posedge sys_clk or negedge sys_rst_n) begin

if(~sys_rst_n) begin

seg <= 8'hff ;

end else begin

case (cnt_16)

0 : begin

seg <= ZERO ;

end

1 : begin

seg <= ONE ;

end

2 : begin

seg <= TWO ;

end

3 : begin

seg <= THREE ;

end

4 : begin

seg <= FOUR ;

end

5 : begin

seg <= FIVE ;

end

6 : begin

seg <= SIX ;

end

7 : begin

seg <= SEVEN ;

end

8 : begin

seg <= EIGHT ;

end

9 : begin

seg <= NINE ;

end

10 : begin

seg <= A ;

end

11 : begin

seg <= B ;

end

12 : begin

seg <= C ;

end

13 : begin

seg <= D ;

end

14 : begin

seg <= E ;

end

15 : begin

seg <= F ;

end

default: seg <= 8'hff ;

endcase

end

end

endmodule

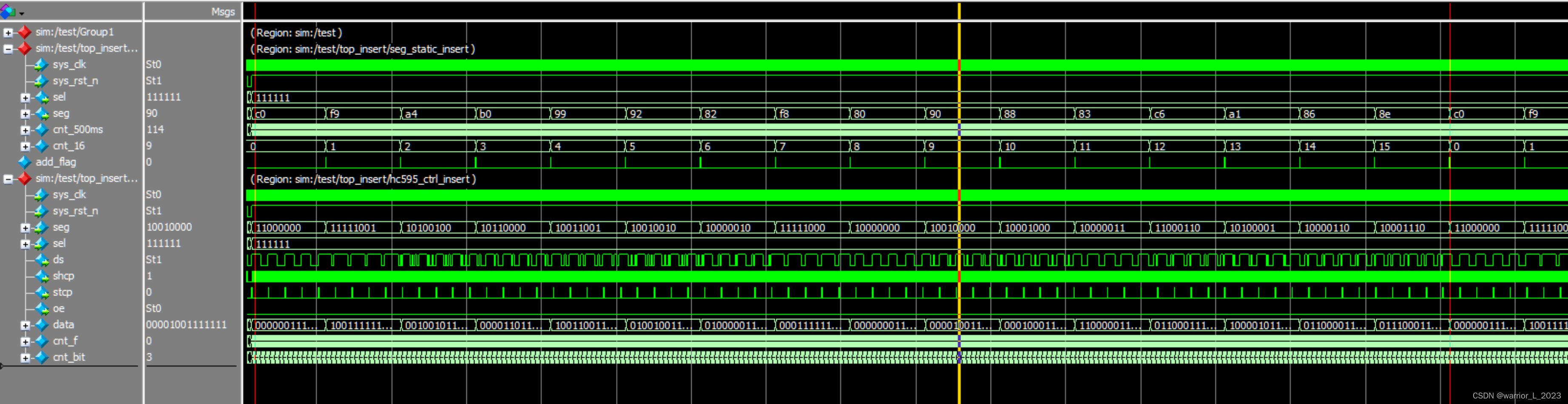

`timescale 1ns/1ns

module test();

reg sys_clk ;

reg sys_rst_n ;

wire ds ;

wire shcp ;

wire stcp ;

wire oe ;

wire [13:00] data ;

wire [03:00] cnt_bit ;

assign data = top_insert.hc595_ctrl_insert.data ;

assign cnt_bit = top_insert.hc595_ctrl_insert.cnt_bit ;

top top_insert (

.sys_clk ( sys_clk ) ,

.sys_rst_n ( sys_rst_n ) ,

.ds ( ds ) ,

.shcp ( shcp ) ,

.stcp ( stcp ) ,

.oe ( oe )

);

defparam top_insert.seg_static_insert.MAX_500ms = 250 ;

parameter CYCLE = 20 ;

initial begin

sys_clk = 1'b1 ;

sys_rst_n <= 1'b0 ;

#( CYCLE * 10 ) ;

sys_rst_n <= 1'b1 ;

#( 210 ) ;

sys_rst_n <= 1'b0 ;

#( 10 ) ;

#( CYCLE * 10 ) ;

sys_rst_n <= 1'b1 ;

#( CYCLE * 1000 ) ;

end

always #( CYCLE / 2 ) sys_clk = ~sys_clk ;

initial begin

$timeformat(-9,0,"ns",6) ;

/* (第一个位置)

-9 是10 的负9次方 表示纳秒

-3 表示毫秒

*/

/* (第二个位置)

0 表示,小数点后显示的位数

*/

/* (第三个位置)

“打印字符” 与单位相对应

*/

/* (第四个位置)

6 表示 打印的最小数字字符 是6个

*/

$monitor("@time %t:cnt_bit=%b,data=%b,ds=%b",$time,cnt_bit,data,ds) ; // 监测函数

end

endmodule

这篇文章描述了一个使用Verilog语言编写的系统,包含时钟信号处理、计数器、选择器和LED显示器模块。它详细展示了如何用参数化设计实现周期性操作和状态切换,以及监控计数和数据变化的过程。

这篇文章描述了一个使用Verilog语言编写的系统,包含时钟信号处理、计数器、选择器和LED显示器模块。它详细展示了如何用参数化设计实现周期性操作和状态切换,以及监控计数和数据变化的过程。

1523

1523

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?