Design source code :

// 4 - 2 priority encoder

// The priorities are in descending order :

// data_ina >> data_inb >> data_inc >> data_ind

// "data_out" is coded output.

// "s" is coded input or not.

module priority_encoder (

input wire data_ina ,

input wire data_inb ,

input wire data_inc ,

input wire data_ind ,

output wire [01:00] data_out ,

output wire s

);

assign { s, data_out } = ( data_ina == 1'b1 ) ? 3'b011 : ( data_inb == 1'b1 ) ? 3'b010 : ( data_inc == 1'b1 ) ? 3'b001 : ( data_ind == 1'b1 ) ? 3'b000 : 3'b100 ;

endmodule

testbench:

`timescale 1ns/1ns

module test();

reg data_ina ;

reg data_inb ;

reg data_inc ;

reg data_ind ;

wire [01:00] data_out ;

wire s ;

parameter CYCLE = 20 ;

priority_encoder priority_encoder_insert (

.data_ina ( data_ina ) ,

.data_inb ( data_inb ) ,

.data_inc ( data_inc ) ,

.data_ind ( data_ind ) ,

.data_out ( data_out ) ,

.s ( s )

);

initial begin

data_ina = 1'b0 ;

data_inb = 1'b0 ;

data_inc = 1'b0 ;

data_ind = 1'b0 ; // 初始化

data_ind = 1'b1 ;

#( CYCLE ) ;

data_inc = 1'b1 ;

#( CYCLE ) ;

data_inb = 1'b1 ;

#( CYCLE ) ;

data_ina = 1'b1 ;

#( CYCLE ) ;

data_ina = 1'b0 ;

#( CYCLE ) ;

$stop;

end

endmodule

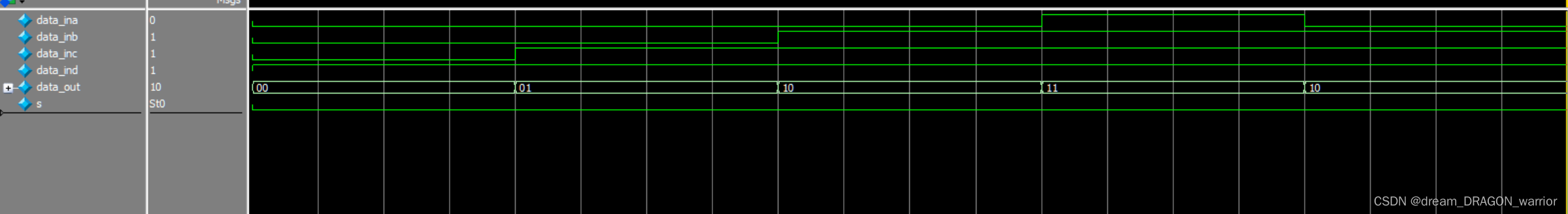

simulation waveform

The second way:

module priority_encoder (

input wire data_ina ,

input wire data_inb ,

input wire data_inc ,

input wire data_ind ,

output reg [01:00] data_out ,

output reg s

);

//assign { s, data_out } = ( data_ina == 1'b1 ) ? 3'b011 : ( data_inb == 1'b1 ) ? 3'b010 : ( data_inc == 1'b1 ) ? 3'b001 : ( data_ind == 1'b1 ) ? 3'b000 : 3'b100 ;

always @(*) begin

if( data_ina ) begin

{ s , data_out } = 3'b011 ;

end else begin

if( data_inb ) begin

{ s , data_out } = 3'b010 ;

end else begin

if( data_inc ) begin

{ s , data_out } = 3'b001 ;

end else begin

if( data_ind ) begin

{ s , data_out } = 3'b000 ;

end else begin

{ s , data_out } = 3'b100 ;

end

end

end

end

end

endmodule

本文介绍了一个优先级编码器的设计,使用Verilog语言实现,包括上升顺序的输入映射和两种不同的数据输出方式。测试bench用于验证模块功能,展示了如何在Verilog中使用assign和always@*语句进行编码逻辑的编程。

本文介绍了一个优先级编码器的设计,使用Verilog语言实现,包括上升顺序的输入映射和两种不同的数据输出方式。测试bench用于验证模块功能,展示了如何在Verilog中使用assign和always@*语句进行编码逻辑的编程。

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?