文章目录

本规范描述AUTOSAR基础软件模块内存访问(Memory Access, MemAcc)。

内存访问模块提供了通过基于地址的API对各种不同技术内存的访问。内存访问模块总是与一个或多个内存驱动搭配使用。内存访问模块是独立于内存设备技术的,可用于多种典型的内存访问,如flash,EEPROM,RAM或相变内存。

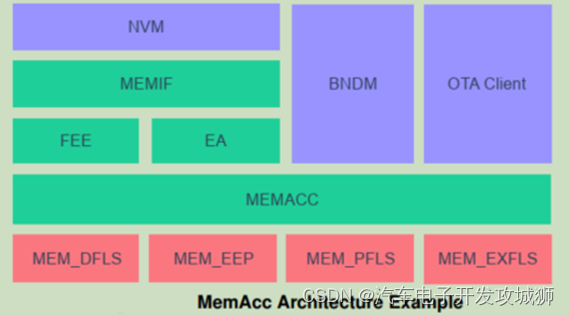

内存访问模块和内存驱动与Fls和Eep驱动在AUTOSAR架构中位于同一层,但这些模块拆分为独立于硬件的部分(MemAcc)和依赖于硬件的部分(Mem)。下图所示为不同内存驱动和上层的架构示例图。

MemAcc与Mem一起使用,支持如下用例:

- 基于块的非易失内存访问,使用NvM和Fee或Ea用于数据存储;

- OTA软件更新;

- 通常基于地址的内存访问,如用于BanM或bootloaer。

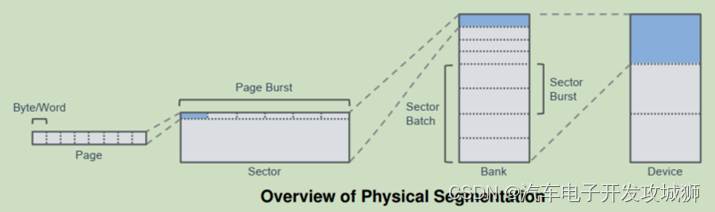

下图所示为物理分段示意图及相应技术术语。

BanM:Bulk Non-Volatile Data Manager,批量非易失性数据管理器;

Bank:一批扇区组成的组,在存储器被分割成扇区的技术情况下,一个bank就是一批扇区组成组的实例化,不允许边读边写操作。在闪存设备的情况下,这通常映

本文深入探讨了AUTOSAR基础软件模块内存访问(MemAcc),描述了其功能、关键特性、模块处理流程,以及内存访问协调、硬件特定服务等内容,强调了在共享内存资源访问控制和内存地址转换的重要性。

本文深入探讨了AUTOSAR基础软件模块内存访问(MemAcc),描述了其功能、关键特性、模块处理流程,以及内存访问协调、硬件特定服务等内容,强调了在共享内存资源访问控制和内存地址转换的重要性。

订阅专栏 解锁全文

订阅专栏 解锁全文

525

525

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?