关注、星标公众号,精彩内容每日送达

来源:网络素材ChipScope 功能与特性

许多硬件问题只有在整个集成系统实时运行的过程中才会显现出来。AMD Vivado™ ChipScope 提供了一套完整的调试流程,可在系统运行期间最大限度提升对可编程逻辑的观测能力,助力设计调试。

设计观测

可观测的内部节点数量增至数百个,设计的内部工作情况一目了然。

深入分析

实施复杂的触发条件并对设计进行多角度的深入分析。

快速调试迭代

利用增量编译流程加快迭代,并使用 Python™ 实现任务自动化。

AMD Vivado™ ChipScope Analyzer

本视频将为您提供关于如何实施和使用 ChipScope 进行硬件调试的实用概览。视频包含如下内容:将内部逻辑分析器和调试核集成到可编程逻辑、设置触发器,以及分析捕获的数据以快速识别和解决问题。

硬件调试分步操作教程

开发者技术分享:Adam Taylor 是嵌入式系统和 FPGA 的设计和开发专家,他针对 AMD Versal™ 和 UltraScale+™ 器件各编制了一套教程,通过这两套教程,可了解如何使用 Vivado ChipScope 在真实的系统中进行硬件调试。每套演示教程都着重介绍了调试方法,并展示了如何有效地检测设计,还包括多项可运行和探索的项目。

Versal:https://www.hackster.io/adam-taylor/using-chipscope-to-debug-amd-versal-designs-2a2fcd?auth_token=b0e9c443bc1db5f44de795fe1c195eeb

UltraScale+:https://www.hackster.io/adam-taylor/illuminating-vivado-chipscope-ilas-ultrascale-051e30?auth_token=bd1bcba0e28e2a6eab35c9605853dd2f

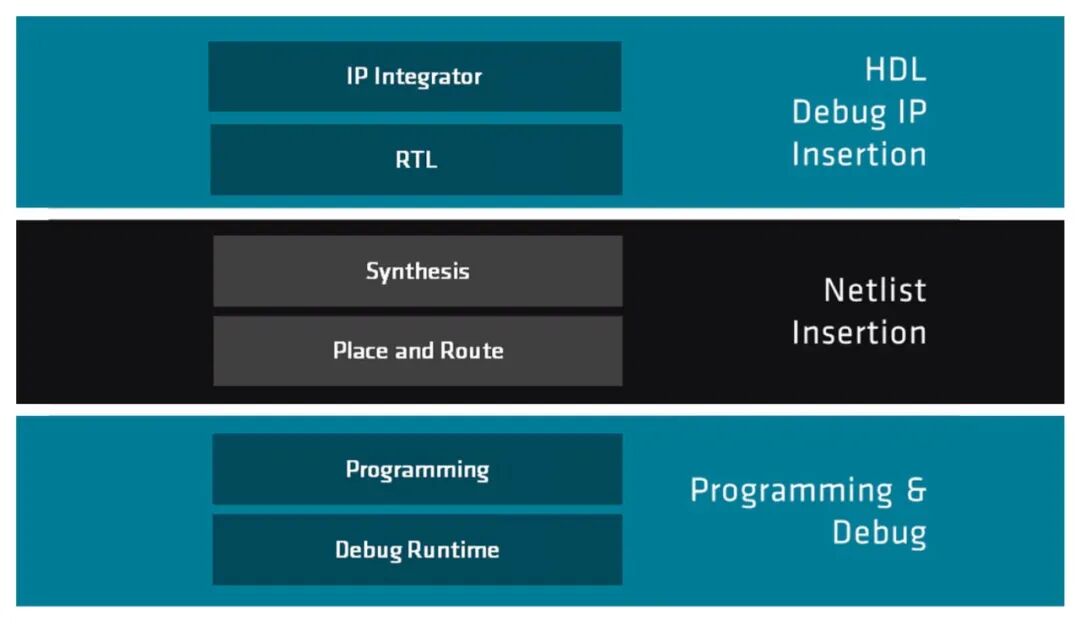

全面的调试流程

采用灵活的方法进行调试 IP 检测、设计分析和运行时配置,并通过增量编译加快调试迭代。

IP Integrator

IP 即插即用:从 IP 目录中选择 ILA,并通过用户界面配置信号探测器和数据捕获深度。

RTL

RTL 插入:自定义 ILA 模块的 HDL 源文件,已实现精准的信号探测。通过 IP Integrator 集成到顶层 RTL。

Synthesis

增量编译:综合后插入;在完成综合后标记要探测的信号,避免修改 HDL 设计和快速重新分配探测器。

Place and Route

ECO 流程:ECO 增量编译流程,在完成布局布线后重新分配信号探测器,充分保留以前的实现结果。

Programming

PDI 调试:用于识别和分析启动配置错误并提出修复建议的实用程序。

Debug Runtime

实时调试:监控信号、触发硬件事件,并以系统速度捕获时序精准的设计的相关数据。

(全文完)

声明:我们尊重原创,也注重分享;文字、图片版权归原作者所有。转载目的在于分享更多信息,不代表本号立场,如有侵犯您的权益请及时联系,我们将第一时间删除,谢谢!

想要了解FPGA吗?这里有实例分享,ZYNQ设计,关注我们的公众号,探索

4631

4631

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?