点击蓝字关注我们

关注、星标公众号,精彩内容每日送达

来源:网络素材标准单元是芯片中的基本概念,彻底改变了集成电路(IC)的设计和制造。这些模块化基本模块构成了高效和可扩展的芯片设计的基础,在灵活性和性能之间提供了理想的平衡。

通过使用预先设计和测试的组件,如逻辑门,设计师可以专注于更high level的设计,加快IC开发过程,同时保持性能的一致性。

芯片中的标准单元

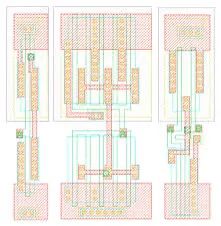

标准单元是预先设计和预先验证的功能块,这些功能块封装了特定的逻辑函数,如AND门、触发器或latch。这些单元布局布线在预定义的高度,无缝互连,允许创建复杂的数字电路。

标准单元的类型

1.基本结构

标准单元通常有一个固定的高度,允许它们在标准网格上对齐。该设计包括晶体管、互连和其他组件的预定义布局,以执行特定的逻辑功能。

2.标准单元的类型

时序单元:专为存储器元素(如触发器和latch)而设计,以存储信息。

组合单元:专注于执行特定的逻辑功能,如AND、OR和XOR门。

标准单元的优点

1.设计生产力

标准单元促进了模块化设计方法,通过实现预特征功能块的重复使用来提高设计生产力。

2.面积效率

它们一致的高度和模块化结构有助于有效利用芯片面积,优化整体布局并确保统一性。

3.性能优化

标准电池经过精心设计和性能K库,有助于可预测和可靠的电路行为。

标准单元库

标准单元库

标准单元库由预设计的标准单元组成,提供一系列功能和性能特征。

2.K库

每个标准单元都经过严格的表征,包括时序分析、功耗评估和其他关键参数。

VLSI设计中的物理实现

1.综合

综合工具将高级硬件描述HDL映射到标准单元的网表中,优化性能、功耗和面积。

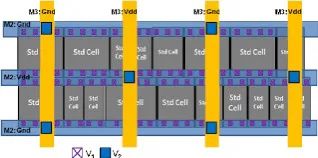

2.place和routing

在物理设计阶段,标准单元被放置在芯片的布局网格上,并相互连接以形成最终设计。

3.设计收敛

进行彻底的验证和时序分析,以确保设计符合规格并成功收敛。

结论

标准单元代表了芯片设计中的范式,为构建复杂数字电路提供了一种多功能和高效的方法。对于旨在创建高性能和可扩展的半导体器件的芯片工程师来说,了解标准单元的结构、优势和设计流程至关重要。

想要了解FPGA吗?这里有实例分享,ZYNQ设计,关注我们的公众号,探索

3031

3031

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?