点击蓝字关注我们

关注、星标公众号,精彩内容每日送达

来源:网络素材1. xdma IP核的功能

完成PC和FPGA通过pice接口的通信,主要是进行数据传输

读写部分分为两种,一种是数据的读写,另一种数配置数据的读写。在数据读写部分,DMA通过MIG控制DDR完成数据读写。配置数据读写通过与BRAM通过AXI-lite总线连接完成,XDMA将PCIe配置信息存在BRAM,在进行配置信息读写时,将传入主机映射到用户逻辑的地址,然后与偏移地址处理(物理地址=段地址<<4+偏移地址),所以在bram设置时需要将其偏移地址设置的与主机地址映射的偏移地址相同。

2. AXI总线传输模式

AXI4.0-lite是AXI4.0-full的简化版。用于简单、低吞吐量的内存映射通信。

由于没有突发传输相关的信号线,所以不能进行突发传输,因此每次传输只能传输一个数据(数据的宽度取决于带宽)。比如对于32位宽度的总线,那么一次就能传输4个字节。AXI4.0-full用于高性能内存映射需求。

包含突发控制信号,所以可以进行突发传输,在指定一次地址后,可以一次传输多达256个数据(数据的宽度取决于带宽)。AXI_stream用于高速流数据。由于没有地址总线,所以用于数据流传送,允许无限制的数据突发传输规模。

应用场景

AXI4.0-lite主要用于内核和外设寄存器之间的通信。AXI4.0-lite就特别合适。

AXI4.0-full主要用于往DDR或者OCM中写入大量数据时使用。

AXI_stream主要用于往FIFO等没有地址的数据缓冲区传送大量数据时使用

3. IP核配置

3.1 Basic

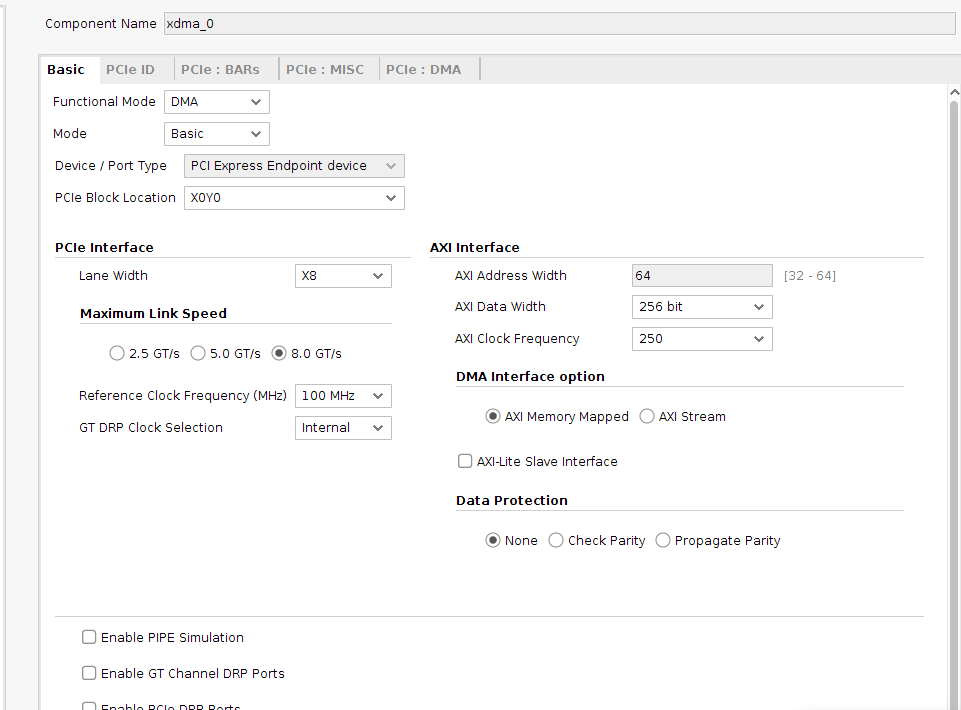

Functional mode:功能模式,即DMA模式。

Mode:模式,选择basic即可,basic与advanced的区别在于advanced模式开放更多的可选选项与功能,basic的话为默认。

Device/Port Type:选择设备与端口类型,为端点设备。

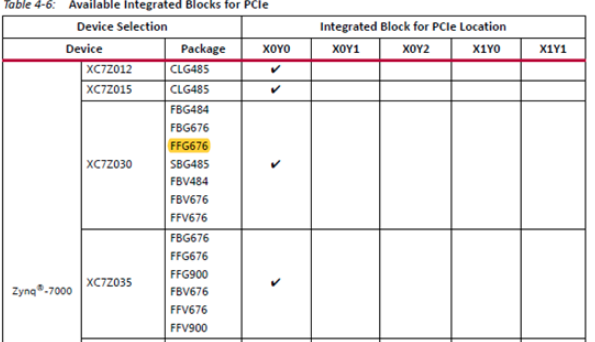

PCIe Block Location:从可用的集成块中选择,以启用生成特定位置的约束文件和输出。通过查找产品手册得到,通常使用X0Y0。

Lane width:通道宽度,根据接口进行选择。

AXI Address width:AXI地址宽度选择,只支持64bit(用户手册73页)。

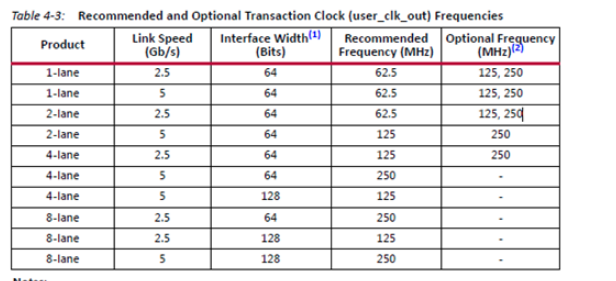

AXI Data Width:AXI总线上传输的数据宽度,可以是64bit、128bit、256bit、512bit(这个只有ultrascale+可以满足,一分钱一分货),根据datasheet进行配置即可P249

DMA Interface option:DMA的接口类型用于数据传输,有两种AXI MM(memory mapped)与AXI ST(stream),一般AXI MM用于和DDR之间的通信,AXI stream用于FIFO。

3.2 PCIe BARs:

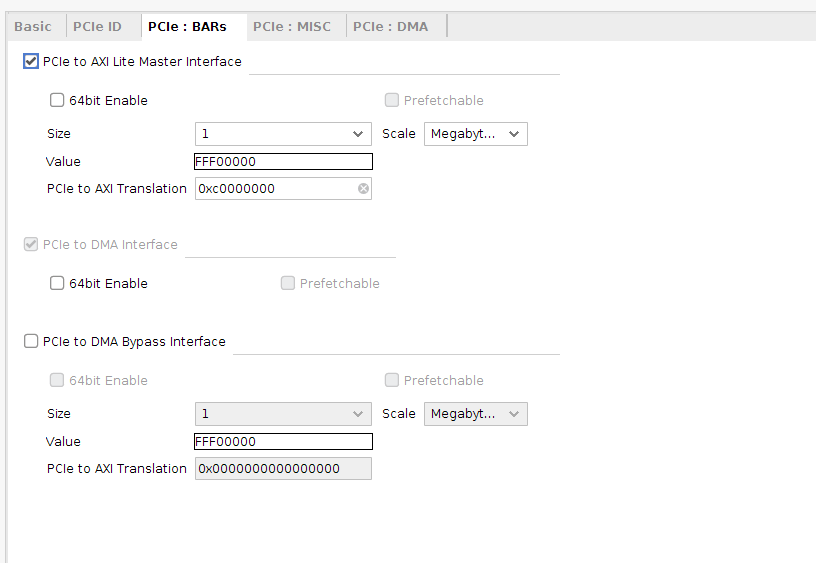

PCIe to AXI Lite Master Interface:使能,这样可以在主机一侧通过PCIe来访问用户逻辑侧寄存器或者其他AXI-Lite总线设备。

此处将配置信息存储到BRAM,通过AXI-lite总线读写Bram。

(1)BAR为32bit,不使能64bit,prefetchable表示预读取,不使能。

(2)映射空间选择1M,大小随意。

(3)PCIe to AXI Translation:主机侧BAR地址与用户逻辑侧地址不同,通过设置转换地址实现BAR地址到AXI地址的转换。比如主机一侧BAR地址为0,则主机访问BAR地址0转换到AXI-Lite总线就是0x8000_0000.

PCIe to DMA Interface:数据传输宽度64bit,DMA控制器一般只支持数据8字节对齐的情况。

当数据从上位机通过PCIe接口发送到端点设备,XDMA内部自行解包对将数据与指令进行分析,得到读写操作的指令地址,并对DDR进行读写操作。操作的结果通过AXI接口返回XDMA,XDMA对数据进行组包,之后通过物理层发出,实现数据的DMA控制。

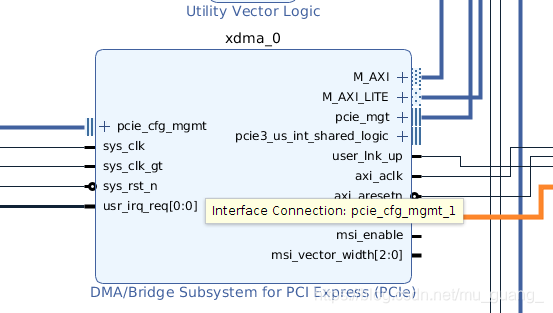

4. xdm连接

主要连接的部分就是M_AXI和M_AXI_LITE, 一般都连接在axi_interconnect中,然后M_AXI一般和DDR或者FIFO相连用于数据通信,M_AXI_LITE用于配置信息传输,用于访问用户逻辑侧寄存器。

5. 使用原理解析

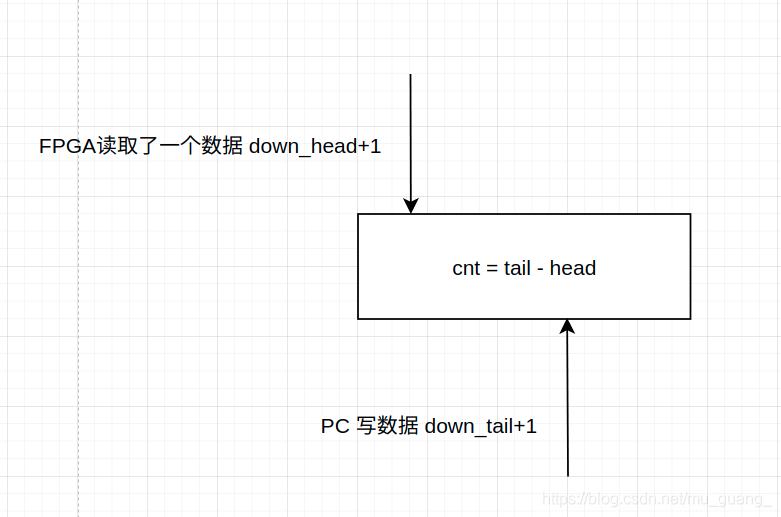

5.1 PC写数据

PC通过调用函数写数据, 更新dsTail, 并写到对应的寄存器中

writeReg相当于一条指令 down_tail+1,xdma会进行一个地址映射,我们在pc上对寄存器进行处理,会通过AXI_LITE总线传输,从而对目的地址上的数据进行加1。

控制模块queue对AXI_LITE数据解析,对down_tail进行+1

计算down_cnt, 从而控制AXI从DDR上对数据进行读取

AXI从DDR上读取数据之后,down_head+1, 然后反馈给控制模块queue, 计算down_cnt.

void updateDsTail(int pkgCnt)

{

for(; pkgCnt > 0; pkgCnt--)

{

dsTail += DS_PSIZE;

if(dsTail >= DS_ADDR_LIMIT)

dsTail = DS_BASE_ADDR;

}

writeReg(DS_TAIL_REG, dsTail);

}

5.2 PC读数据

PC读数据,对up_head寄存器进行+1

通过xdma对相关寄存器地址进行映射,并通过AXI-LITE总线对相应的地址进行写入数据

控制模块queue通过up_cnt = tail-head,计算up_cnt

up_cnt用于控制FPGA把数据写入DDR, up_cnt也就是一个满标志。

想要了解FPGA吗?这里有实例分享,ZYNQ设计,关注我们的公众号,探索

919

919

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?