时序式UDP 的输出reg端口初始值可通过initial语句指定,该语句提供了一个初始化过程赋值,且initial语句是可选的。module中的初始化语句也以关键字initial开头,但与UDP的过程赋值有一些区别,下表1列出了这两类初始语句的区别:

|

UDP中的初始语句 |

module中的初始语句 |

|

仅限于初始化1条过程赋值语句 |

可以是1条任何类型的过程语句,也可以是1条包含多条过程语句的块语句 |

|

过程赋值的reg信号为端口列表的输出信号 |

过程赋值语句的reg信号可以不是端口列表信号 |

|

过程赋值语句的赋值只能为:1'b1、1'b0、1'bx、1、0 |

过程赋值语句可赋值任意的位宽和数值大小 |

表1:UDP 和module初始语句对比

例 1:下面的示例为一个包含初始语句的时序式UDP:

primitive srff (q, s, r);

output q; reg q;

input s, r;

initial q = 1'b1;

table

// s r q q+

1 0 : ? : 1 ;

f 0 : 1 : - ;

0 r : ? : 0 ;

0 f : 0 : - ;

1 1 : ? : 0 ;

endtable

endprimitive

输出q在仿真开始时的初始值为1;对UDP例化的延迟指定不会延迟初始值分配给输出的时间;仿真启动时,该值就是状态表中的当前状态;UDP初始语句中不允许延迟指定。

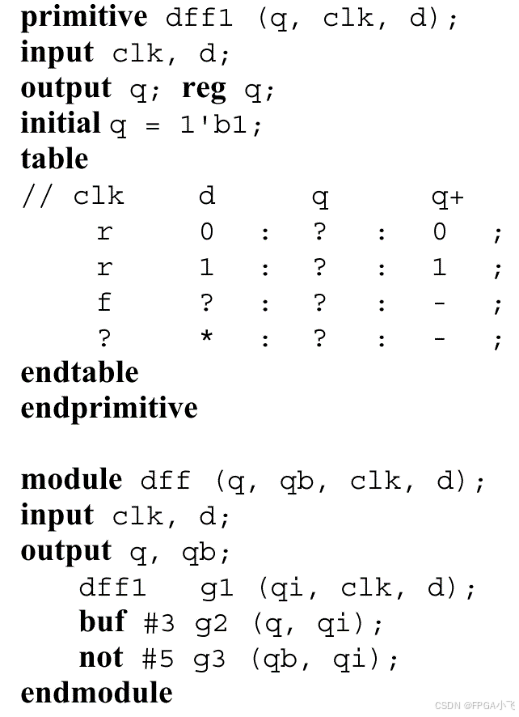

例2:下面的示例和图1展示了如何在模块module中使用初始语句例化时序式UDP:

UDP dff1 包含一条初始语句,将其输出的初始值设为 1。模块 dff 例化了一个 UDP dff1。

图1显示了上面的module原理图和仿真结果,UDP输出 qi 的扇出包括网络信号 q 和 qb。在仿真时间0时,qi的值变为1。qi 的初始值直到仿真时间3才传播到网络q,直到仿真时间5才传播到网络qb。

图1:module原理图和初始值传播仿真时间

点赞加关注博主(ID:FPGA小飞)的博文,咱们一起系统学习verilog最终标准IEEE Std 1364-2005吧!

589

589

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?