文章目录

-

- Verilog描述DFF

-

- 代码:

- 运行环境:

- 仿真图像:

- 对于always的用法:

“CK”为Flip-Flop(DFF)的时钟输入

Flip-Flop功能行为:在"CK"的上升沿把“D"端输入值锁存到”Q”端输出;

也有下降沿触发的DFF;

Verilog描述DFF

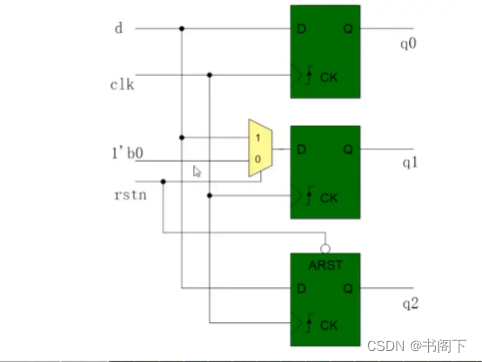

电路图:

代码:

module c_seq (

d ,

rstn ,

clk ,

q0 ,

q1 ,

q2

);

input wire d,rstn,clk;

output reg q0,q1,q2;//reg型变量除了描述寄存器还可以描述组合逻辑

//non-blocking assignment,非阻塞赋值

always @(posedge clk) //@括号里面为条件,上升沿

q0<=d;//当时钟为上升沿时执行

always @(posedge clk)

if (!rstn)

q1<=1'b0;//描述寄存器时用这种进行赋值

else

q1<=d;

always @(posedge clk or negedge rstn) //时钟的上升沿和rstn的下降沿

if (!rstn)

q2<=1'b0;

else

q2<=d;

endmodule

运行环境:

module tb_seq ();

reg clk,rstn;

reg d;

wire q0,q1,q2;//顶层的input能定义为wire型或者reg型,output只能定

文章详细介绍了如何使用Verilog语言描述DFF(D型触发器),包括上升沿和下降沿触发,并展示了always块中非阻塞赋值和阻塞赋值的使用。同时,提供了仿真环境的设置和仿真图像,帮助理解DFF在不同条件下的行为。

文章详细介绍了如何使用Verilog语言描述DFF(D型触发器),包括上升沿和下降沿触发,并展示了always块中非阻塞赋值和阻塞赋值的使用。同时,提供了仿真环境的设置和仿真图像,帮助理解DFF在不同条件下的行为。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1938

1938

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?