网络或变量的数组所声明的元素类型可以是标量或矢量。例如:

数组可用于将已声明元素类型的元素组合成多维对象。在声明数组时,应在声明的标识符后指定元素地址范围。每个维度应由一个地址范围表示。指定数组索引的表达式应为常整数表达式。常量表达式的值可以是正整数、负整数或零。

一条声明语句可同时用于声明数组和声明数据类型的元素。这种功能使得在同一条声明语句中同时声明数组和与元素矢量宽度相匹配的元素变得非常方便。

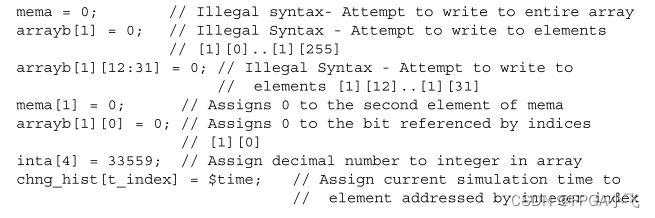

数组里的一个元素可以在一次赋值过程中赋值,但完整或部分数组不能。完整或部分数组维数也不能用于为表达式赋值。要为数组元素赋值,必须指定每个维度的索引。索引可以是一个表达式,该选项提供了一种机制,可根据电路中其他变量和网络的值引用不同的数组元素。例如,计数器reg值 可用来索引随机存取存储器(RAM)。

网络类型数组元素的使用方式与标量或矢量相同,它们可用于连接循环生成结构(高端操作,后文介绍)中模块实例的端口。

记住,所有变量类型(reg、integer、time、real、realtime)的数组也均可使用!

包含 reg 类型元素的一维数组也称为存储器。这些存储器可用于模拟只读存储器(ROM)、随机存取存储器(RAM)和reg 文件。数组中的每个 reg 都称为一个元素,并通过一个数组索引寻址。

一个n位reg可以通过一次赋值来赋值,但一个完整的存储器则不行。要为存储器赋值,必须指定一个索引,索引可以是一个表达式。该选项提供了一种机制,可根据电路中其他变量和网络的值,引用存储器中不同的元素。

下面举几个数组声明例子:

下面举几个数组赋值例子:

我们还要注意由n个1bit reg元素组成的存储器是不同于一个 n 位reg变量的,这两个是完全不同的概念:

![]()

点赞加关注博主(ID:FPGA小飞)的博文,咱们一起系统学习verilog最终标准IEEE Std 1364-2005吧!

Verilog HDL 数组详解

Verilog HDL 数组详解

1211

1211

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?