目录

1. 介绍

综合报告是 Vitis HLS 工具链中一个关键的输出,它为开发者提供了关于其 HLS 设计的重要信息,包括时序估计、性能和资源使用情况、硬件接口细节以及软件到硬件的映射信息。

本文通过三个简单的示例,详细解读这些报告,以便更好地理解 Vitis HLS 工具的输出,并利用这些信息来优化和调试硬件设计。

2. 示例一

2.1 HLS 代码

#include <ap_int.h>

void func(ap_fixed<1,1> *led_o, char reg_in)

{

if(reg_in == 'o')

*led_o = 1;

else

*led_o = 0;

}

这段代码的功能非常简单,根据输入字符(reg_in)来控制一个 LED 的开关状态。如果输入是'o',则 LED 打开;否则,LED 关闭。

func 函数接受两个参数:

- reg_in:一个 char 类型的变量,用来接收控制指令。

- led_o:一个 ap_fixed<1,1> 指针,用法见《Vitis HLS 学习笔记--数据类型(任意精度:ap_int.h / ap_fixed.h)1》。

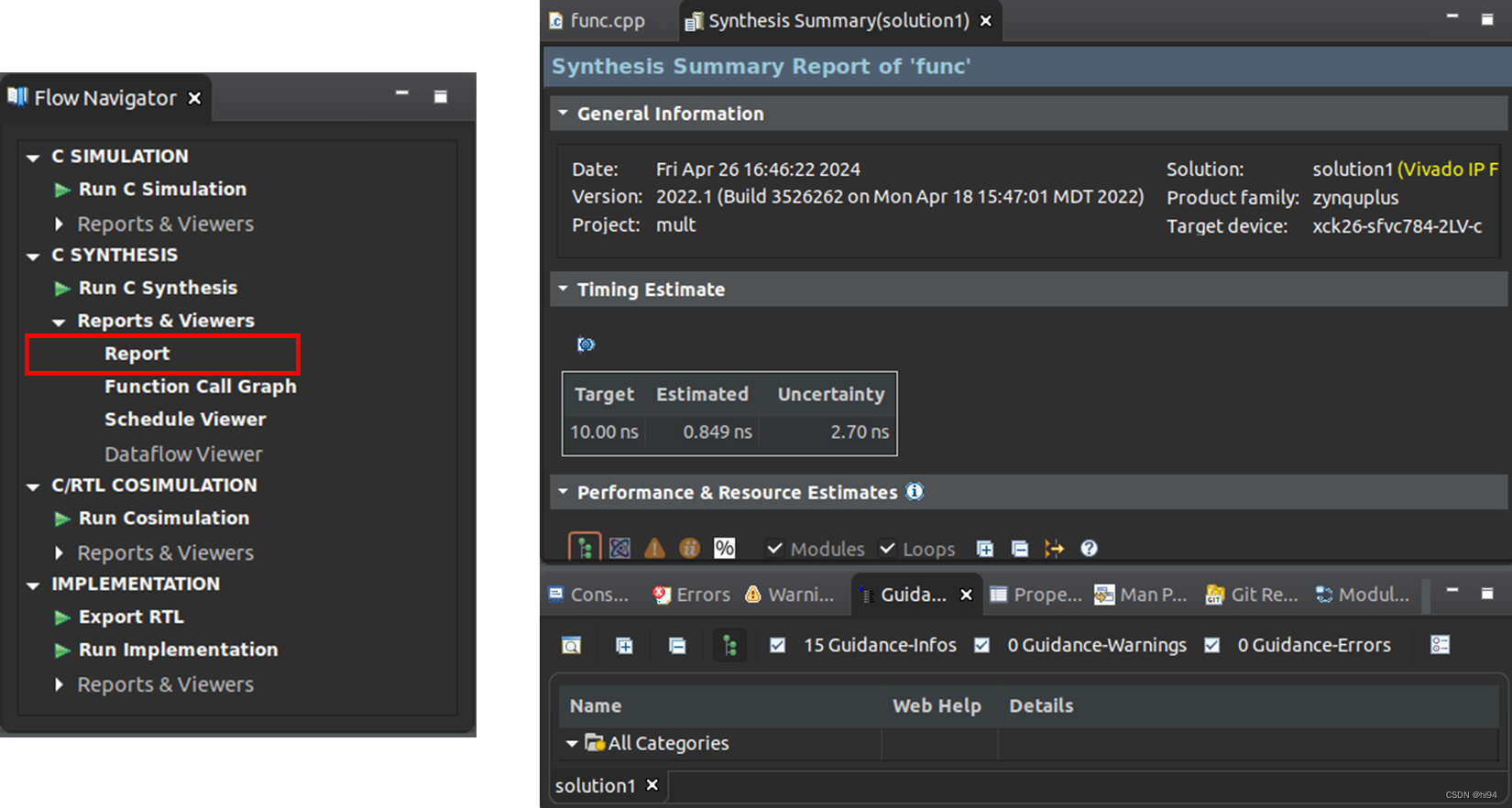

执行综合后,IDE 会自动打开报告,这里介绍两种进入报告的途径。

方法一,通过 Flow Navigator 打开 GUI 界面:

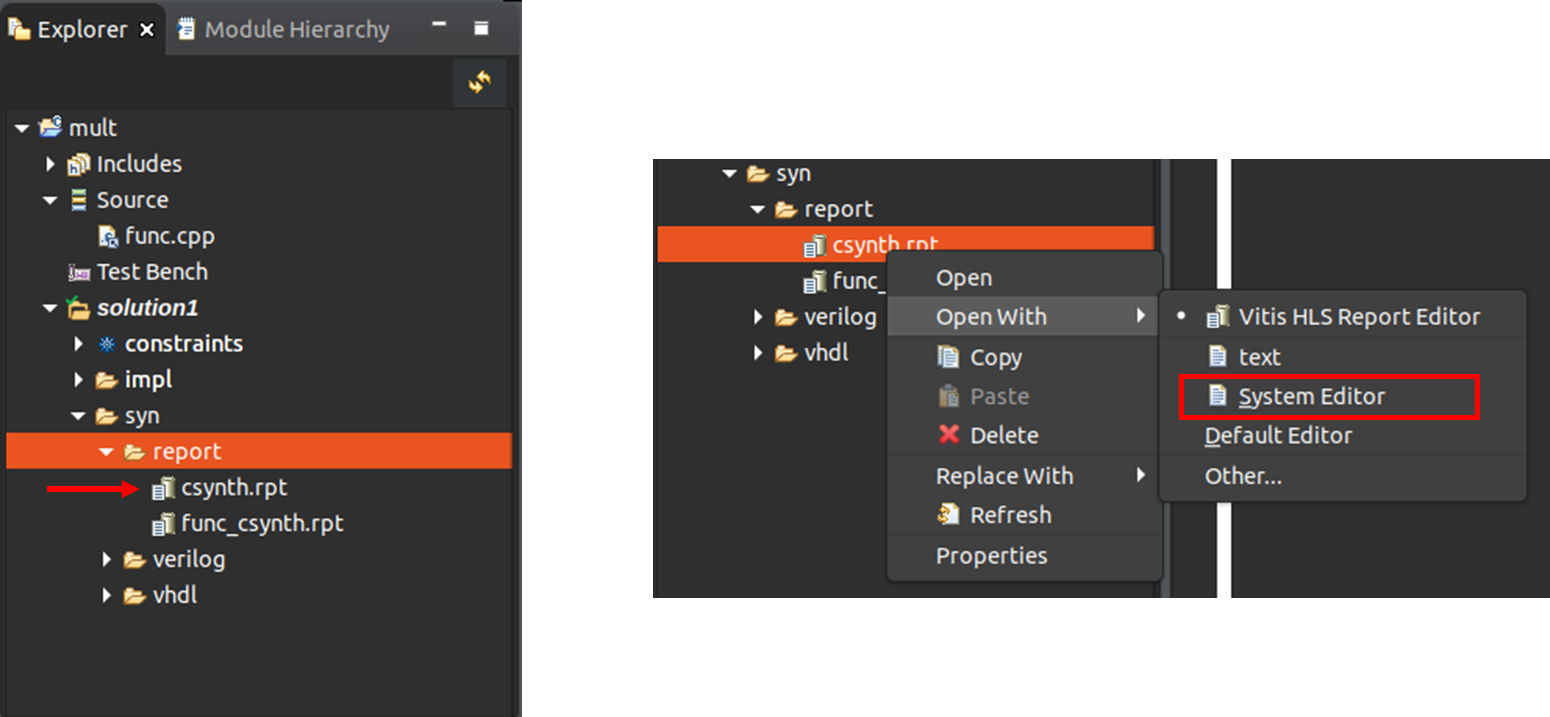

方法二,直接打开文本报告:

第二种方法可以打开文本的报告,比较方便复制。以下的内容从文本报告中复制。

2.2 Report 解读

2.2.1 时序估计

>> Timing Estimate

+ Timing:

* Summary:

+--------+----------+----------+------------+

| Clock | Target | Estimated| Uncertainty|

+--------+----------+----------+------------+

|ap_clk | 10.00 ns| 0.849 ns| 2.70 ns|

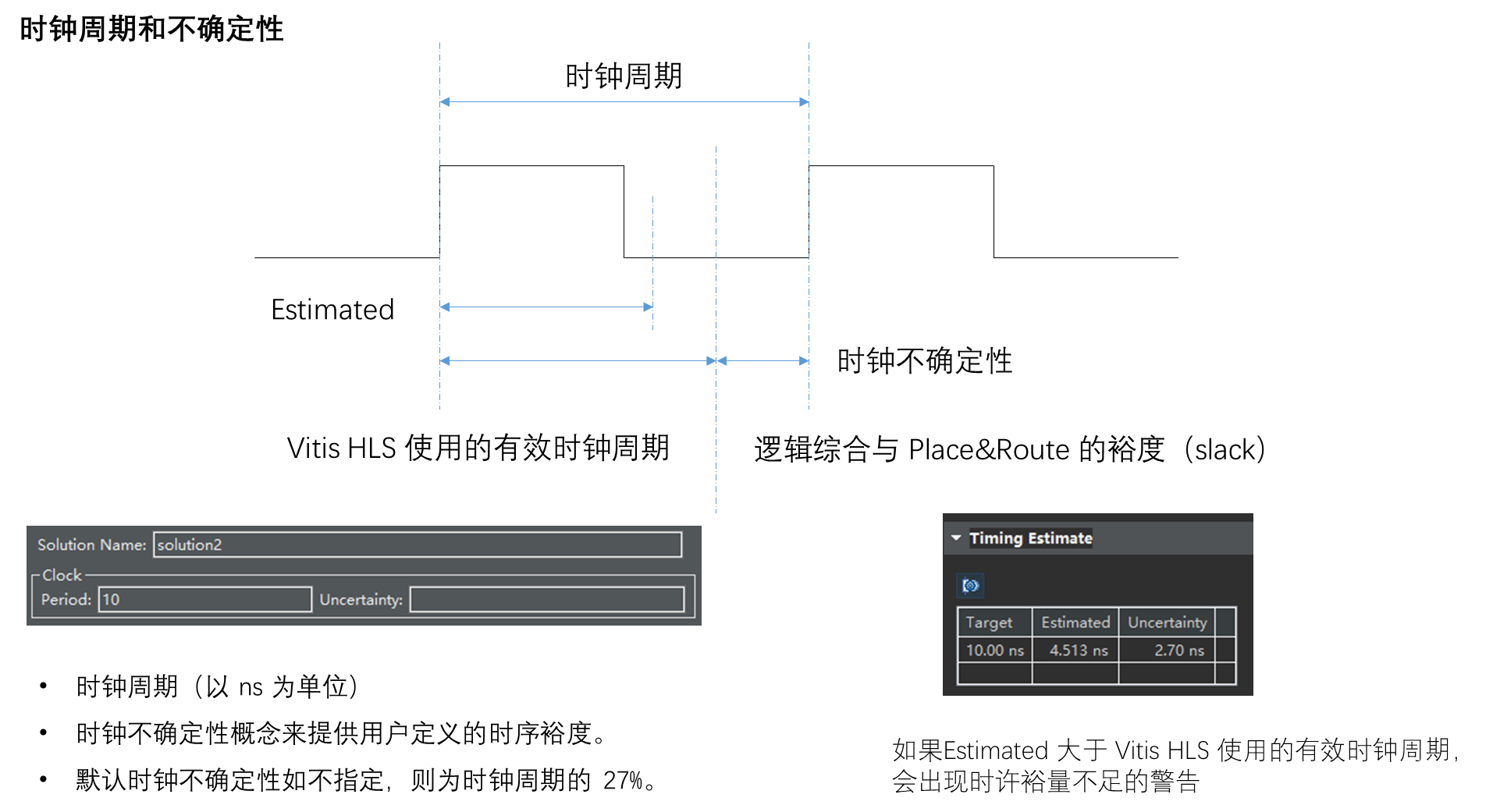

+--------+----------+----------+------------+关于 Uncertainty 的详细解释,我绘制下图方便理解:

其中,Vitis HLS 使用的有效时钟周期,可以理解为 Target 减去 Uncertainty。

2.2.2 性能和资源估计

>> Performance & Resource Estimates

+ Performance & Resource Estimates:

PS: '+' for module; 'o' for loop; '*' for dataflow

+--------+------+------+---------+--------+----------+---------+------+----------+------+----+---+----------+-----+

| Modules| Issue| | Latency | Latency| Iteration| | Trip | | | | | | |

| & Loops| Type | Slack| (cycles)| (ns) | Latency | Interval| Count| Pipelined| BRAM | DSP| FF| LUT | URAM|

+--------+------+------+---------+--------+----------+---------+------+----------+------+----+---+----------+-----+

|+ func | -| 6.45| 0| 0.000| -| 1| -| no| -| -| -| 11 (~0%)| -|

+--------+------+------+---------+--------+----------+---------+------+----------+------+----+---+----------+-----+2.2.3 HW interfaces

2.2.3.1 硬件接口报告

================================================================

== HW Interfaces

================================================================

* REGISTER

+-----------+---------+----------+

| Interface | Mode | Bitwidth |

+-----------+---------+----------+

| led_o | ap_none | 1 |

| reg_in | ap_none | 8 |

+-----------+---------+----------+

* TOP LEVEL CONTROL

+-----------+------------+-----------------------------------+

| Interface | Type | Ports |

+-----------+------------+-----------------------------------+

| ap_ctrl | ap_ctrl_hs | ap_done ap_idle ap_ready ap_start |

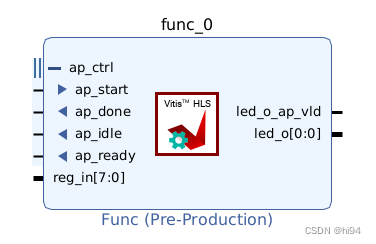

+-----------+------------+-----------------------------------+2.2.3.2 导出 Vivado IP

默认块级协议为 ap_ctrl_hs,故生成的 Vivado IP 包含 ap_ctrl 端口。

2.2.3.3 端口级协议

Port-Level Protocols,端口级协议,即 func 函数的参数:

- reg_in(标量类型),作为输入,默认是 ap_none 协议

- led_o(指针类型),作为输出,默认是 ap_vld 协议,故包含 led_o_ap_vld 信号

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2301

2301

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?