摘要:领域特定架构已成为计算机发展的一种趋势。在提供更高效算力的同时,它也给底层硬件的开发带来了更大的挑战。传统的芯片设计和验证技术已越来越无法应对这些新的要求和挑战。在芯片设计上,本文将介绍如何使用SpinalHDL,一种基于Scala的新型硬件描述语言(HDL),或者更准确地说是硬件构造语言,提高硬件设计的效率和质量。对于SpinalHDL,本文还介绍了如何利用Scala的类型系统高效地进行复杂硬件的设计。对于验证,本文将介绍基于Python的验证环境Cocotb,以及如何利用Python简洁高效的语言特性及其繁荣的开源社区,提升芯片验证的效率。

1. 引言

1.1 背景

近年来,计算需求不断演进并且多样化。就高性能计算而言,过去二十年间,互联网的迅速扩张产生了大量的数据,而深度学习等技术提供了许多有效利用这些数据的方法。然而,这些技术的实现对大规模高性能计算能力有着强烈的需求。例如,深度神经网络发展中的一个里程碑AlexNet的实现,很大程度上依赖于Nivida GPU的使用,后者为运行这一模型提供了足够的计算能力。与此同时,在工业应用中,提供节能型硬件以降低成本同时提供高计算能力也是相当重要的。在低功耗计算方面,随着物联网的快速发展,芯片的应用场景变得多样化,我们希望为每种场景选择最适合的芯片,这提出了多样化的芯片开发需求。

随着摩尔定律和丹纳德缩放的减速,简单地通过提高CPU或GPU性能来实现这种计算能力的增长已经不能满足需求。而且,简单地将低功耗CPU部署到边缘场景无法满足低功耗和定制功能的需求。因此,许多特定领域架构设计任务出现了,其中大部分呈现出软硬件协同设计的范式。硬件架构的研究和设计成为业界和学术界的热门话题,毫无疑问,当前正处于架构创新的黄金时代。这也是硬件描述语言(HDL)创新最好的时代,因为HDL是描述计算机架构最直接的方式,我们需要更高效的HDL来加快我们的架构设计实现。

与这些新兴的设计需求相比,目前业界主流的设计工具远远落后。Verilog和VHDL已经超过30年历史了,而SystemVerilog在设计方面只是对Verilog进行了一些小修改。与C等经典语言不同,Verilog/VHDL并没有通过多个版本的迭代演进,也没有发展大量的第三方库来补充语言,因此在很大程度上,我们使用Verilog/HDL时仍然像它们最初发布时一样。

1.2 HDL的演变

1.2.1 主流HDL的历史

传统HDL的历史可追溯到20世纪60年代,其中在20世纪80年代发布的Verilog和VHDL是最受欢迎的两种语言。Verilog和VHDL被认为是HDL的黄金标准,因为几乎所有电子设计自动化(EDA)工具都广泛支持它们。

最初,Verilog和VHDL用于记录和模拟以其他形式捕获和描述的电路设计,比如原理图文件。换句话说,它们并不是为了描述数字同步集成电路(IC)的RTL级模型而设计的。Verilog和VHDL的“读者”被认为是一个模拟器,而不是一个综合工具或工程师。在实践中,逻辑综合为HDL的引入将HDL从后台推到了数字硬件设计的前台,为此添加了“可综合”规则,但这些规则从未成为语言标准的一部分。

21世纪的第一个十年见证了SystemVerilog的出现,它是Verilog的超集。在验证方面,SystemVerilog借鉴了许多高级语言的特性,例如面向对象、更丰富的类型系统等。然而,在设计方面,它只是添加了一些功能,例如:• 增强的类型系统,包括枚举、联合等。• 带有接口的强度输入/输出描述。• 通过引入新的always comb、always ff和always -latch关键字,限制对敏感性列表的使用。

尽管如此,这些新引入的SystemVerilog设计功能直到现在也没有得到EDA供应商的全面支持,因此单独这些变化并不能使其具备处理复杂的软硬件协同设计任务的能力。

1.2.2 其他HDL的历史

与Verilog/VHDL不同,功能型HDL可以追溯到上世纪70年代,最早用于硬件形式化。众所周知,最早用于描述硬件的记号系统可以追溯到约翰·李的著作《计算机语义学》。与早期不同的是,自上世纪90年代以来,开发新的用于数字硬件设计的HDL有两个主要趋势:首先,鉴于Verilog和VHDL是主流EDA的事实标准,为了避免构建新的特定于某种语言的工具链,开发者选择首先生成Verilog/VHDL代码,然后使用生成的代码进行后续流程,包括综合和实现。在这种情况下,Verilog/VHDL的作用类似于汇编语言或新HDL与现有工具链之间的接口层。更精确地说,这些新的HDL,如Spinal、Chisel和Clash,通常被定义或称为HCL(HCL:Hardware Construction Language)。在本文中提到的HCL仍然是HDL的一部分,因为它们可以执行HDL的所有功能。这意味着单个HCL的内容必须是Verilog/VHDL核心部分的超集。

其次,与从头开始不同,大多数这些新的HDL都嵌入到流行的高级编程语言中,或更准确地说,它们可以被视为高级程序语言的库。因此,它们可以重用现有成熟语言的基础设施,包括它们的编译器、测试系统、包管理系统、IDE(IDE:集成开发环境),以及最重要的是它们的社区。这种策略降低了学习的难度,并使这些新的HDL非常可扩展。例如,Lava(及其方言)和Clash嵌入到Haskell中,Chisel和SpinalHDL嵌入到Scala中,MyHDL嵌入到Python中。

2. SpinalHDL

2.1 SpinalHDL简介

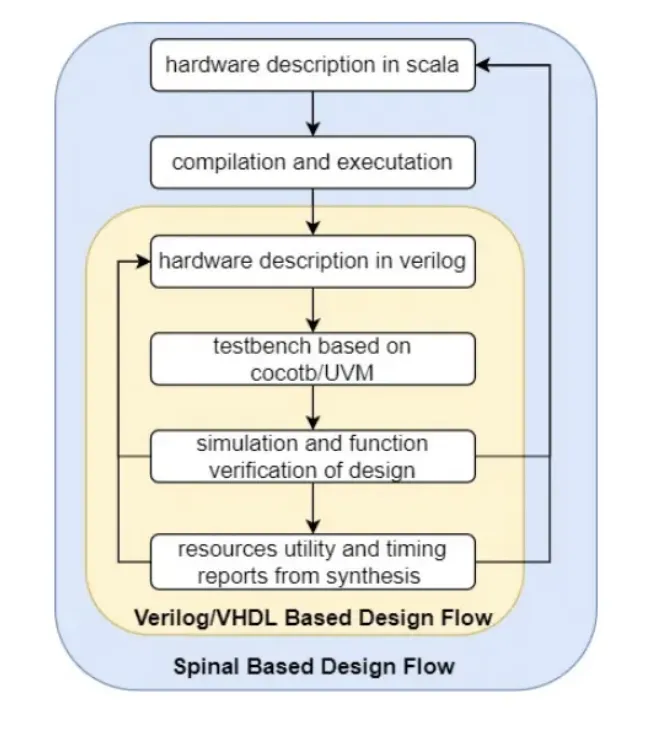

正如上面提到的,SpinalHDL[3]是基于Scala的HCL,或更准确地说,是Scala中的一个包,专用于数字芯片设计。与Chisel类似,SpinalHDL也是基于Scala的,并且主要用于RISC-V CPU设计。在Spinal中设计硬件的过程主要可以分为三个步骤:1)使用Scala和SpinalHDL包来描述硬件设计的结构和逻辑;2)编译和执行Scala程序,生成对应的SystemVerilog/VHDL代码,该代码与Scala代码描述的结构相同;3)使用任何类型的模拟器,如Iverilog、Verilator或Synopsys VCS,进行硬件模拟和验证。SpinalHDL基于传统的Verilog或VHDL进行硬件设计过程。Scala程序不能直接用于硬件模拟,而是需要首先执行以生成Verilog或VHDL代码,这意味着现有丰富的基于Verilog的设计工具链,包括模拟器、综合器和FPGA开发套件,可以在整个设计过程中使用。

图1:基于SpinalHDL的设计流程

2.2 与传统HDL相同的描述粒度

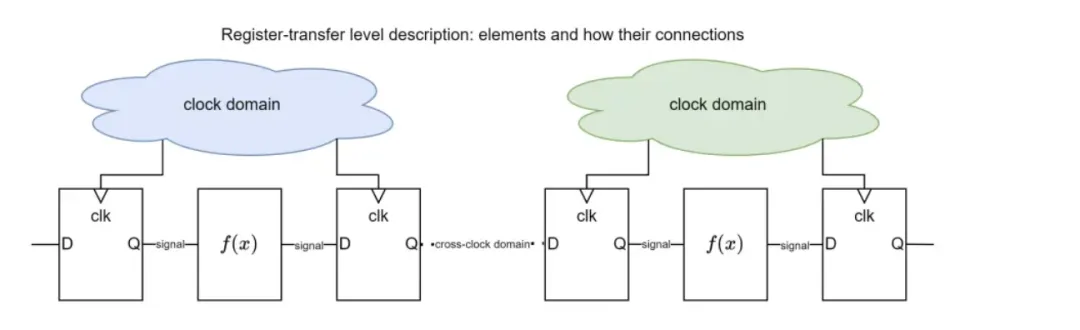

与软件开发相比,SpinalHDL对于以Verilog为代表的传统HDL来说就像Java、C/C++和Python等高级编程语言对汇编语言的作用一样。显然,高级语言比汇编语言更具表达力和生产力,并大大降低了开发复杂软件系统(如操作系统)的难度。尽管高级编程语言提高了软件开发的效率,但与汇编语言相比,程序的性能也受到了很大的牺牲。类似地,与传统HDL相比,SpinalHDL具有各种优势,并提高了设计数字硬件的效率。然而,与高级语言不同的是,它不会牺牲生成的硬件的性能和资源利用率,而是简化和加速设计过程。SpinalHDL与传统HDL(如Verilog或VHDL)几乎具有相同的描述精度或粒度。它可以精细控制寄存器的数量和寄存器之间的逻辑路径的长度。关于近似描述粒度的最佳证明是,对于Verilog/VHDL中的所有RTL级语法元素,SpinalHDL都有对应的对应元素。为了明确起见,我们在图2中显示了RTL级描述的所有基本元素,并在表1中列出了从SpinalHDL到Verilog的映射。如图2所示,RTL级描述是具有一个或多个时钟域的同步数字系统的形式化定义,基本上由以下五个部分组成:• 时钟域。• 组合部分在图2中表示为f(x)。• 顺序部分,通常是寄存器和存储器,在图2中表示为DFF。• 信号和连接,在图1中块之间表示为线(信号)。• 输入/输出(接口)。

图2:RTL级别描述中的元素。

对于这五个部分中的每一个,SpinalHDL提供了完整的相同描述能力,列在表1中。对于最坏情况,尤其是对于初学者来说,您可以使用SpinalHDL作为带有不同关键字集的Verilog/VHDL。因此,对于因语义失真而导致性能损失的担忧是不必要的。

表1:从SpinalHDL到Verilog的映射。

2.3 SpinalHDL相比传统HDL的优势

2.3.1 可靠性

使用SpinalHDL可以大大提高程序的可靠性,减少错误的可能性,从而减

SpinalHDL与Cocotb助力数字芯片设计验证

SpinalHDL与Cocotb助力数字芯片设计验证

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1537

1537

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?