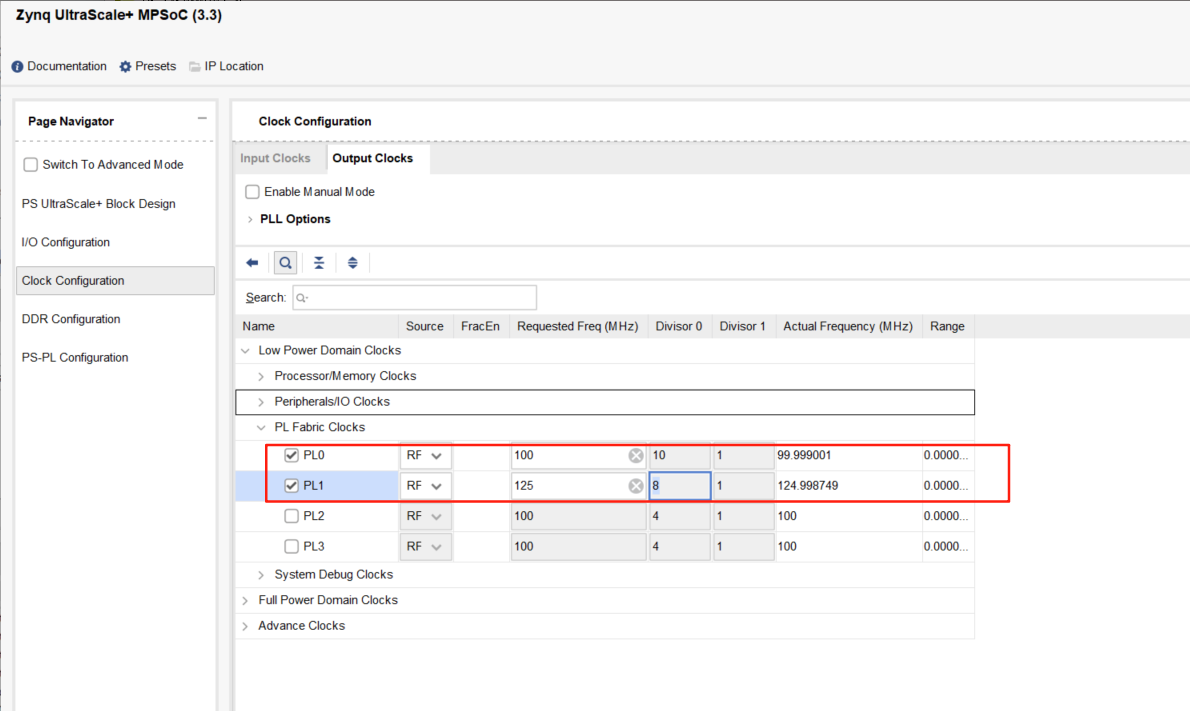

1、最近我在使用PL搭建RGMII 的工程的时候,打算使用PS引出的时钟的时候发现了PS的参考时钟为33.33333Mhz但是通过锁相环出来的100Mhz时钟实际只有:99.99999Mhz

以及需要的125Mhz实际只能到:124.998750Mhz

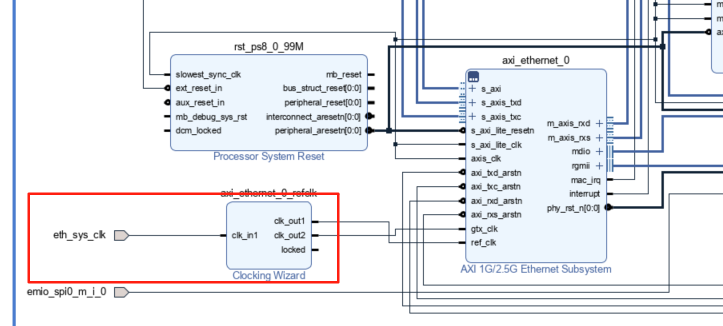

: [BD 41-238] Port/Pin property FREQ_HZ does not match between /axi_ethernet_0/gtx_clk(125000000) and /axi_ethernet_0_refclk/clk_out2(124998750)

2、当前我的解决办法是使用FPGA自己的系统时钟:

至于为什么没办法输出整数时钟可能还需要去查看PLL 锁相环的设计

3576

3576

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?