LMH0341接收SDI视频并转化为BT1120

1.概述

LMH0341解串器是TI FPGA-Attach SER /DES产品系列的一部分,支持将SDI视频解码为5位LVDS,可以和带LVDS的FPGA直接相连接。当与主机FPGA配对时,LMH0341会自动检测输入数据速率,并解码符合SMPTE-292M标准的数据。LMH0341的特性如下:

- 5位LVDS接口;

- 无需外部VCO或时钟;

- 带SDI环路输出端;

- 3.3V SMBus配置接口;

- 小型48引脚WQFN封装;

- 温度范围:-40℃至+85℃

LMH0341相比于其他SDI芯片,具有体积小,硬件接线简单的特点,可以满足小型化产品的设计要求。但芯片目前可参考的设计实例不多,本文在旨在将自己前期的工作做一个小总结,给各位提供一个设计参考。

2.硬件设计

其中信号SMB_CS,SDK和SDA是IIC总线,用于上层系统对LMH0341内部寄存器的配置和状态的读取。

DVB_ASI信号是DVB_ASI模式的选择,在使用在接收SDI信号的时候,该信号直接置零即可

RESET是复位信号,低电平有效

RX_MUX_SEL信号用于选择输入的通路,LMH0341可以实现两路SDI二选一的输入,RX_MUX_SEL=0用于选通RXIN0路,RX_MUX_SEL=1用于的选通RXIN1路;

LOCK为锁定信号,检测锁定到SDI信号时,输出低电平;

LOOP_EN用于使能自环输出,当LOOP_EN=1的时候,TXOUT可以环路输出输入的SDI视频

GPIO为LMH0341的通用输入输出接口,可以通过SMBUS写寄存器进行配置

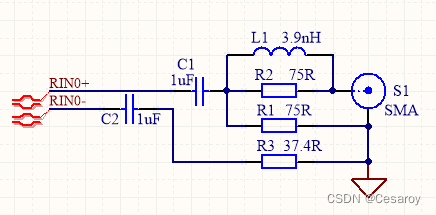

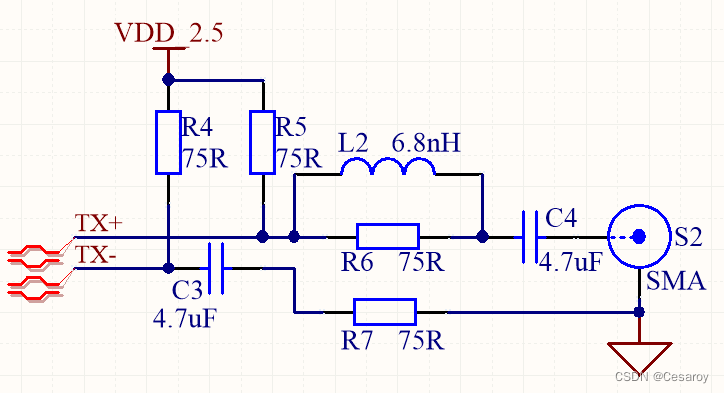

以上两个电路是SDI接收和发送的调理电路,经实测,可以和LMH0341直接相连。输入输出1080p/25Hz的视频没有问题,但是如果要输入输出帧频高于1080p/25Hz的视频,需要中间加一个自适应电缆均衡器,如LMH0344。LMH0344和LMH0341之间连线关系可以参考LMH0344数据手册中的典型电路。

L1和L2需要采用高频电感,可选用为LQP18MN3N9和LQP18MN6N8,其他元件用无高频要求。

3.软件设计

本设计直接将LMH0341直接和FPGA中具有LVDS特性的引脚相连,由FPGA解析出SDI视频的数据。

LMH0341在以时钟边沿为触发信号,包括上升沿和下降沿,每个边沿输出5位宽的数据,依据SMPTE-292m的标准,一个像素有20个字节,分为低十位和高十位,低十位为U/V分量,高十位为Y分量。输入视频为1080p/25Hz时,LMH0341的RXCLK 输出的频率148.5MHz。输入视频的像素时钟为74.25MHz,将RXCLK 通过PLL分频得到像素时钟,同时输出RXCLK的同相及反相信号,在信号的边沿对数据进行采样。程序如下:

always @(posedge clk_in1) begin

rev11 <= data_in;

rev12 <= rev11;

end

always @(posedge clk_in1_rev) begin

rev21 <= data_in;

rev22 <= rev21;

end

always @(posedge clk_out_div2) begin

rev_dat<= {rev21, rev11, rev22, rev12};

end

clk_in1就LMH0341输出的时钟;

clk_in1_rev是clk_in1的反相信号;

clk_out_div2是clk_in1的2分频信号;

rev_dat就是一个像素的数据

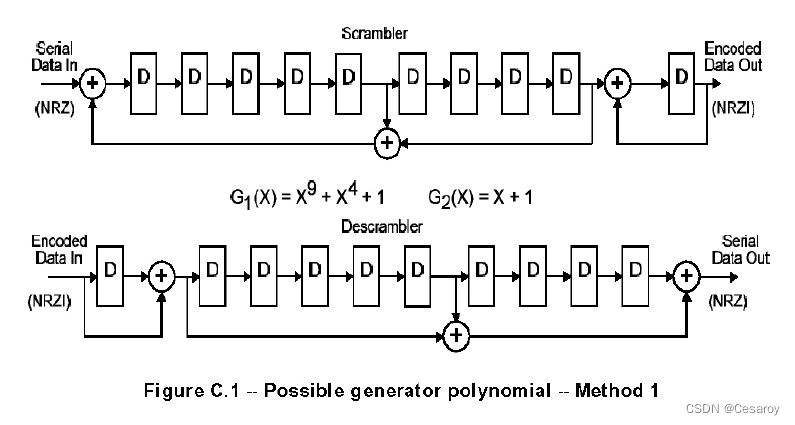

到此为止,程序已经可以将LMH0341输出的串行信号采集并合成了一个20Bit的数据,该数据为图像一个像素的数据。但是这个数据并不是以BT1120数据格式呈现,因为该数据经过了NRZI(Non-Return to Zero Inverted)的编码,还需要进行相应的解码才能得出符合BT1120格式的数据。

这里可以使用TI官方提供的参考程序SDALTIP-1.0,利用模块Descrambler可以将数据解码成BT1120格式。

module Descrambler (

input wire rstN, // System reset

input wire clk, // Input video clock at 74.25MHz nominal

input wire clken, // Clock enable for standard-definition

input wire [2: 0] clkfrq, // Detected input clock frequency

input wire [19: 0] i, // Scrambled video input from LVDS I/F

output reg [2: 0] trs, // Input TRS signals

output wire present, // Valid signal present

output reg [19: 0] vout // Descrambled input video

);

rstN是系统复位信号,clk是像素时钟,clken是时钟的使能信号,在这里可以置一个常值,使其处于一直使能的状态

clkfrq视频信号格式的说明码,1080p/25Hz对应的是b010,相关资料在SDALTIP-1.0源文件中可以查到

i是已编码的数据

输出数据trs在本设计中没有使用,可以悬空,vout是解码后的数据,present用于指示有一帧有效信号;

在像素时钟下,读取vout的数据,这就是符合BT1120格式的图像数据。后面可根据SMPTE-292M定义的BT1120格式对图像的有效数据进行解析,并进行后续处理。

下面两个文件是采用上述方法,利用Vivado的逻辑分析仪ila抓取的数据。

https://download.youkuaiyun.com/download/Cesaroy/87240373

本文介绍了如何使用TI的LMH0341解串器从SDI视频信号中接收数据并转化为BT1120格式。内容涵盖LMH0341的特性、硬件设计(包括关键信号的描述)以及软件设计,涉及FPGA解析SDI视频数据和NRZI解码。提供了基于SDALTIP-1.0的解码方案。

本文介绍了如何使用TI的LMH0341解串器从SDI视频信号中接收数据并转化为BT1120格式。内容涵盖LMH0341的特性、硬件设计(包括关键信号的描述)以及软件设计,涉及FPGA解析SDI视频数据和NRZI解码。提供了基于SDALTIP-1.0的解码方案。

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?