高速串行通信经常需要用到 XILINX FPGA 内部专用的 SERDESE 模块来实现串并转换。 LVDS 配合 SERDESE可以充分发挥 FPGA 的高速接口优势。 SERDESE 分输入和输出,输入采用 ISERDESE, 输出采用 OSERDESE,OSERDESE 的使用要比 ISERDESE 简单。

本文涉及到一些重要原语概念,包括 idelay 延迟原语,IDELAYCTRL原语, ISERDESE 、OSERDESE。其中很关键一点时使用 idelay 延迟模块以及 ISERDESE 原语中 BITSLIP 功能,实现比特流的时钟对齐,以及数据流的位流顺序对齐。XILINX FPGA 高速通信中经常会用到 idelay模块对信号比特流做细微的时序调整。

参考文档包括:官方手册ug471,xapp585,第三方米联客教程。

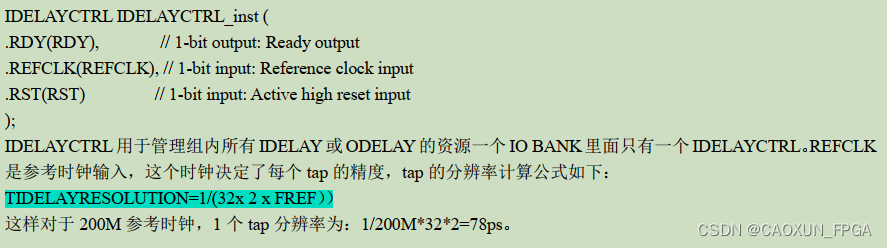

1、IDELAYCTRL模块

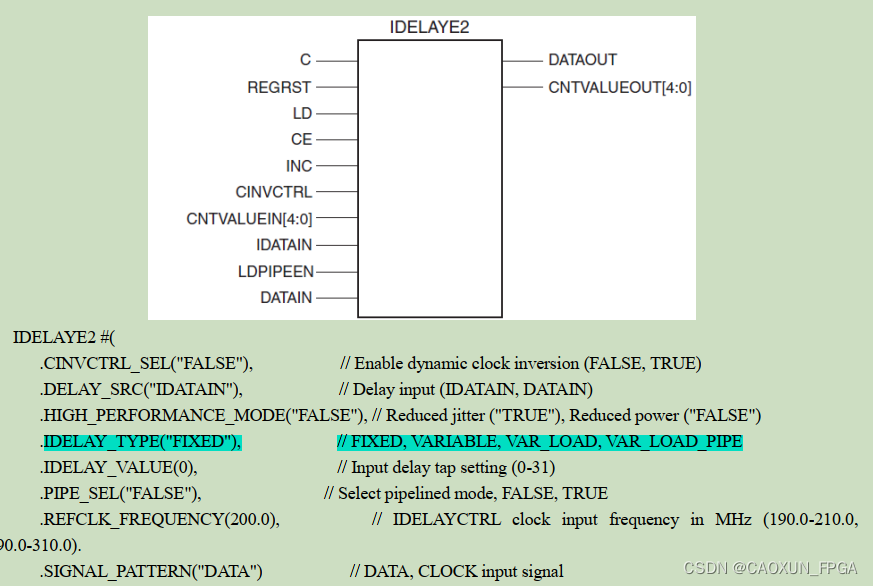

2、IDELAY模块

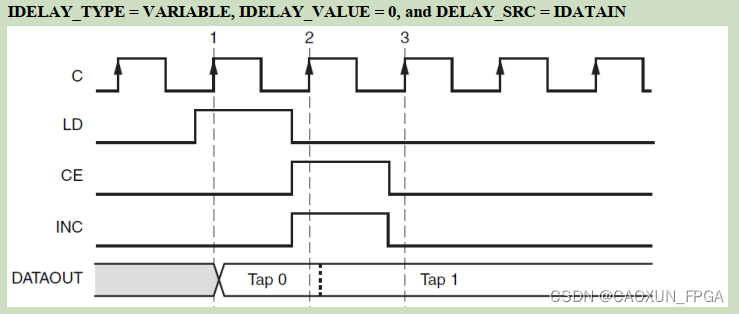

3、IDELAY模块工作时序

本文介绍Xilinx FPGA中SERDES模块的应用,包括OSERDES和ISERDES的工作原理,IDELAY与BITSLIP的功能,以及实现高速串行通信的时钟恢复和数据对齐的具体方法。

本文介绍Xilinx FPGA中SERDES模块的应用,包括OSERDES和ISERDES的工作原理,IDELAY与BITSLIP的功能,以及实现高速串行通信的时钟恢复和数据对齐的具体方法。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2万+

2万+