Q值有很多不同的定义,可以理解为电磁波在一个电路或结构中转了多少圈,能量就消失了(包括热损耗和漏波损耗造成能量损失)。

也可以用中心频率比带宽,储能比耗能,复本征频率实部比虚部等方法定义。

对于电感的Q值,越大代表L的等效电阻越小,所以Q值越高越好;

对于谐振电路的Q值而言,用途不同的谐振电路,Q值不同,不是越大越好,合适就好;

电学里,诸如分贝,Q值这些概念都让人犯蒙,这很正常,你不犯蒙才不正常。因为这其中任何一词都不只代表了一个意思,更不是在一个地方用的。

仅就品质因数Q来说,高频电路领域至少有三个公式常用到。

公式一是说电感的品质因数。

![]()

这里面的 ω是角频率,L 是电感量。一般情况下, ω和 L 都是我们已经选好的,能变的就是电感的损耗,即等效电阻R。所以等效电阻R越小,电感的品质因数Q就越高。

后两种Q值,则是说谐振电路的品质因数

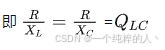

其中公式二,是从阻抗角度定义谐振电路的品质因数,等于【谐振电路的非谐振状态下的等效电阻值】,除以【谐振状态下的容抗值或感抗值】

★ 你注意到了吗?这个电路里,虽然Q还是Q,还是代表电路的品质;R也还是

订阅专栏 解锁全文

订阅专栏 解锁全文

2236

2236

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?