目录

一、前言

在时序分析中,不得不提的两个词,建立时间setup分析和保持时间hold分析,两者的定义如下

建立时间:触发器如果要正确捕获数据信号,数据信号必须在时钟信号到达前保持稳定的最小时间,即建立时间

保持时间:触发器如果要正确捕获数据信号,数据信号必须在时钟信号到达后保持稳定的最小时间,即保持时间

只有数据信号和时钟信号间的关系满足建立时间和保持时间时,数据才能正确地从触发器的Q端口输出

二、触发器的内部结构

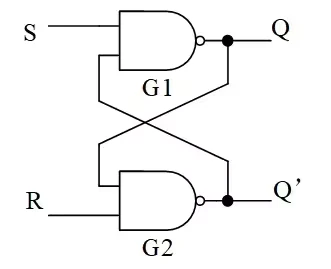

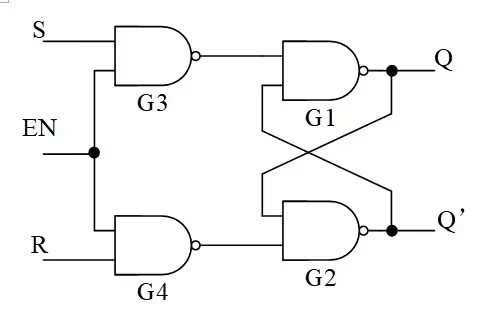

2.1 SR触发器

SR触发器有两个与非门组成,同时存在输出连接到输入的反馈电路。

SR触发器逻辑真值表如下图,Q0为Q的上一个变化输出,Q0'为Q'的上一个变化输出,正常情况Q和Q'应该值相反,一个为0,另一个为1。

1)R和S都为0时,则Q和Q’输出都为1,该状态属于非正常状态

2)R为0,S为1,则Q为0,Q'为1,SR锁存器为复位状态

3)R为1,S为0,则Q为1,Q'为0,SR锁存器为置位状态

4)R为1,S为1,则Q和Q'维持上一个时钟的状态,即输出不会变化,称为保持状态

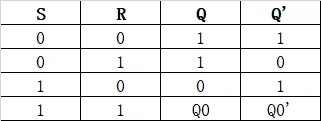

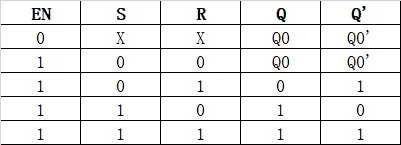

2.2 SR锁存器

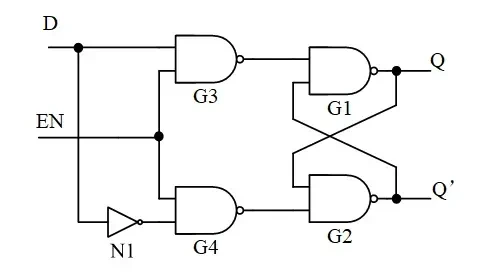

SR锁存器相比SR触发器,前面增加了两个与非门,同时增加了控制信号EN,只有控制信号EN为1时,才能有效进行锁存状态。

SR锁存器逻辑真值表如下图

1)当EN为0时,R和S的输入不会传到后一级的SR触发器,Q和Q'的输出保持之前的状态

2)当EN为1时,R和S的输入与输出Q和Q'的关系类似SR触发器

2.3 D锁存器

根据前面的SR触发器和SR锁存器的逻辑值可知,当出现S和R输入都为1时,Q和Q'的输出一致,这种情况不是设计想要的,因此就出现S和R来自同一个输入,当其中一路连接一个反相器进行取反的逻辑,即保证R和S的输入值相反。

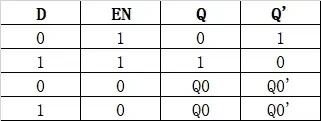

D锁存器逻辑真值表如下图

1)EN为1时,使能控制有效,输出Q等于输入D,也即将输出数据D锁住

2)EN为0时,使能控制无效,不管输入D为何值,输出都是保持之前的状态

2.4 D触发器

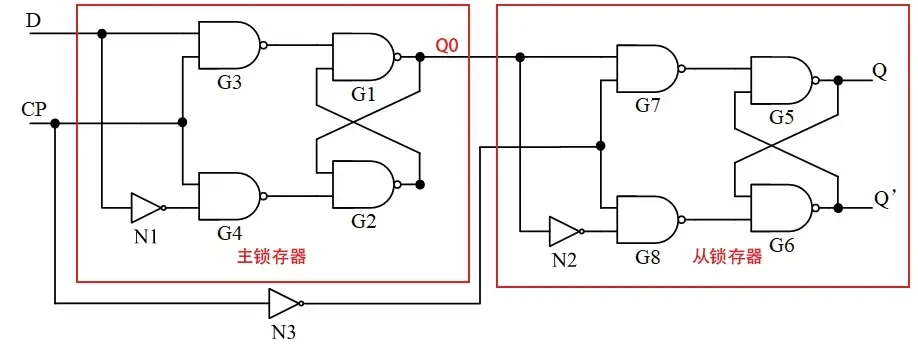

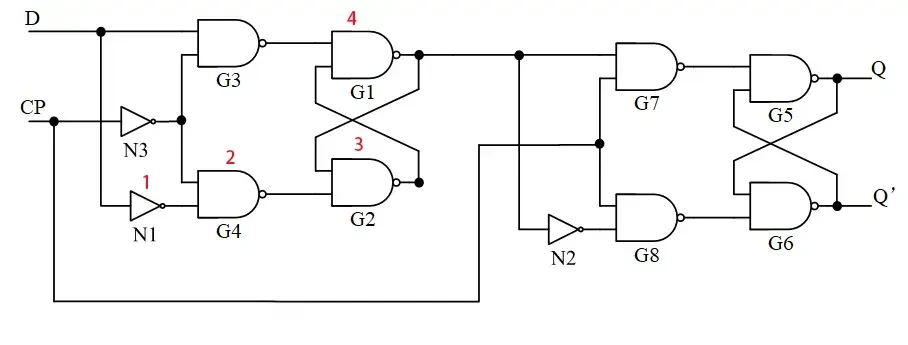

D触发器可由两个D锁存器加一个取反单元构成,前面的D锁存器为主锁存器,后面的为从锁存器,两者的控制信号CP同一时刻时相反的,下图是一个下降沿触发的D触发器内部结构。

1)CP为1时,主锁存器的输出Q0等于输入D,但从锁存器的控制信号因非门N3的存在,控制信号值为0,因此Q和Q’都维持上一个时刻的值。

2)CP为0时,主锁存器的输出的输出Q0维持上一个输入D值,同时从锁存器的输出Q等于Q0,也即Q0

3)结合上述的1和2,CP为1时D传输到Q0,CP变为0时,D可以从主锁存器传输到从锁存器的输出Q。整个流程看,即CP从1变为0时(即CP信号的下降沿),数据D可以传输到Q端口,上述电路图即为一个下降沿触发的D触发器。

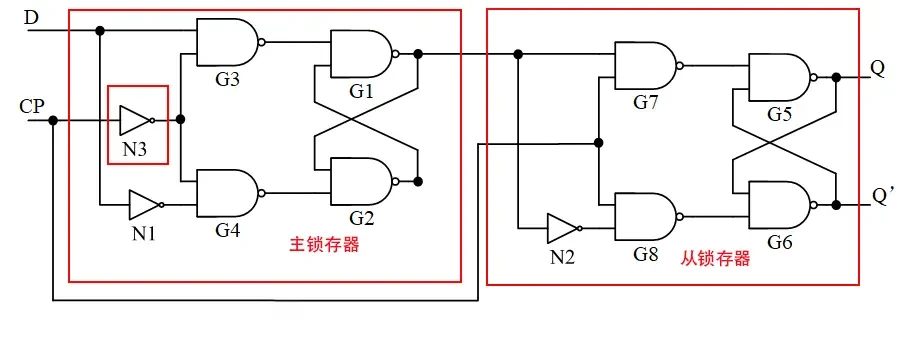

4)如果需要上升沿触发的触发器,即将上图中的取反模块N3接到主锁存器可是实现,下图即为上升沿触发的D触发器结构图

三、setup/hold来源详解

3.1 setup与hold

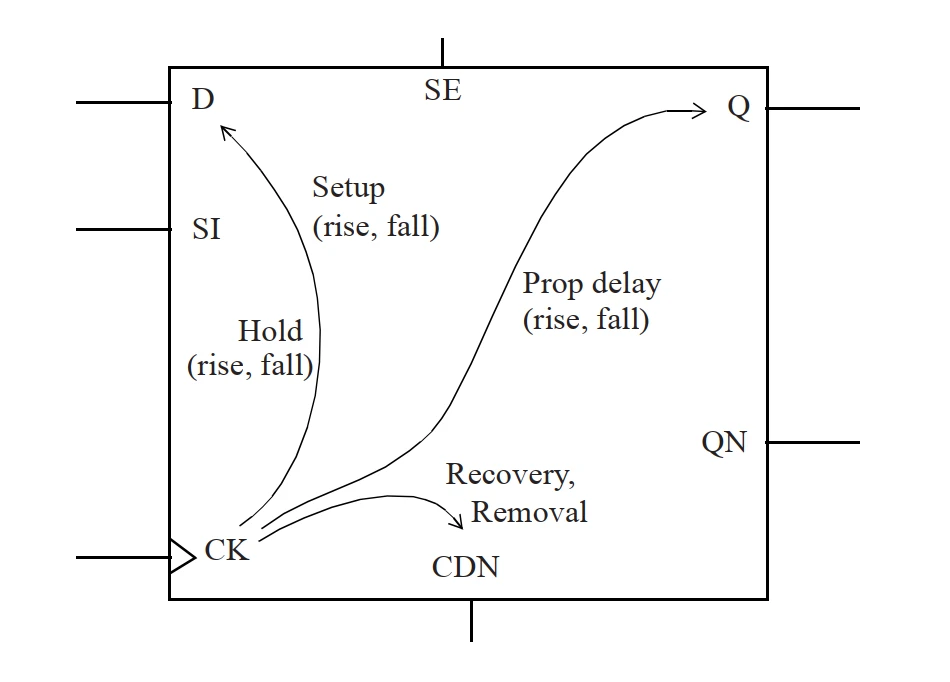

对于时序单元如触发器,从外部引脚中涉及到的各端口的时序分析类型如下图,分为3类

1)时钟端口CK与数据端口D的setup/hold分析,存在上升沿与下降沿

2)时钟端口CK和复位端口CDN间的removal/recovery分析

3)时钟端口CK到输出端口Q间传输延时分析

前面已对D触发器的结构来源进行了详细介绍,下面将对第一类setup/hold进行分析,以上升沿触发的D触发器为例。

3.2 setup内部分析

D触发器的结构中主要涉及非门和与非门,假设信号在非门和与非门中的传输时延分别为T0和T1,忽略其他线路的时延,数据信号D分两路传输,经过非门N1,G4,G2,G1的路径延时更大,总的延时Td=T0+3T1,时钟信号经过一个非门N3,时延Tclk=T0。在CP信号变成高电平前数据信号D需一直维持稳定的输入,两信号在触发器内部的延时差T=Td-Tclk=3T1即可近似理解为setup时间,即数据信号需至少比时钟信号提前T到达触发器的输入端口D,从而保证数据D能够在G1的输出端稳定维持住。

3.3 触发器内部hold分析

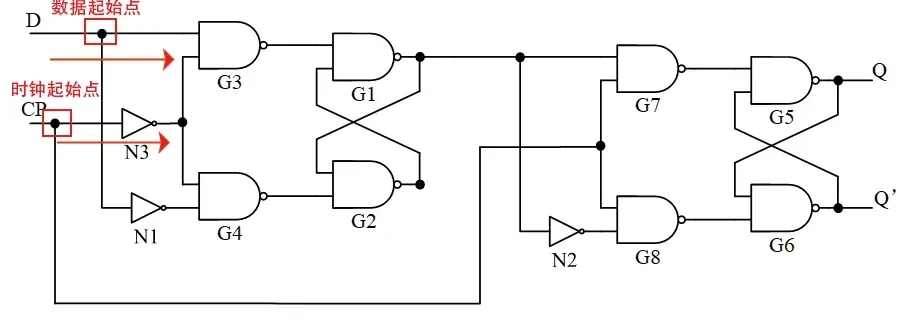

如下图中所示的数据起始点和时钟起始点,时钟信号还需要经过非门N3传输到与非门G3和G4,假设时延为Tclk,而数据路径分两路,一路直接到G3,另一路经过非门N1到达G4,延时为Tdata。假设当时钟信号CP达到时钟起始点后数据信号就发生变化,如从0变为1,则有可能数据信号先到达G3或G4,而时钟信号CP为1的信号后到达G3和G4,此时与非门G3的将是两个输入信号为1,最终导致G1输出变为1。即预期此时G1的输出值对应为CP为1,D为1下的输出,实际变为CP为0,D为1时的输出,可能出现逻辑错误,而hold时间可以看成Tclk-Tdata的时间,hold时间满足可保证数据正确地从与非门G5输出。

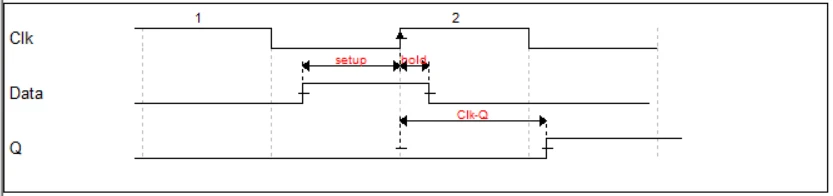

用波形关系表示触发器的setup和hold关系如下

根据前面的分析,setup、hold为触发器内部的特性,即数据信号和时钟信号分别到达触发器外部的数据端口和时钟端口和,分别进入触发器内部后对于两者延时的要求。通常情况setup和hold都是正值,但也存在为负值的情况。

在前面的设计中,默认触发器内部时钟的时延小于数据的延时,即Td>Tclk。但是在一些其他特殊情况,如内部时钟经过了缓冲器buffer,此时就可能出现Td<Tclk,setup即为负值。当setup为负值时,表示外部数据信号可以比时钟信号更迟到达触发器的外部端口。

注需注意此处的setup/hold表示触发器的固有特性,与常提到的setup/hold时序分析不同,setup/hold时序分析是指包括了触发器外部数据路径和时钟路径的延时,触发器的setup/hold被作为一个固定值计算进去。

setup和hold不能同时为负值,二者之和必须大于0。

3.4 时序模型文件查看setup/hold

前面说明了setup/hold的来源,在实际应用中,setup/hold值保存在时序模型文件*.lib中,最终体现在时序报告中。

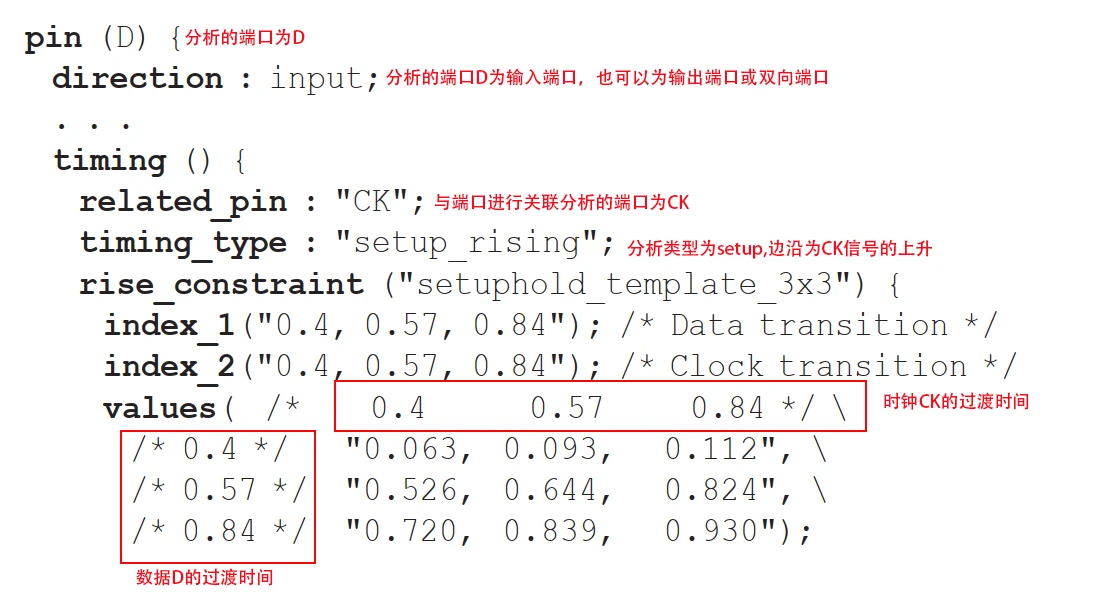

时序模型结构如下图二维模型,pin为D端口表示分析的端口数据数据端口,related_pin为时序单元中与pin存在时序关系的的其他端口,一般有很多个,下图只列举了CK端口,表示分析CK与数据D端口的时序关系,时序类型为setup_rising,表示分析CK与D的setup时序关系,边沿为时钟CK的上升沿。

信号的切换并非理想的瞬间变化,存在一定的时间,因此,信号从0到1或从1到0的变化是存在过渡时间的。 在时序分析中,D端口与CK端口的setup值根据D端口和CK端口的过渡时间通过查找时序模型表来确定,如D端口的上升沿过渡时间为0.57ns,CK端口的上升沿过渡时间为0.84ns,则D端口的上升沿setup值为0.824ns。

3.5 Datasheet查看setup/hold

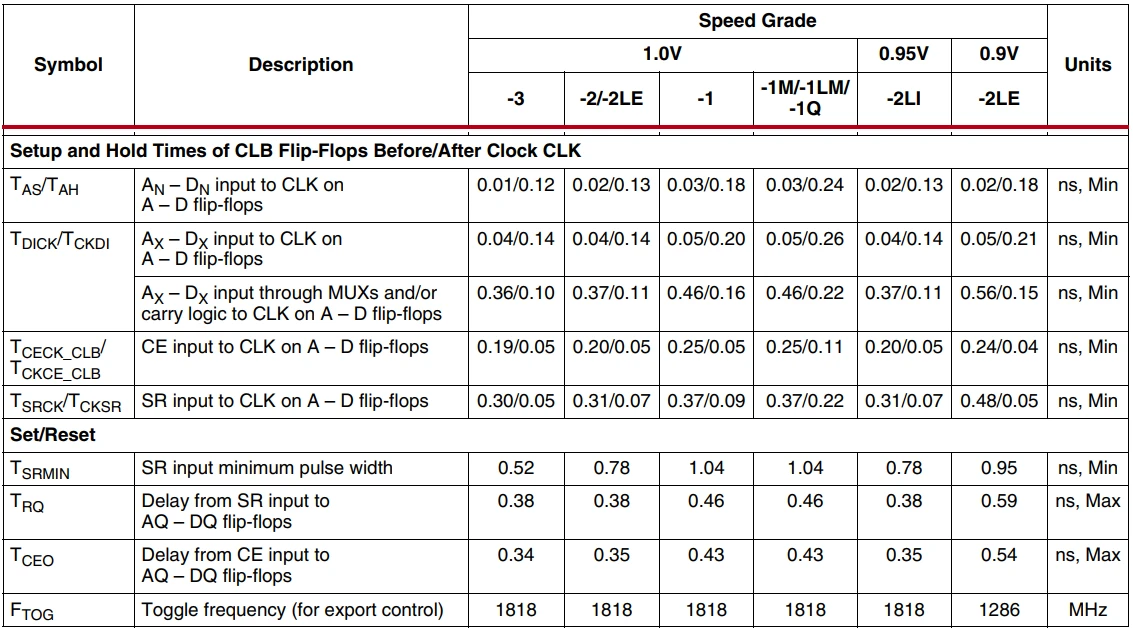

时序模型文件lib因涉及软件时序分析使用 ,对用户是不可见的。另一种方式查看对应器件官方提供的datasheet文档。以Kintex_7系列CLM中的FF单元为例,不同电压和不同速率下的setup/hold值是不同的。每个单元格有两个数字,前者为setup,后者为hold。除了数据端口D和时钟端口CLK的检查值,还有使能端口CE,复位端口SR与时钟端口的时序检查值。

3.6 时序报告查看setup/hold

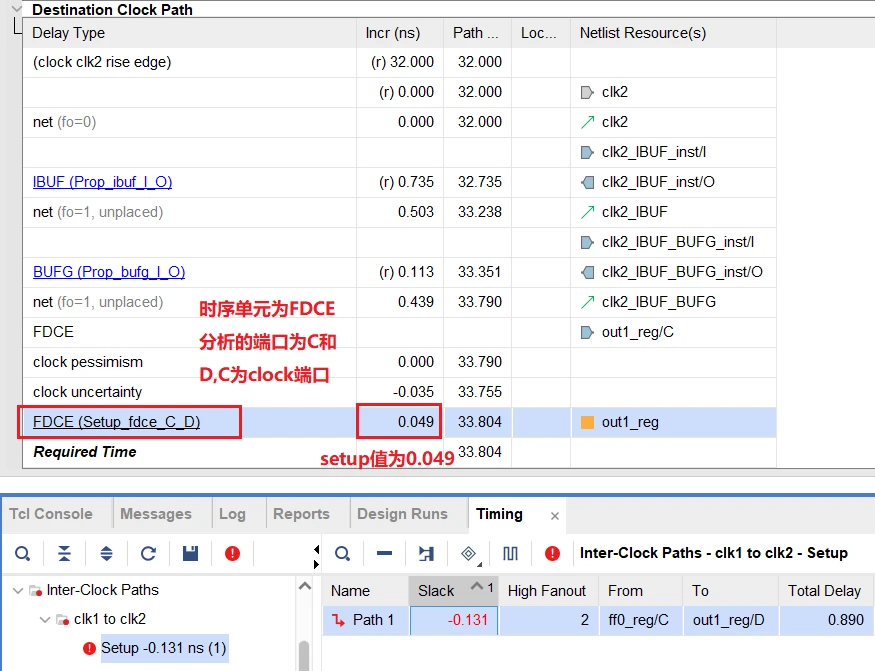

时序报告中查看setup/hold值是最简单的方式,选择包含查看单元的时序路径,该单元需为时序的终点endpoint,下图的setup值0.049

hold的值查看同理,同时可以通过Timing Delay Description查看

3.7 影响setup/hold值的因素

上面提到setup/hold芯片固有的硬件特性参数,相对固定的,但还是会受到一些因素的影响,主要由以下三类

(1)时序单元本身的结构,即芯片材料,结构

(2)工艺(process)、电压(voltage)和温度(temperature),即芯片工作的环境

(3)器件使用的时间,随着芯片使用的时间越长,内部有些特性会变化,也即“老化”现象

四、参考资料

1、《Static Timing Analysis for Nanometer Designs》

2、《PrimeTime user guide》

1318

1318

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?