Gerber文件叠层设置

前言

Gerber文件是一种电路板生产文件,它包含了电路板的各个层面的细节信息,如顶层、底层、丝印层、钻孔层等。Gerber文件通常用于生产电路板时进行制造、检查和维护,因此它们对于电路板制造和测试过程至关重要。

一、Gerber文件叠层

Gerber文件叠层可以归结为布线层、丝印层、阻焊层、钢网层、钻孔层、辅助制造。以四层板为例,文件叠层设置如下:

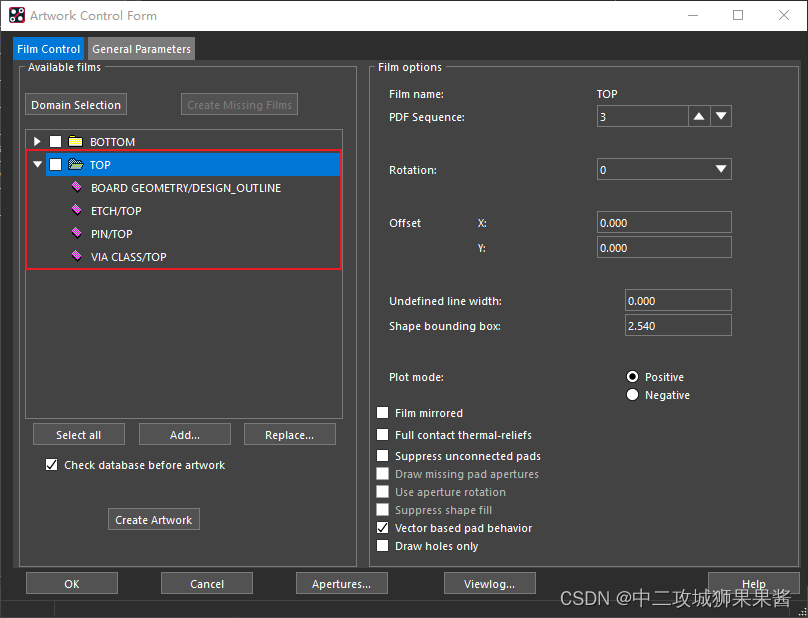

1.TOP

- Board Geometry — Design_Outline 板框

- Etch — Top 走线

- Pin — Top 焊盘

- Via Class — Top 过孔

2.BOTTOM

- Board Geometry — Design_Outline 板框

- Etch — Bottom 走线

- Pin — Bottom 焊盘

- Via Class — Bottom 过孔

3.GND02

- Board Geometry — Design_Outline 板框

- Etch — GND02 走线

- Pin — GND02 焊盘

- Via Class — GND02 过孔

4.PWR03

- Board Geometry — Design_Outline 板框

- Etch — PWR03 走线

- Pin — PWR03 焊盘

- Via Class — PWR03 过孔

5.SILKTOP

- Board Geometry — Design_Outline 板框

- Board Geometry — Silkscreen_Top 板层丝印

- Package Geometry — Silkscreen_Top 器件丝印

- Ref Des — Silkscreen_Top 位号

6.SILKBOT

- Board Geometry — Design_Outline 板框

- Board Geometry — Silkscreen_Bottom 板层丝印

- Package Geometry — Silkscreen_Bottom 器件丝印

- Ref Des — Silkscreen_Bottom 位号

7.SOLDTOP

- Board Geometry — Design_Outline 板框

- Board Geometry — Soldermask_Top 板层阻焊

- Package Geometry — Soldermask_Top 器件阻焊

- Pin — Soldermask_Top 焊盘阻焊

- Via — Soldermask_Top 过孔阻焊

8.SOLDBOT

- Board Geometry — Design_Outline 板框

- Board Geometry — Soldermask_Bottom 板层阻焊

- Package Geometry — Soldermask_Bottom 器件阻焊

- Pin — Soldermask_Bottom 焊盘阻焊

- Via — Soldermask_Bottom 过孔阻焊

9.PASTTOP

- Board Geometry — Design_Outline 板框

- Package Geometry — Pastemask_Top 器件阻焊

- Pin — Pastemask_Top 焊盘阻焊

10.PASTBOT

- Board Geometry — Design_Outline 板框

- Package Geometry — Pastemask_Bottom 器件阻焊

- Pin — Pastemask_Bottom 焊盘阻焊

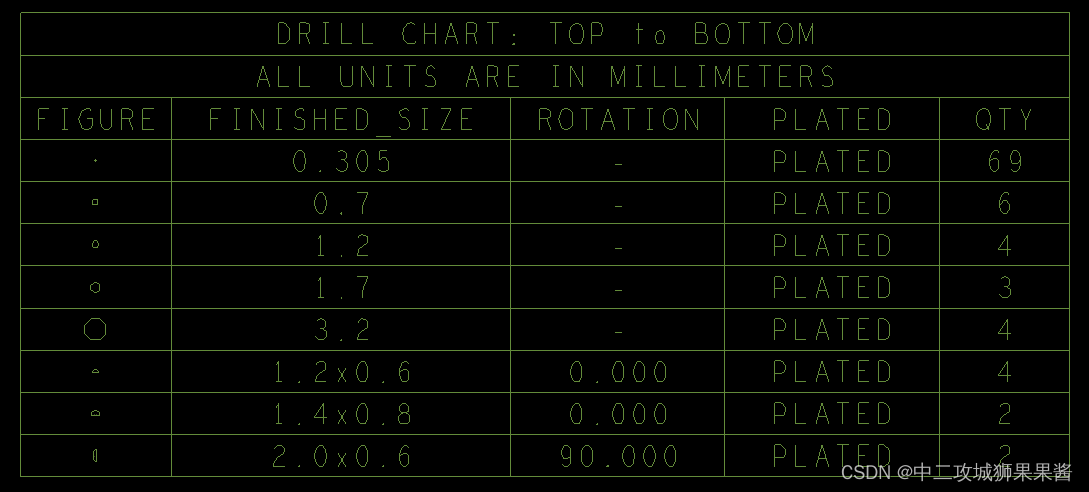

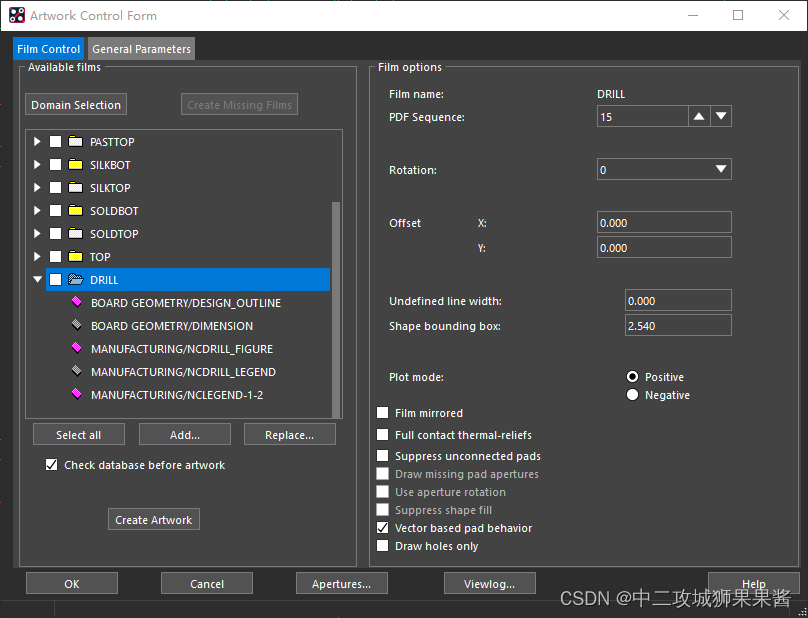

11.DRILL

- Board Geometry — Design_Outline 板框

- Board Geometry — Dimension

- Manufacturing — Ncdrill_Figure 钻孔符

- Manufacturing — Ncdrill_Legend 钻孔表

- Manufacturing — Nclegend-1-4

12.ADT

- Board Geometry — Design_Outline 板框

- Board Geometry — Silkscreen_Top 板层丝印

- Package Geometry — Silkscreen_Top 器件丝印

- Ref Des — Silkscreen_Top 位号

- Pin — Top 焊盘

13.ADB

- Board Geometry — Design_Outline 板框

- Board Geometry — Silkscreen_Bottom 板层丝印

- Package Geometry — Silkscreen_Bottom 器件丝印

- Ref Des — Silkscreen_Bottom 位号

- Pin — Bottom 焊盘

二、设置步骤

这里以TOP为例:

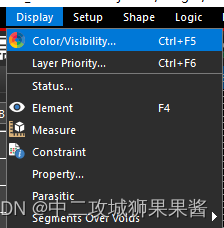

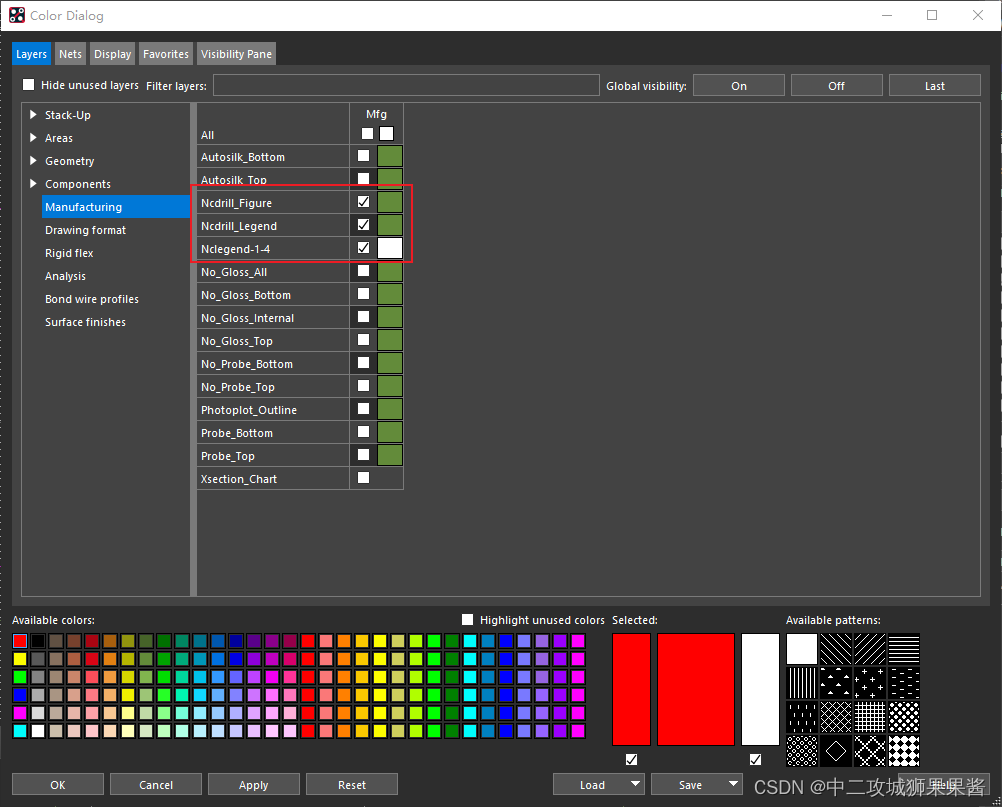

- 选择菜单栏中的Display,在弹出的下拉框中选择Color/Bisibility…;

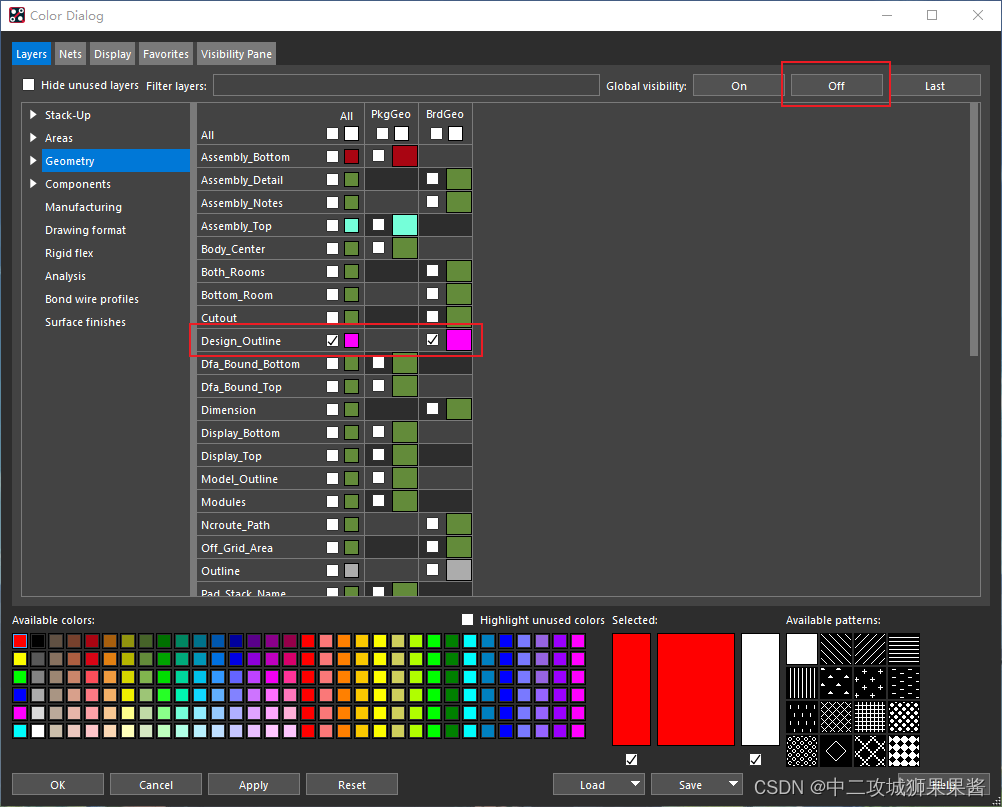

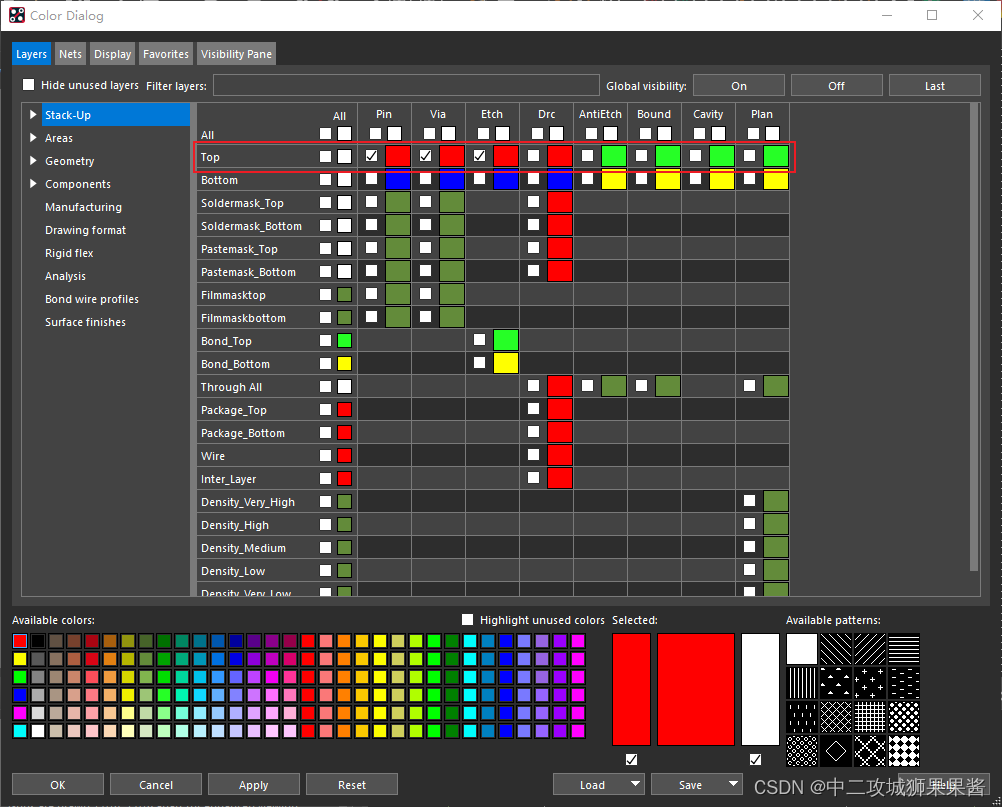

- 在对话框Color Dialog中先点击Off关闭所有图层,再勾选我们要显示的图层,选择完后点击OK;

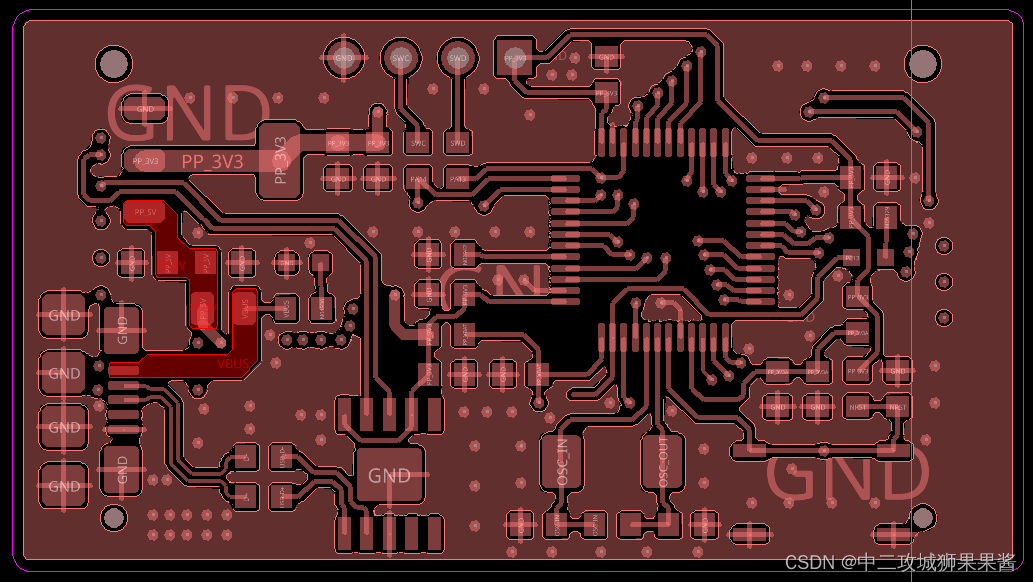

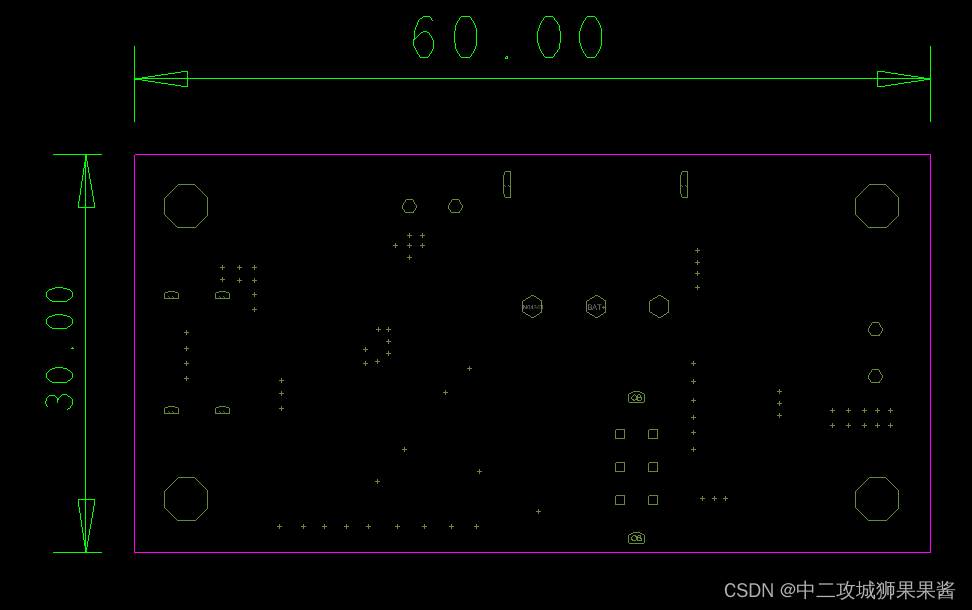

- 选择完后的显示效果如下

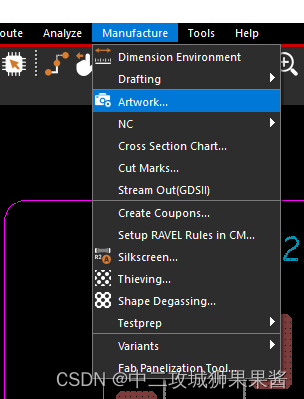

- 接着选择菜单栏中的Manufacture,在弹出的下拉框中选择Artwork;

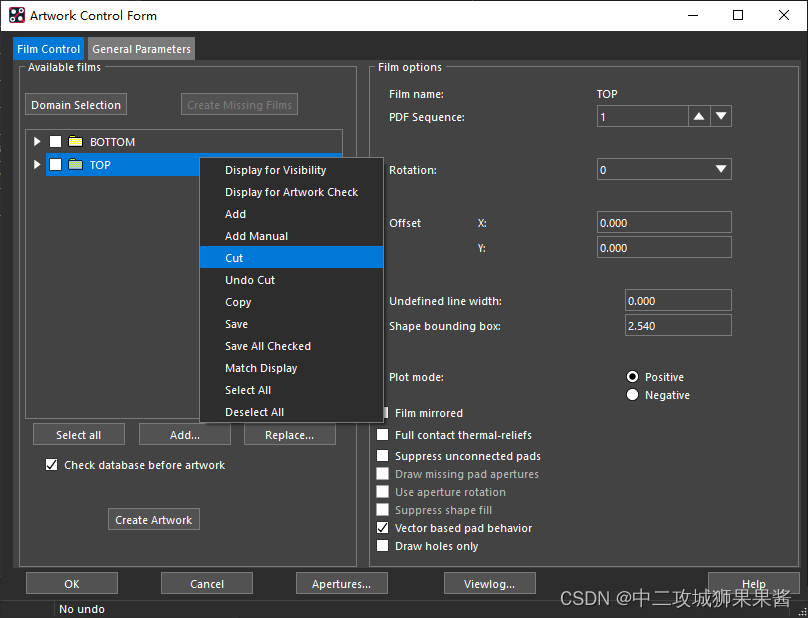

- 可以看到系统默认给我们创建了TOP和BOTTOM层,我们可以选择右键选择Cut删除掉;

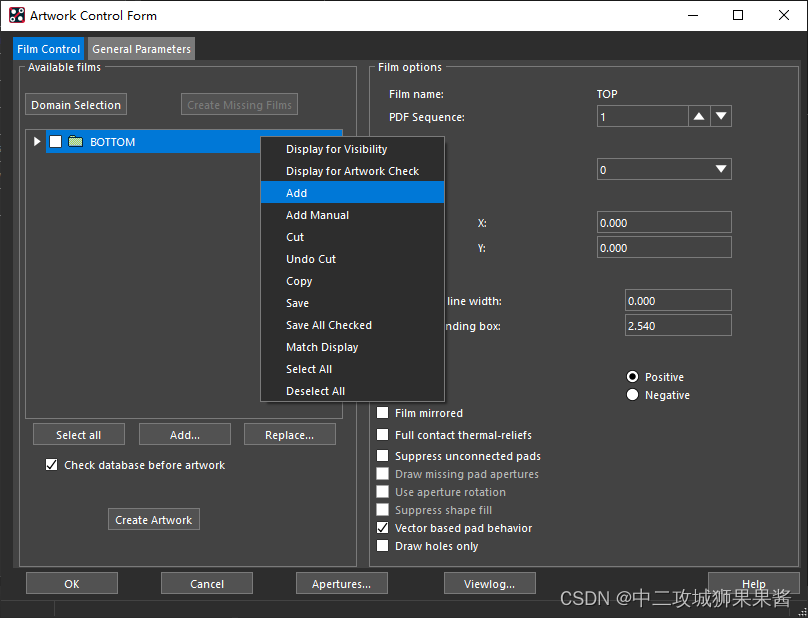

- 右键选择Add,命名为TOP即可;

- 点开TOP,可以看到已经把需要的层添加到了TOP里了,其它层也是类似的,重复以上步骤添加就好。

三、DRILL层设置

这里的钻孔层添加比较特殊,需要生成孔符图和钻孔表。

-

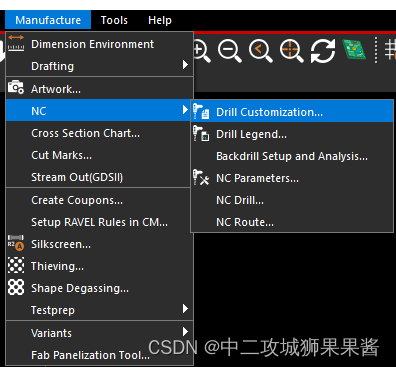

首先我们先更新一下孔符图,避免制作封装的时候有相同的孔符图存在,点击菜单栏的Manufacture,选择Drill Customization…;

-

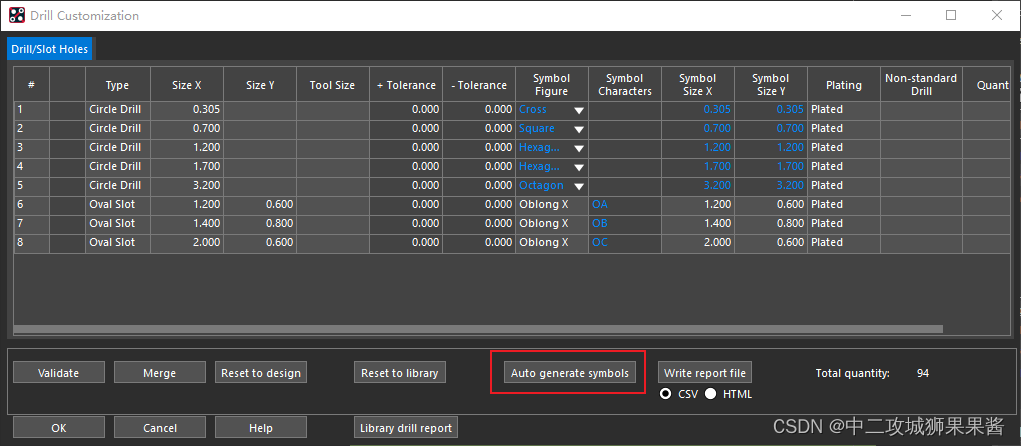

在弹出的对话框中,点击Auto generate symbols软件会自动生成钻孔符,再点击Write report file写入文件中,最后点击OK;

-

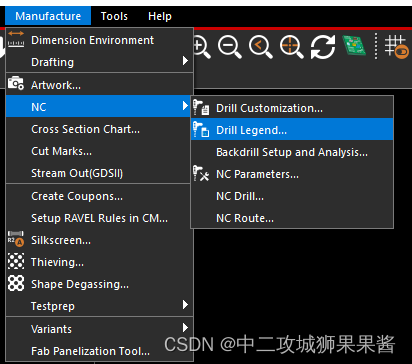

更新完孔符图就可以生成我们的钻孔表了,点击菜单栏中的Manufacture,选择Drill Legend…;

-

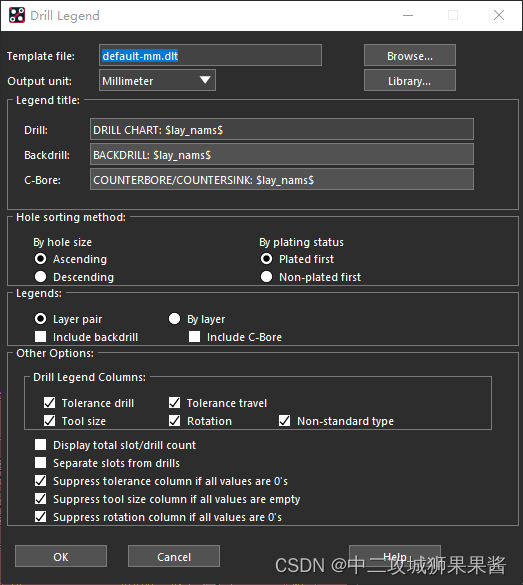

弹出对话框中,点击OK,即可生成钻孔表;

-

生成的钻孔表如下:

-

接着我们添加DRILL层, 和之前的类似,在Color Dialog中勾选我们要显示的图层,选择完后点击OK;

-

显示效果如下:

-

同样在我们的Artwork中添加DRILL。

四、总结

写作不易,如果觉得对你有用,帮忙点赞👍收藏⭐️哦,你的支持会让我有更多动力写下去💪💪💪!商务合作可以私信我哦💌!

本文详细介绍了Gerber文件在电路板叠层设置中的重要性,包括各层定义和设置步骤,如TOP、BOTTOM、GND02、PWR03等,以及特殊处理的钻孔层设置。

本文详细介绍了Gerber文件在电路板叠层设置中的重要性,包括各层定义和设置步骤,如TOP、BOTTOM、GND02、PWR03等,以及特殊处理的钻孔层设置。

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?