CPCI总线

•PCI总线作为处理器系统的局部总线,主要目的是为了连接外部设备,而不是作为处理器的系统总线连接Cache和主存储器

•(1) PCI总线空间与处理器空间隔离

•(2) 可扩展性 桥

•(3) 动态配置机制即插即用

•(4) 总线带宽

•(5) 共享总线机制

•(6) 中断机制

PXI

•PXI规范是CompactPCI规范的扩展

•PXI在CompactPCI的机械规范上强制增加了环境性能测试与主动冷却装置,以简化系统集成并确保不同厂商产品之间的互用性。

•PXI还在高速PCI总线的基础上补充了测量与自动化系统专用的定时与触发特性

•PXI是一种坚固的模块化仪器平台,它提出了基于计算机的高性能标准化测量与自动化方案

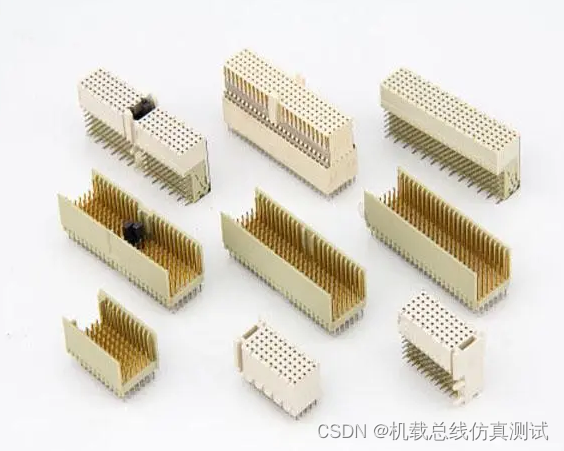

CPCIE基本概念

•PCI Express的接口根据 总线 位宽不同而有所差异,包括X1、X4、X8以及X16(X2模式将用于内部接口而非插槽模式)。PCI Express规格从1条通道连接到32条通道连接,有非常强的伸缩性

•较短的PCI Express卡可以插入较长的PCI Express插槽中使用。PCI Express接口能够支持热拔插,PCI Express卡支持的三种电压分别为+3.3V、3.3Vaux以及+12V。

•用于取代 AGP 接口的PCI Express接口 位宽 为X16,将能够提供5GB/s的 带宽,即便有编码上的损耗但仍能够提供4GB/s左右的实际带宽,远远超过AGP 8X的2.1GB/s的带宽。

CPCIE总线

•PCI总线使用并行总线结构,在同一条总线上的所有外部设备共享总线带宽,而PCIe总线使用了高速差分总线

•并采用端到端的连接方式,因此在每一条PCIe链路中只能连接两个设备。

•端到端的数据传递

•PCIe插槽需要使用参考时钟,其频率范围为100MHz±300ppm

2万+

2万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?