基于线‐TFET器件实验数据的模拟电路设计:从器件到电路层面

摘要

本研究探讨了线隧穿场效应晶体管(Line TFET)器件在模拟应用中的使用。文中展示了这些器件的直流和小信号特性,并将其与其他TFET结构以及传统MOSFET技术进行了比较。通过对Line‐TFET的饱和特性进行仿真和实验表征,深入研究发现,源极到漏极的点隧穿漏电流不仅限制了偏置电压和栅极面积,还导致输出电导与栅极长度无关。为此设计了一个共源极级电路来说明并进一步探究这一现象,并与传统MOSFET技术进行了对比。为了获得具有极高电压增益的放大器,设计了一个两级运算跨导放大器(OTA),并考虑了两种不同的设计起点:固定晶体管效率(gm/Ids)或固定归一化电流(Ids/W),以使Line‐TFET与MOSFET器件在相近的性能条件下进行比较。结果表明,Line‐TFET设计始终能够实现更高的本征电压增益(高达115分贝),更适用于低功耗、低频应用。因此,进一步采用100纳米栅极长度的Line‐TFET器件完成了第三种设计,实现了71分贝的开环电压增益和18纳瓦的功耗,该设计可能适用于生物信号采集等应用。

关键词

线性TFET,模拟电路设计,运算跨导放大器。

一、引言

文献最初认为隧穿场效应晶体管(TFETs)是用于高密度数字应用的有前景的器件,有可能克服当前摩尔定律面临的挑战[1]。然而,越来越多的近期研究开始考虑将TFETs应用于信号放大和模拟电路设计[2]‐[6]。这种对TFETs在上述应用中使用的兴趣是有根据的,因为这些器件具有超低输出电导(gd),并且已被证明对温度变化[7]和噪声[2]具有较强的抗性。然而,由于陷阱和声子辅助隧穿(TAT)的影响,TFETs存在亚阈值斜率退化以及漏极电流较低的问题,尤其是在硅器件中更为明显。因此,研究人员已设计出采用不同材料的不同结构,例如本文所研究的具有Si 0.55 Ge 0.45 源极的线隧穿场效应晶体管(Line‐TFET)[8]。该器件由比利时微电子研究中心(imec/Belgium)制造,相较于其他 TFETs表现出较高的漏极电流,同时具有非常高的本征电压增益(Av),是一种适用于模拟应用的有吸引力的器件 [2][9][10]。

到目前为止,线隧穿场效应晶体管在电路应用方面的研究还很少。因此,本工作研究了使用这些器件的放大器设计,揭示了其特性如何影响所实现的性能指标和电路设计。此外,由于缺乏实验数据且建模困难,文献中报道的基于TFET的电路通常采用仿真且具有一定理想化程度的器件[3]–[5],[10]。这些研究主要关注在亚阈值区偏置TFET时所能实现的更高能量效率(通过gm/Ids参数),而这通常需要忽略多种非理想性(例如带间隧穿TAT)。本文是少数基于实验器件数据研究TFET电路应用的工作之一,所得设计更具可行性,并为设计者提供了考虑多种非理想性的设计指导,例如设计者可实际采用的反型程度。该方法还揭示了器件级别的独特特性,特别是该器件中输出电导gd与栅极长度Lg无关的现象,这一现象通过器件仿真得到解释,并在电路设计中进一步探讨。为了探索线隧穿场效应晶体管Line‐TFET的潜在应用,我们设计了一个两级运算跨导放大器(OTA),考虑了不同的设计起点,从而能够与传统MOSFET技术以及文献中的其他TFET设计进行比较。

II. 器件描述

A. 器件结构与工作原理

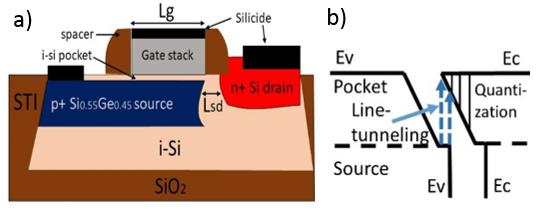

本文研究的由比利时微电子研究中心(imec/Belgium)制造的线隧穿场效应晶体管(Line‐TFET)(其制造工艺概述见[8])具有由Si0.55Ge0.45构成的源极区域,该区域采用硼进行重掺杂(1.1020原子/立方厘米),并沿栅极全长延伸,理想情况下与栅极末端对齐。在源极与栅极之间存在一个约5 nm厚的理想未掺杂硅区域(尽管由于源极的扩散,在口袋区中硼浓度最高可达1.1019原子/立方厘米)。在源极与漏极之间是另一个理想未掺杂的硅区域,其长度为Lsd,如图1.a)所示。漏极采用n 型掺杂,砷(As)浓度为5.1018原子/立方厘米。等效氧化层厚度为0.9 nm,栅堆叠由SiO2/HfO2(1.8 nm)/TiN(2 nm)/P型掺杂 α‐Si组成。隔离氧化物延伸至表面形成浅沟槽隔离(STI),用于实现晶体管之间的电学隔离(图2.a)中的棕色区域),接触部分由硅化物构成(图2.a)中黑色部分表示),以获得较低的接触电阻。在此器件中,隧穿发生在垂直方向,即从源极价带到口袋区导带。因此,栅极电场不仅引起能带弯曲,使口袋区导带中出现可利用的能量态(由于口袋厚度极小,其能级发生量子化),同时还促进电子隧穿,如图1.b)所示;而在传统 TFET中,电子隧穿由横向电场驱动。这种机制被称为线隧穿,因其沿栅极长度方向均匀发生,不同于传统的点隧穿。由于隧穿面积增加以及采用了锗硅源极(SiGe source),该器件结构可实现更高的漏极电流(数量级为若干微安每微米)。同时,由于隧穿窗口迅速关闭,亚阈值摆幅(SS)更陡峭(在室温下最小值约为55 mV/decade),尽管带间隧穿(TAT)对其有所限制。在此器件中,漏极电流与栅极面积成正比[8]。

B. 直流电学特性

该器件采用Verilog‐A硬件描述语言实现的漏极电流 (Ids)和寄生电容关于栅极与漏极电压(分别为Vgs和 Vds)的查找表进行建模。电流特性通过对栅极长度Lg =1μm的器件进行实验表征获得,而寄生电容则通过新思科技的TCAD程序Sentaurus建模估算。电路仿真使用楷登电子的Spectre类Spice电路仿真器完成。

图2.a)展示了通过查找表方法获得的连续模型以及器件的实验Ids与Vgs特性,其中Lg=1μm。在Vgs=1.2V至Vgs=1.8V范围内,线隧穿在电流输运中占主导地位,超过TAT和漏极到源极的隧穿。在此偏压范围内的电流水平介于约 100nA/μm至10μA/μm之间。与某些点隧穿场效应晶体管结构相比,该电流水平比硅基TFET高出约1000倍[6][9], ,比 SiGe基TFET高出约10倍[5][9], ,但低于III‐V族TFET和传统 MOSFET[3]。在Vgs=0.7V(最坏情况下,此时Vds=1.8V, 因为该值对Vds高度依赖)至Vgs=1.2V的亚阈值区,TAT是 主要的导通机制[8],[9], ,这会导致亚阈值摆幅恶化。当 Vgs更小时,由于源极到漏极的隧穿效应,关态电流对Vds高度依赖[8]。这导致在较低Vds值下,最小亚阈值摆幅有所降低[8],[9]。值得注意的是,由于该器件的几何结构存在栅极与 漏极之间的未重叠区,其双极性电流被有效抑制[8]。图2.b)显示了Vgs从1.2V到1.8V时的Ids与Vds曲线。可以看出, 该器件具有优异的饱和特性,实现了良好的输出

输出电导(gd)在Vgs=1.8V时低至5.5nS/μm。饱和电压( Vdsat)范围约为460mV至约800mV。通过用一条斜率为平均输出电导的直线对类饱和区进行插值,并检查其与x轴的交点,表明该器件的厄利电压(VA)超过100V,而在缩放型 MOSFET技术中,该值几乎不超过5V [3][11]。这是TFETs具有极高本征电压增益的关键,可解释如下:在Vds较低时, TFETs的Ids x Vds特性由源极和沟道中能态的费米占据概率决定。随着Vds增加,源极中的能态逐渐变空,而本征区(对于线隧穿场效应晶体管而言,对应于口袋区和源漏间距)中的能态则逐渐被填充。这解释了TFETs典型的超线性电流特性和延迟饱和现象 [12],[13]。然而,这一现象不会无限持续,当 Vds足够高时,本征区会出现载流子耗尽。此时,表面势和导带均被钉扎,电流对Vds的依赖变得非常小,进入类饱和区, 从而导致极高的VA[10],[14]。

图3.a)和3.b)分别展示了通过TCAD仿真并结合实验数据 拟合后得到的寄生电容Cgs、Cgd和Cgg=Cgs+Cgd随Vgs( Vds=1V)和Vds(Vgs=1.25V)的变化情况。分析两幅图可知, 除较高的Vgs和较低的Vds外,漏极电荷均可忽略不计。因此, 在线性工作区,Cgs与Cgd达到相近的数量级。在类饱和区, Cgs成为主导的寄生电容,而Cgd可忽略。通常情况下, TFET由于源极/沟道突变结处通过隧穿产生的载流子远少于漏极电荷,导致Cgd在任何偏置区域均大于Cgs,因而表现出较强的密勒效应。但Line‐TFET不存在此现象,因其源极沿整个栅极长度延伸,使得源极处的电荷更为显著。在放大器设计中, 晶体管通常工作在类饱和区,因此采用Line‐TFET设计时密勒效应的降低有望提升频率响应。

C. 小信号特性

图4.a) 描绘了晶体管效率(gm/Ids)和单位增益频率 (ft,即晶体管增益达到0分贝时的频率,由 ft=gm/2πCgg 给出) 随归一化漏极电流(Ids/W)的变化关系,其中 Vgs 从 1.1伏特 到 1.8伏特,Vds=1伏特。gm/Ids 的可用范围约为 4伏特-1 到约 12伏特-1。该范围可为设计者提供一定灵活性,但与大多数MOSFET技术相比仍较有限,后者可达约 25伏特-1 [11]。通过在制造工艺中降低缺陷浓度以减小带间隧穿的影响,以及通过增加源极到漏极间距来减小漏极到源极隧穿(从而提高 Vgs 的下限值),可实现更高的晶体管效率。[8],[15],根据 Ids/W 的取值,ft 从约 5 兆赫兹 到约 500 兆赫兹,这比某些 III‐V族点型TFET和纳米级MOSFET低约 100 至 1000 倍,但 相比之前已实现约 10 倍的提升

与锗硅点式TFET [4]相比,以及与硅点式TFET [6]相比,提高了100到图10400.b倍)。显示了本征电压增益(Av)随归一化漏极电流的变化关系。由于厄利电压极高,该值可达60分贝, 而纳米级MOSFET技术几乎不超过20分贝[11]。与其他 TFET结构相比,该值通常高于大多数III‐V族TFET的本征电压增益[3]但低于硅基点式TFET的电流[6],[9]。

D. 栅长变化

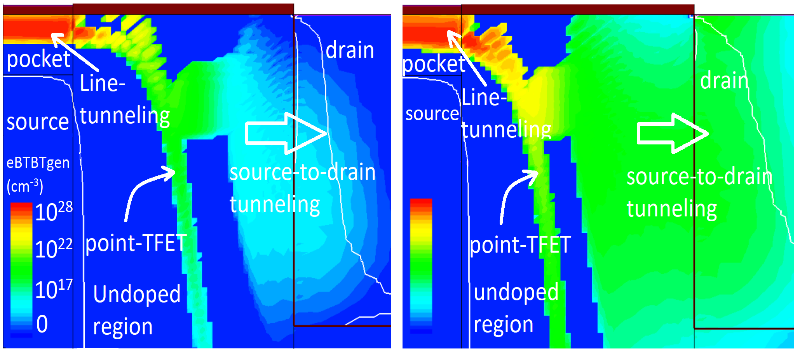

源极到漏极隧穿在线隧穿场效应晶体管的整个转移特性中起着重要作用,而不仅仅影响关态漏电流。这种隧穿通过由源极‐本征‐漏极区域界面构成的P‐i‐N结形成的短沟道点式TFET发生,其沟道长度等于Lsd,如图 1.a)所示[16]。为了进一步研究这一现象,采用TCAD程序Sentaurus对器件进行仿真,栅极长度Lg=1μm,口袋厚度tpocket=6nm,源漏间距Lsd=25nm,以及1.1019cm-3(硼)的均匀口袋掺杂。由于掺杂剂从源极扩散导致的高斯分布在如此小的长度(口袋厚度)内近似为常数, 因此可合理地认为口袋掺杂是均匀的。图5.a)和b)分别显示了在Vgs=2V、Vds=1V 和 Vds=1.8V 时该区域的电子隧穿产生率,而图5.c)显示了这两种情况下的能带图。图 5.a)和b)表明,该漏电流高度依赖于Vds,如果线隧穿越弱,则漏电流可能显著增大。图5.c)表明,引起该电流的寄生点式TFET是一种短沟道晶体管,会受到严重的漏致势垒变薄(DIBT)影响[16], ,这与之前报道的情况类似 [17]。虽然增加Lsd可减小源极到漏极的隧穿,从而允许在更低的偏置电压下使用更短的栅极长度工作,并改善 gd,但必须将Lsd限制在约40nm以下,以避免器件内阻显著增加,因为这是一个高电阻率区域。这可能会显著提高饱和电压,并降低线性工作区的电流水平[8][16].图5.c)的插图展示了该寄生点型TFET在不同漏源电压下的最小隧穿距离。

这种现象的后果如下所列:

1) 最小栅极偏压的限制:如果Vgs过低,线隧穿将与源极到漏极的隧穿达到相同的数量级,从而降低器件的饱和特性。对于栅极长度为1微米的器件,当Vgs约为=0.6伏特时,Vds =1伏特下的饱和特性开始下降,如[9]所示。

2) 最小栅极长度的限制:栅极面积越小,线隧穿越小。当减小栅极宽度(W)时,线隧穿和源极到漏极隧穿以相同比例减小; 但当减小Lg时,只有线隧穿减小。这意味着更短的器件更容易出现类饱和区退化,因此必须在更高的栅极电压下工作。图6展示了70纳米长器件的实验漏极电流随漏极电压变化曲线。当Vgs为 =1.2V时,随着Vds=1V,饱和特性开始退化[16]。

3) 输出电导在深度饱和下与栅极长度无关:即使线隧穿在源极到漏极隧穿中占主导地位,对于足够高的Vds,后者的随Vds的变化要大得多。因此,这种情况下漏极电流Ids随Vds的变化(或输出电导gd)基本上取决于寄生点型TFET,而当Lg变化时,该寄生点型 TFET保持不变。

图7显示了栅极长度Lg从100纳米到1微米的模拟器件的跨导与漏源电压特性(tpocket=6纳米且Lsd=35纳米),而插图描绘了漏源电流与漏源电压转移特性。在[10],软饱和和深饱和电压被定义为漏源电压Vds的值,分别对应于口袋区以及源极与漏极之间的本征区中的载流子完全耗尽的情况。在这种情况下,无论Vds多高,输出电导gd应渐近地降至一个最终值。然而,如图7所示,gd最终开始上升,因此我们将深饱和电压定义为∂gd/∂Vds=0达到峰值时所对应的Vds值, 这表明点式TFET中的导电机制与先前报道的深饱和机制存在重叠。此外,如图7所示,一旦进入深饱和状态,gd达到相同的值,而与栅极长度无关[16]。图8通过实验验证了这些结果。它展示了栅极长度分别为70纳米、130纳米和1微米的器件在栅源电压Vgs=1.8伏特时,归一化到栅极面积的实验转移特性, 其平均输出电导分别为4.5纳西、4纳西和4.7纳西。电流水平不一致是由于工艺变化引起的,尤其是口袋厚度[8]的不同所致。

E. 小信号参数对栅极尺寸的依赖性

漏极电流与栅极面积(W×Lg)的正比性以及gd与 Lg的无关性,是线隧穿场效应晶体管独有的特性,这些特性将改变使用此类器件进行模拟电路设计的方式。通常, 在使用传统MOSFET技术时,如果设计者希望提高本征电压增益(等于gm/gd),则需增加Lg以降低gd。而对于线隧穿场效应晶体管,也应增加Lg,但这是因为跨导( gm)随之增加,而gd保持不变,前提是W保持相同[16]。

表I总结了小信号参数随栅极尺寸的变化关系,比较了传统MOSFET技术和线隧穿场效应晶体管。由于在饱和区gd = Ids/VA ,可以看出对于MOSFET而言,输出由于电流水平按W/Lg缩放,且V与沟道长度调制相关的Lg成正 比,因此电导与1/Lg2成正比A [11]。对于线隧穿场效应晶体管, 由于定义gd的寄生现象发生在栅极以外的区域,因此该参数仅随宽度W缩放,而不依赖于栅极长度Lg,这意味着厄利电压和电流水平均与Lg成比例。如 所述,单位增益频率(ft)不依赖于Lg,因为跨导gm和寄生电容(Cgg)均与Lg成正比,而ft = gm/2πCgg。这意味着增益带宽积(GBWP =Av.ft,该品质因数用于评估增益与动态性能之间的折衷)在线隧穿场效应晶体管中随Lg成比例增加,这与金属氧化物半导体场效应晶体管相反,在后者中GBWP随Lg成比例下降[11]。这对于线隧穿场效应晶体管而言是一个主要优势,因为从工艺角度来看,减小沟道长度具有挑战性且成本高昂[16]。

| 金属氧化物半导体场效应晶体管 | 线隧穿场效应晶体管 | |

|---|---|---|

| Ids | ∝ 宽度/栅极 长度 | ∝ 宽度 x 栅极 长度 |

| gm | ∝ 宽度/栅极 长度 | ∝ W x Lg |

| gd | ∝ W/Lg2 (*) | ∝ W |

| Av (gm/gd) | ∝ Lg | ∝ Lg |

| Cgg | ∝ W.Lg | ∝ W.Lg |

| ft(gm/2πCgg) | ∝ 1/Lg2 | 常数 |

| GBWP (Av.ft) | ∝ 1/Lg | ∝ Lg |

(*) 考虑沟道长度调制

III. 基于线型TFET的模拟电路设计

为了简化后续分析,假设P型和N型晶体管是对称的,并且在电路设计中忽略了栅极漏电流。用于与线隧穿场效应晶体管设计进行比较的MOSFET技术是65纳米和130纳米工艺中的传统SOI平面拓扑结构,这两种工艺目前在模拟电路设计中被广泛使用。

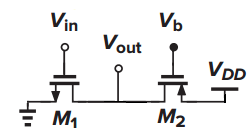

A. 采用电流源负载的共源极级电路

设计了一个带有电流源负载的共源极级(图9),旨在说明之前关于Line‐TFET的小信号参数与栅极尺寸依赖关系的讨论。

当增益增加时,小信号参数的变化会导致一种结果:在使用线隧穿场效应晶体管时,设计者可以选择通过按相同比例减小宽度W来抵消栅极长度Lg的增加,从而保持跨导gm和电流水平不变,同时降低输出电导gd;或者在增加Lg时保持W不变,从而提高跨导gm和电流水平,而输出电导gd保持不变。表二比较了采用MOSFET和线隧穿场效应晶体管的共源极级配合电流源负载的设计,在该设计中希望将电压增益从初始状态加倍。{v3}和 GBW分别表示3dB截止频率和0dB交叉频率。图10描绘了两种技术在上述两种情况下最终设计的波特图。

| 器件 | MOSFET | MOSFET | MOSFET | 线隧穿场效应晶体管 | 线隧穿场效应晶体管 | 线隧穿场效应晶体管 |

|---|---|---|---|---|---|---|

| 情况 | 初始 | 恒流 恒定 | 宽度 初始 | 恒流 | 恒定宽度 | |

| Lin(nm) | 130 | 260 | 260 | 300 | 600 | 600 |

| Win(nm) | 200 | 400 | 200 | 140 | 70 | 140 |

| Lload(纳米) | 130 | 260 | 260 | 300 | 600 | 600 |

| Wload(纳米) | 200 | 400 | 200 | 400 | 200 | 400 |

| 电流(安培) | 15.5μ | 15.5μ | 7.75μ | 66n | 66n | 132n |

| Gm(西) | 110µ | 110µ | 55µ | 400n | 400n | 800n |

| 输出电阻(欧姆) 125千 | 260k | 550k | 350M | 700M | 350M | |

| 电压增益 (分贝) | 21 | 27 | 27 | 44 | 50 | 50 |

| Fc3dB (赫兹) | 28M | 14M | 7M | 10k | 5.1k | 10k |

| 增益带宽积(赫兹) 3亿 | 300M | 160M | 1.5M | 1.5M | 3M |

在MOSFET设计中,唯一有趣的情况是保持电流水平恒定,这会导致gd值减半而gm保持不变。由于gd值降低, 使得第一级输出节点的时间常数1/RC降至原来的一半, fc3dB也随之减半,但gm保持不变,因此GBW也保持不变。与恒定W情况相比,该情况下的输出电阻增加了4倍,而 gm降低了2倍,导致fc3dB下降为原来的1/4,GBW下降为原来的1/2。在恒定I或恒定W情况下,电路面积分别扩大为原来的4倍或2倍。

使用线隧穿场效应晶体管(Line‐TFETs)时,为了使电路电压增益加倍,可以选择在保持跨导gm不变的同时提高输出电阻Rout, 或者在保持Rout不变的情况下将gm加倍。在第一种情况下,由于宽度W减小,电路面积保持不变;而在宽度W恒定的情况下,电路面积则加倍。线隧穿场效应晶体管的另一个有趣特性是,当栅极长度Lg增加时,特征频率ft保持不变,而增益带宽功耗积GBWP提高;而对于MOSFET,两者均会下降。在电流I恒定的情况下,结果与MOSFET相同:跨导gm和增益带宽积GBW保持不变,但由于输出电导 gd减小,截止频率fc 3dB 降低。然而,在宽度W恒定的情况下,由于 gm加倍,GBW也加倍,而Rout和fc 3dB 保持不变。综上所述,这对于增益和使用线隧穿场效应晶体管时,频率响应允许采用更大的栅极长度值[16]。

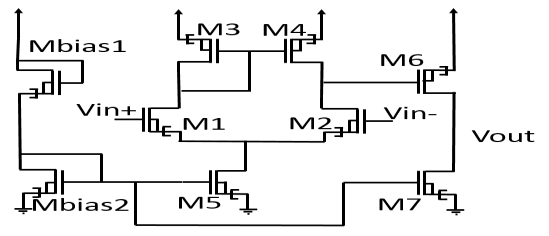

B. 两级运算跨导放大器设计:与MOSFET技术的比较

图11显示,所选的放大器拓扑结构中,第一级为采用有源负载的差分对,且使用较少的晶体管,从而简化了偏置电路,并实现了具有差分输入的单端输出。该级与共源级相连接, 以获得最大输出摆幅和高电压增益,总增益由两级电压增益的乘积给出。图11还展示了一种提出的线隧穿场效应晶体管的电路符号表示,其中口袋区位于源极隧道结的上方。该符号表示此器件中电学参数对栅极尺寸的特殊依赖性[18]。

为了与传统MOSFET技术进行比较,设计在不同的起始条件下进行:相同的gm/Ids和W,以及相同的Ids/W和W。由于P型和N型MOSFET晶体管之间存在不对称性(源于载流子迁移率的不同),只有输入晶体管(M1和M2)具有固定的宽度值。出于稳定性考虑,第二级晶体管的宽度也不固定,但必须至少是第一级晶体管宽度的10倍。负载电容和补偿电容(分别为CL和CC)保持不变,其值分别为50飞法和25飞法。

1) 采用固定的跨导与漏源电流比和宽度的设计

表示跨导与漏源电流比的中间值在线隧穿场效应晶体管(图4.a)获得的范围内,该设计采用8伏特-1作为晶体管效率的值。输入晶体管(M1和M2)的宽度固定为150纳米,接近MOSFET 130纳米工艺可提供的最小值。增益和相位随频率的变化分别如图12.a)和12.b)所示,晶体管尺寸设计见表III,结果总结于表IV。

结果表明,线隧穿场效应晶体管设计具有1.4伏峰峰值的高输出摆幅、极高的开环电压增益(110分贝)以及80兆欧的输出电阻。由于线隧穿场效应晶体管的电流水平低于MOS器件,该电路功耗极低,约为3.2微瓦,即使在2.5伏特较高的电源电压下也是如此,但这也导致补偿后的增益带宽积(GBW)较低,为5.5兆赫。图12显示,由于这些器件的输出电阻显著更高,线隧穿场效应晶体管设计的3dB截止频率(fc)明显更低。此外,由于输出电导(gd)较低,线隧穿场效应晶体管设计具有更高的共模抑制比(CMRR),这也是采用TFET时实现拓扑简化的一个进一步原因。

表III. 具有固定gm/Ids (8V-1)和W值的两级运算跨导放大器:晶体管尺寸设计。

| 线-TFET | MOS 65nm | MOS 130纳米 | MOS 130纳米 (栅极长度=1μm) | |

|---|---|---|---|---|

| W1-2 (nm) | 150 | 150 | 300 | 345 |

| W3-4 (nm) | 150 | 150 | 300 | 630 |

| 宽度5/bias (nm) | 300 | 1.5μm | 4.5μm | 2.7μm |

| W6 (μm) | 15.8 | |||

| W7 (μm) | 1.5 | 6 |

表IV. 具有固定跨导与漏源电流比(8V-1)和宽度值的两级运算跨导放大器:设计结果。

| 器件 | 线-TFET | MOS 65nm | MOS 130纳米 | MOS 130纳米 (栅极长度=1 μm) |

|---|---|---|---|---|

| Ids/W (微安/微米) | 0.6 | 35 | 35 | 5 |

| Vdd (伏) | 2.5 | 1.2 | 1.2 | 1.2 |

| 总电流 (µA) | 1.275 | 75 | 21 | 32.5 |

| 功率 (µW) | 3.2 | 90 | 25.2 | 39 |

| 输出摆幅 (峰峰值电压) | 1.4 | 0.725 | 0.75 | 0.7 |

| Rout (欧姆) | 80M | 10k | 68k | 242k |

| 电压增益(分贝) | 110 | 28 | 40 | 66 |

| CMRR (dB) | 116 | 34 | 46 | 72 |

| fc3dB (Hz) | 20 | 10M | 2M | 18k |

| GBW (Hz) | 5.5M | 240M | 180M | 32M |

2) 采用固定的Ids/W和W的设计

为了比较采用MOSFET和线隧穿场效应晶体管技术的两级运算跨导放大器设计,在与表III相同的宽度和相同归一化电流条件下,该值被设置为Ids/W=2μA/μm。此电流水平使线‐TFET器件工作于强反型区,gm/Ids=5.2V-1,而MOSFET器件则几乎工作于弱反型区,其中65纳米和130纳米栅极长度下的gm/Ids接近20 V-1 。图13和表五展示了该设计的结果。

由于相同的电流水平,所有设计的增益带宽积(GBW)相似,但MOSFET设计因其更高的晶体管效率而略大。由于线隧穿场效应晶体管(Line‐TFET)的反型程度相较于前一节略有增加,其增益带宽积(GBW)从5.5兆赫提升至8.5兆赫,而对于MOSFET的65纳米、130纳米和1微米设计,该值分别由于反型程度远小于前一节,电流水平降低了10倍、6倍和3倍。同样由于与前一节相比反型程度发生变化,线隧穿场效应晶体管的输出电阻和输出摆幅下降,而金属氧化物半导体场效应晶体管的这两个值则上升。本节中所有设计的功耗现在均相近,因为电流水平保持相同(出于稳定性考虑,130纳米 Lg=1μm 设计除外),从而导致高频性能相似。尽管金属氧化物半导体场效应晶体管设计由于反型程度降低而使其电压增益和共模抑制比提高,但与线隧穿场效应晶体管设计相比仍至少有40分贝的降低。

表五. 漏极电流/宽度(Ids/W)固定为2微安/微米且宽度W值固定的两级运算跨导放大器设计结果。

| 器件 | 线-TFET | MOS 65nm | MOS 130纳米 | MOS 130纳米 (Lg=1μm) |

|---|---|---|---|---|

| 跨导与漏源电流比 (V-1) | 5.2 | 18 | 19 | 11 |

| Vdd (伏) | 2.5 | 1.2 | 1.2 | 1.2 |

| 总电流 (µA) | 3.6 | 3.6 | 3.6 | 12.6 |

| 功率 (µW) | 9 | 4.3 | 4.3 | 15.1 |

| 输出摆幅 (峰峰值电压) | 1.3 | 0.825 | 0.9 | 0.875 |

| Rout (欧姆) | 28M | 80k | 550k | 925k |

| 电压增益(分贝) | 115 | 32 | 42 | 74 |

| CMRR (dB) | 121 | 38 | 48 | 80 |

| fc 3dB (Hz) | 18 | 560k | 250k | 2.8k |

| GBW (Hz) | 8.5M | 24M | 31M | 13M |

3) 超低功耗,低频纳米设计

在之前的设计中,线隧穿场效应晶体管器件工作在强反型区并采用最大栅极偏置。为了最大化电流水平、动态操作性能,并在相似性能条件下与MOSFET技术进行比较,需优化栅极长度。然而,线隧穿场效应晶体管(Line‐TFET)具有在纳米器件中实现极高电压增益的潜力,可在低频下以超低功耗最小化电路面积。这些特性适用于生物信号采集等应用,此类应用需要将低于1赫兹到数百千赫兹的信号进行高精度放大(因而需要高开环电压增益),同时消耗最小的功耗和电路面积[4][18][19]。表VI和图14分别描绘了某项设计的部分性能指标及其波特图,该设计采用栅极长度为100纳米的晶体管,在中等反型至亚阈值区过渡区域偏置,晶体管效率为12伏特-1。

表VI. 采用100纳米栅极长度的线隧穿场效应晶体管的两级运算跨导放大器:设计结果与晶体管尺寸设计。

| 器件 | 线隧穿场效应晶体管 Lg=100nm | 线隧穿场效应晶体管 Lg=100nm | 线隧穿场效应晶体管 Lg=100nm |

|---|---|---|---|

| Ids/W (纳安/微米) | 7.5 | 跨导与漏源电流比 (V-1) | 12 |

| Vdd (伏) | 1.8 | ||

| 总电流 (nA) | 10 | W1-2 | 100纳米 |

| 功率 (nW) | 18 | W3-4 | 100纳米 |

| 输出摆幅 (峰峰值电压) | 1.1 | W5/bias | 200纳米 |

| Rout (欧姆) | 470M | W6 | 1µm |

| 电压增益(分贝) | 71 | W7 | 1µm |

| CMRR (dB) | 77 | ||

| fc3dB (Hz) | 10 | ||

| GBW (Hz) | 50k |

反型程度的降低使得电源电压Vdd可降至1.8伏特,从而降低了功耗,并提供了与更先进的MOS技术兼容的可能性。栅极长度的缩短导致跨导gm减小,进而使增益带宽积 GBW(由于跨导与漏源电流比gm/Ids的降低而已经减小)和电压增益Av分别降至约50千赫兹和71分贝。有趣的是,由于输出电阻Rout未受到栅极长度缩短的影响,fc 3dB 几乎保持不变,仅因反型程度降低导致Rout升高至约470兆欧姆,从而使fc略微降低至10赫兹。此外,由于晶体管效率的提高,即使在Vdd降低的情况下,输出摆幅仍保持在1Vpp以上。该设计采用非常简单的放大器拓扑结构,栅极面积仅为0.01平方微米到0.1平方微米,实现了仅18纳瓦的功耗和71分贝的开环电压增益,同时具有77分贝的高共模抑制比。

C. 两级运算跨导放大器:与其他TFET设计的比较

表七将本研究中的首尾两个设计与其他基于TFET的放大器设计进行了比较。由于会降低弱反型区性能的非理想性,必须使用较高的供电电压,即源漏隧穿和带间隧穿。需要注意的是,其他设计采用了仿真器件,并忽略了亚阈值工作区的一些非理想性,从而实现了极低的偏置电压。尽管如此,功耗仍然非常低,但第一个采用线隧穿场效应晶体管的设计由于这些器件的电流水平较高、反型程度更高以及本设计所采用的设计约束(如gm/Ids和电流预算值),导致其功耗相对较高,同时也带来了更高的性能。由于采用了两级拓扑结构,本研究还实现了更高的开环电压增益,尽管其他研究使用了共源共栅结构来提升增益。

表七。与其他采用TFET的放大器设计的比较

| 本工作 | 本工作 | [5] | [4] | [3] | |

|---|---|---|---|---|---|

| TFET 器件 | 锗硅线隧穿场效应晶体管 | 锗硅线隧穿场效应晶体管 | 三五族双栅 | 三五族双栅 | SiGe 垂直 |

| 拓扑结构 | 两级 | 两级 | 折叠 共源共栅 | 望远镜式 共源共栅 | One- 级 |

| Vdd | 2.5V | 1.8V | 0.43伏特 | 0.5V | 1V |

| 总电流 | 1.275微安 | 10纳安 | 216纳安 | 10nA | 3.6纳安 |

| 功率 | 3.2微瓦 | 18纳瓦 | 93nW | 5nW | 3.6纳瓦 |

| Av | 110分贝 | 71dB | 63dB | 50dB | 27.7分贝 |

IV. 结论

本工作提出利用线隧穿场效应晶体管(Line‐TFET)器件进行信号放大,因其具有极高的本征增益、低功耗以及相对良好的性能,并且对温度变化和噪声具有较强的抗性(这两方面在本工作中未涉及)。对Line‐TFET器件级别模拟特性的研究以及所进行的电路实现均基于实验器件数据。该方法旨在获得所设计电路更真实的性能指标,为模拟电路设计者提供指导,考虑了若干在使用仿真器件时可能被低估甚至完全忽略的非理想性,同时强调了器件级别可能的优化方向,以用于未来采用Line‐TFET制造模拟电路。

在器件级别上,已表明Line‐TFET如何实现比大多数点TFET更高的性能(III‐V族TFET除外),其归一化漏极电流高达10μA/μm,但由于带间隧穿和源极到漏极隧穿,需要更高的电源电压。此外,研究表明该器件可实现高达60分贝的极高本征电压增益,同时具有可接受的动态性能,单位增益频率高达500兆赫兹。进一步研究了Line‐TFET的饱和特性,以更好地理解源极到漏极泄漏隧穿所起的作用。该研究揭示了这种隧穿不仅限制了偏置电压和最小栅极面积,还解释了为什么输出电导与栅极长度无关,这一点最初是在实验中观察到的。它还深化了对已有饱和特性的认识,表明输出电导并非如先前认为的那样渐近减小,而在深度饱和时最终上升。

设计了一个采用电流源负载的共源极电路,旨在说明栅极长度对输出电导gd的独立性对模拟电路设计的影响。使用MOSFET技术,为了提高电路电压增益,必须增加栅极长度以提高输出电阻。对于线隧穿场效应晶体管,设计者也需要增加栅极长度,但可以选择在保持电路面积不变的情况下增加输出电阻,或在增加栅极长度时保持宽度不变以提高跨导。

为了在类似性能条件下对电路进行基准测试,设计了一款两级OTA,以比较线隧穿场效应晶体管与MOSFET技术。结果表明,由于电流密度较低,线隧穿场效应晶体管适用于低功耗、低性能的应用场景;但无论何种情况,其开环电压增益均极高,最高可达115分贝,比栅极长度为Lg=1μm的MOSFET设计高出40分贝。基于这些特性,采用栅极长度为100纳米的线隧穿场效应晶体管设计了一款超低功耗运算跨导放大器,其实现的功耗为18纳瓦,电压增益Av=71分贝,这对于需要高增益、低功耗和最小电路面积的生物信号采集等低频应用具有重要意义。本设计还讨论了由于输出电导gd不随栅极长度Lg变化,3dB截止频率几乎保持不变的情况。由于采用了两级拓扑结构,该设计实现了比其他基于隧穿场效应晶体管的放大器设计更高的开环电压增益。尽管由于非理想性导致亚阈值工作区性能退化而需要更高的供电电压,但与其他隧穿场效应晶体管设计相比仍获得了相似的功耗水平。

基于Line-TFET的低功耗放大器设计

基于Line-TFET的低功耗放大器设计

438

438

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?