基于隧穿场效应晶体管的超低功耗和硬件安全电路设计考虑 p‐i‐n正向漏电流

1 | 引言

隧穿场效应晶体管(TFETs)已成为未来低能耗电子电路设计中一种有前景的器件候选者。1,2 TFET表现出陡峭的亚阈值斜率,因其带间隧穿机制而实现更高的开态与关态电流比。3,4近年来,已提出多种TFET器件结构,以在实现亚60 mV/dec开关操作的同时获得高开态电流。5-8其中,硅基TFET由于其成熟的制造工艺已被证明是理想的器件,但其开态电流较低。5,6研究人员的研究表明,III‐V族TFET由于所用材料具有更小的带隙,因而能够实现更高的开态电流。7,8在最近的实验演示中,III‐V族TFET在0.5 V的电源电压(VDD)下实现了 92 μA/μm的开态电流,并具有48 mV/dec亚阈值摆幅9。凭借高开态与关态电流比和更低的亚阈值摆幅,TFET数字电路实现了超低功耗和高能效。10,11然而,TFET表现出一些特殊的电学特性,如双极性和单向电流导通。12,13 TFET中的双极性被视为一个严重挑战,已有多种器件级优化技术被用于降低双极性漏电流。14,15最近有实验报道指出,TFET表现出显著的 p‐i‐n泄漏,导致基于TFET的电路发生故障,且该现象并非由TFET器件中的双极性漏电流引起。16,17文献中通常忽略p‐i‐n正向漏电流所带来的影响,且尚未深入探讨减少其影响的方法或技术。17,18本文提出了用于减轻TFET p‐i‐n正向漏电流影响的电路技术。

同时,集成电路设计与制造的全球化带来了硬件安全威胁,例如硬件木马、侧信道分析以及集成电路逆向工程(RE)。19-21面向硬件的安全利用新型互补金属氧化物半导体(CMOS)为基础的安全原语,如真随机数发生器(TRNGs)、物理不可克隆功能以及其他电路设计方法,使系统能够有效抵御安全攻击。22-24然而,基于CMOS的安全原语功耗和面积开销较高,并需要额外的源/漏掺杂变化来实现用于混淆的隐蔽操作。25-27为了克服CMOS的局限性,研究人员正在探索利用新兴器件的固有独特特性来提升硬件安全。28-30TFET器件的重要性引起了设计人员的关注,使其专门探索该器件特性在硬件安全应用中的潜力。31-33早期已设计出低成本基于TFET的多态逻辑电路,以避免知识产权克隆。31随后,提出了TFET电流模式逻辑,以在实现更低功耗的同时提高差分功率分析抗性。32最近,TFET双极性也被探索用于增强硬件安全。33考虑到TFET器件的局限性与应用前景,本文提出电路技术以最小化 TFET p‐i‐n正向漏电流的影响。除此之外,还利用TFET固有的p‐i‐n正向漏电流来增强硬件安全。

本文其余部分组织如下。第2节介绍了TFET器件特性以及TFET p‐i‐n正向漏电流对基于传输门(TG)的数字电路设计的影响。第3节展示了在TFET数字电路中降低正向漏电流效应的电路技术。第4节利用TFET p‐i‐n正向漏电流生成多种功能,用于硬件混淆应用以及优化硬件密码原语。最后,第5节给出了结论。

2 | TFET器件特性及显著泄漏电流的演示

本节介绍了在设计TFET Verilog‐A模型时所研究的TFET器件结构和参数。通过能带图展示了TFET在不同区域的工作特性,并讨论了描述各种漏电流分量的特征。此外,本节还演示了p‐i‐n正向漏电流对基于TFET TG的数字电路的影响。

2.1 | 器件结构与模型

近年来,研究人员提出了多种具有不同结构和材料的TFETs。其中,III‐V族TFETs因其高开态电流和更低的亚阈值摆幅值而受到广泛关注。本文研究了一种沟道长度为L = 20nm的通用解析双栅InAs TFET Verilog‐A模型,用于TFET电路设计。

展示了该TFET的物理结构。这些模型已被集成到工业标准HSPICE环境中,在工作区中实现并仿真了电路网表。该TFET模型基于Kane‐Sze公式计算隧穿效应,能够捕捉TFET器件的重要特性,如偏压相关的亚阈值摆幅、超线性漏极电流起始、双极型导电以及负微分电阻。InAs TFET模型所用的器件参数如表1所示。

展示了该TFET的物理结构。这些模型已被集成到工业标准HSPICE环境中,在工作区中实现并仿真了电路网表。该TFET模型基于Kane‐Sze公式计算隧穿效应,能够捕捉TFET器件的重要特性,如偏压相关的亚阈值摆幅、超线性漏极电流起始、双极型导电以及负微分电阻。InAs TFET模型所用的器件参数如表1所示。

关于所研究的InAs TFET的器件结构、参数、等效模型、掺杂浓度以及C‐V特性的更多细节可参见卢等人36和阿夫奇等人[36]。

2.2 | 隧穿场效应晶体管在不同区域的行为

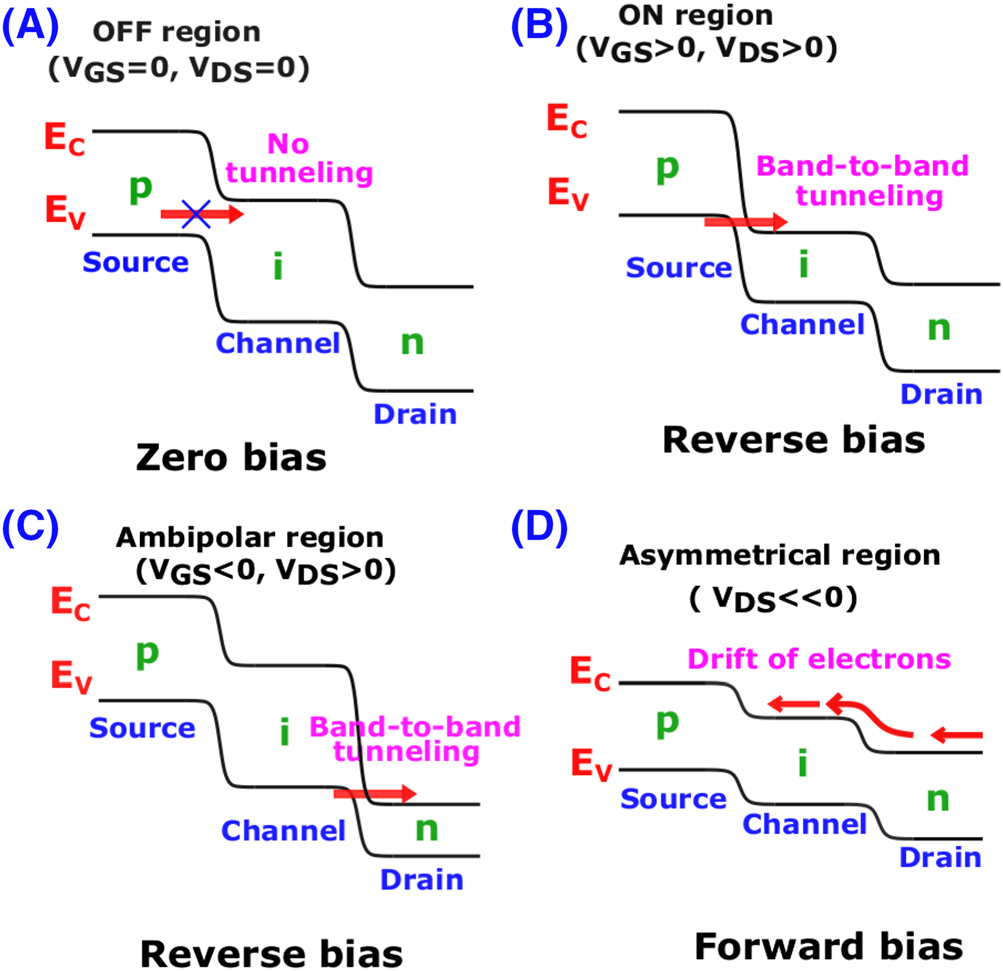

本节通过能带图解释了隧穿场效应晶体管(TFET)的工作特性。通过将栅极到源极电压(VGS)和栅极到漏极电压(VDS)从负电压调节至正电压,n型通道隧穿场效应晶体管(NTFET)可以在不同状态下工作。

展示了NTFET在四个不同区域中的能带图。当VGS为零时,沟道的导带位于源极的价带之上,如图2A所示。由于这一原因,器件中不发生隧穿,TFET处于关断状态。当VGS> 0、VDS> 0时,源极与沟道中的能带对齐,如图2B所示。因此,在p‐i‐n结构反向偏置下的TFET表现出从源极到沟道的带间隧穿,且导通由栅极电压控制。在此区域中,TFET导通。

展示了NTFET在四个不同区域中的能带图。当VGS为零时,沟道的导带位于源极的价带之上,如图2A所示。由于这一原因,器件中不发生隧穿,TFET处于关断状态。当VGS> 0、VDS> 0时,源极与沟道中的能带对齐,如图2B所示。因此,在p‐i‐n结构反向偏置下的TFET表现出从源极到沟道的带间隧穿,且导通由栅极电压控制。在此区域中,TFET导通。

当VGS< 0、VDS> 0时,漏极和沟道中的能带对齐,如图2C所示。因此,隧穿场效应晶体管出现从沟道到漏极的带间隧穿,该导通电流称为双极性电流。当VDS<< 0时,TFET的p‐i‐n 器件结构处于正向偏置状态。在此区域中,TFET表现为一个普通的p‐n二极管,载流子由于漂移运动而从漏极流向源极,而非带间隧穿,如图2D所示。这导致TFETs中产生p‐i‐n正向电流,其流动方向与传统开态电流相反(从源极到漏极)。该电流几乎无法通过栅极电压进行控制,且高度依赖于VDS。

2.3 | 隧穿场效应晶体管双极性漏电流

当施加正的VGS和VDS电压时,由于源极‐沟道结处发生带间隧穿,TFET器件导通。当VGS变为负值时,隧穿结从源极‐沟道结转移到漏极‐沟道结,导致双极性电流从漏极流向源极。

显示了n型通道隧穿场效应晶体管(NTFET)在VDS=0为4V,VGS从‐0.4V变化到0.4V时的ID‐VGS特性。由此可以观察到,当器件处于关断状态时存在双极性电流。在VGS=为‐0.4V时,NTFET表现出0.1μA/μm的双极性电流。NTFET和PTFET分别在VGS为负值和正值时进入双极性工作区。

显示了n型通道隧穿场效应晶体管(NTFET)在VDS=0为4V,VGS从‐0.4V变化到0.4V时的ID‐VGS特性。由此可以观察到,当器件处于关断状态时存在双极性电流。在VGS=为‐0.4V时,NTFET表现出0.1μA/μm的双极性电流。NTFET和PTFET分别在VGS为负值和正值时进入双极性工作区。

2.4 | TFET p‐i‐n正向漏电流

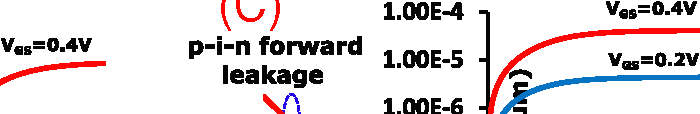

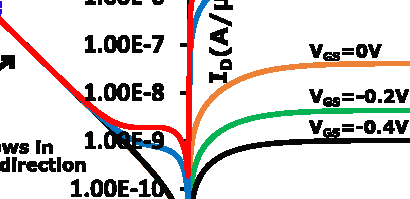

展示了NTFET的ID‐VDS特性,显示出在负VDS条件下存在显著漏电流传输,而非单向电流导通。当施加正 VDS时,NTFET表现出理想的晶体管行为,并具有高导通电流。在负VDS条件下,砷化铟隧穿场效应晶体管表现出显著的漏电流(p‐i‐n正向漏电流),这是由于p‐i‐n器件结构的正向偏置所致。可以观察到,随着VDS变得更负,漏电流出现急剧增加。在VDS= −0.4伏时,NTFET在反向(即源极到漏极)表现出 2 μA/μm的漏电流。较低至中等幅度的负VDS (−0.2至 −0.4伏)会产生显著漏电流(与导通电流相比偏低),且几乎不受栅极电压控制。从图3B,C可以看出,通过将栅极电压从 −0.4伏变化到0.4伏,TFET表现出相似量级的p‐i‐n正向电流。这表明,随着VDS变得更负(由于p‐i‐n结构的正向偏置),栅极对沟道失去控制,电流仅由VDS控制。从图3A,C可推断出,p‐i‐n正向漏电流的幅度高于双极性漏电流。因此,p‐i‐n正向漏电流是一个严重问题,会增加TFET电路功耗并降低可靠性。本文提出了一些电路技术,如新型紧凑型门电路和三态门,以减少漏电影响。此外,作者还利用p‐i‐n正向漏电流特性来设计电路,以增强硬件安全性。

展示了NTFET的ID‐VDS特性,显示出在负VDS条件下存在显著漏电流传输,而非单向电流导通。当施加正 VDS时,NTFET表现出理想的晶体管行为,并具有高导通电流。在负VDS条件下,砷化铟隧穿场效应晶体管表现出显著的漏电流(p‐i‐n正向漏电流),这是由于p‐i‐n器件结构的正向偏置所致。可以观察到,随着VDS变得更负,漏电流出现急剧增加。在VDS= −0.4伏时,NTFET在反向(即源极到漏极)表现出 2 μA/μm的漏电流。较低至中等幅度的负VDS (−0.2至 −0.4伏)会产生显著漏电流(与导通电流相比偏低),且几乎不受栅极电压控制。从图3B,C可以看出,通过将栅极电压从 −0.4伏变化到0.4伏,TFET表现出相似量级的p‐i‐n正向电流。这表明,随着VDS变得更负(由于p‐i‐n结构的正向偏置),栅极对沟道失去控制,电流仅由VDS控制。从图3A,C可推断出,p‐i‐n正向漏电流的幅度高于双极性漏电流。因此,p‐i‐n正向漏电流是一个严重问题,会增加TFET电路功耗并降低可靠性。本文提出了一些电路技术,如新型紧凑型门电路和三态门,以减少漏电影响。此外,作者还利用p‐i‐n正向漏电流特性来设计电路,以增强硬件安全性。

2.5 | p‐i‐n 正向漏电流对TFET传输门/开关的影响

TG 是一种开关,通过选择控制信号可使输入信号传递到输出端,可用于构建多种数字电路。为了展示 p‐i‐n 正向漏电流的影响,对 TFET TG 的功能进行了考察。

展示了 TFET TG 在不同情况下的开和关切换。在图4A中,假设使能信号En 处于逻辑“1”,Enb处于逻辑“0”,负载电容(CL)已完全充电至 VDD。如果输入(Vin)为逻辑 “0”,则 NTFET 的 VGS 和 VDS 将大于零,使 NTFET 处于导通状态,从而将输出端的负载电容 CL 放电至 0 V。类似地,在图4B中,当输入为逻辑“1”时,电容充电至 VDD 。另一方面,在图4C中,假设En输入为逻辑“0”,Enb为逻辑“1”,且CL已完全充电至VDD。如果输入Vin为逻辑“0”,则 PTFET的VGS和VDS大于零,NTFET的VGS为零,在该区域中,传输门中的两个晶体管通常均处于关断状态。但由于PTFET的p‐i‐n结构发生正向偏置,会产生显著的正向漏电流,导致负载电容通过PTFET放电,这是不希望出现的现象,并会引起功耗显著增加。类似地,在图4D中,当输入为逻辑“1”时,电容充电。

展示了 TFET TG 在不同情况下的开和关切换。在图4A中,假设使能信号En 处于逻辑“1”,Enb处于逻辑“0”,负载电容(CL)已完全充电至 VDD。如果输入(Vin)为逻辑 “0”,则 NTFET 的 VGS 和 VDS 将大于零,使 NTFET 处于导通状态,从而将输出端的负载电容 CL 放电至 0 V。类似地,在图4B中,当输入为逻辑“1”时,电容充电至 VDD 。另一方面,在图4C中,假设En输入为逻辑“0”,Enb为逻辑“1”,且CL已完全充电至VDD。如果输入Vin为逻辑“0”,则 PTFET的VGS和VDS大于零,NTFET的VGS为零,在该区域中,传输门中的两个晶体管通常均处于关断状态。但由于PTFET的p‐i‐n结构发生正向偏置,会产生显著的正向漏电流,导致负载电容通过PTFET放电,这是不希望出现的现象,并会引起功耗显著增加。类似地,在图4D中,当输入为逻辑“1”时,电容充电。

显示了在0.4V供电电压下,驱动负载电容CL的基于TFET的传输门设计的仿真设置。使用静态TFET反相器来吸收/提供负载电容所需的电流。图5B描绘了在0.4V供电电压下,TFET传输门驱动10飞法负载电容的仿真响应。

显示了在0.4V供电电压下,驱动负载电容CL的基于TFET的传输门设计的仿真设置。使用静态TFET反相器来吸收/提供负载电容所需的电流。图5B描绘了在0.4V供电电压下,TFET传输门驱动10飞法负载电容的仿真响应。

当使能信号En为逻辑“1”且Enb为逻辑“0”时,传输门导通,输出Vout将为输入信号的反相。如果使能信号En 为逻辑“0”且Enb为逻辑“1”,由于TFET器件中存在显著漏电流,传输门部分导通,导致输出根据所加输入信号发生充电/放电现象。从图5B可以看出,由于显著的p‐i‐n泄漏,TFET传输门表现出非传统的行为。

2.6 | TFET p‐i‐n正向漏电流对基于传输门电路设计的影响

基于TFET传输门的电路由于器件的正向漏电流而表现出高功耗和可靠性差。通常,基于传输门的多路复用器(MUX)设计与基于TFET静态互补门的MUX设计相比具有较低的功耗。但由于TFET p‐i‐n正向漏电流,TFET传输门MUX工作时功耗较高,并表现出逻辑摆幅退化。

分别显示了使用静态互补NAND和传输门逻辑实现的TFET MUX。图6C显示了在0.4V供电电压下两种MUX设计的瞬态特性。可以观察到,TFET MUX设计出现逻辑摆幅退化,而静态互补MUX则完全正常工作并恢复了逻辑摆幅。从图6D可以看出,在0.4V供电电压下,TFET传输门MUX的功耗~6×大于基于静态互补NAND的MUX。因此,应避免p‐i‐n正向漏电流效应,以利用TFET器件实现高性能和超低功耗。

分别显示了使用静态互补NAND和传输门逻辑实现的TFET MUX。图6C显示了在0.4V供电电压下两种MUX设计的瞬态特性。可以观察到,TFET MUX设计出现逻辑摆幅退化,而静态互补MUX则完全正常工作并恢复了逻辑摆幅。从图6D可以看出,在0.4V供电电压下,TFET传输门MUX的功耗~6×大于基于静态互补NAND的MUX。因此,应避免p‐i‐n正向漏电流效应,以利用TFET器件实现高性能和超低功耗。

3 | TFET电路设计以抑制泄漏效应

本节提出了新型电路技术,以缓解p‐i‐n泄漏效应对基于TFET的数字电路的影响。提出TFET新型紧凑型门以实现低功耗和高可靠性。此外,还建议采用三态逻辑来避免TFET数字电路设计中的漏电流效应。

3.1 | 新型紧凑型栅极

CMOS传输门得益于PMOS和NMOS的导通。但在TFET传输门中,由于其不对称特性,只有NTFET或PTFET导通。18因此,TFET传输门的传播延迟增加。TFET传输门在其关断状态对p‐i‐n正向漏电流高度敏感。这会增加TFET电路功耗并降低可靠性,如第1节所述。为了提升性能,本文提出了以下针对基于TFET传输门的电路的建议,以最小化漏电流效应。

- 在设计电路时,尽可能应用固定电压(VDD或地)。

- 避免在电路中使用传输门/开关(从传播延迟角度看并无额外优势),因为它对器件漏电非常敏感。

根据上述建议,基于TFET传输门的电路可以进行如下修改。例如,考虑使用两个传输门实现的TFET传输门 AND逻辑,如

所示。在不改变TG AND逻辑功能的前提下,可将上部传输门的源极端子固定接地,如图7B所示。由于NTFET已足以传递逻辑“0”,且从传播延迟角度看并无额外优势,因此T1晶体管可以省略。这样便可去除上部传输门,从而降低电路对器件漏电的敏感性。最终得到的AND逻辑仅包含五个晶体管,对器件漏电具有较强的鲁棒性,如图7C所示。类似地,OR逻辑可按图7D所示方式进行修改。图7E展示了一个产生逻辑(AB + C)的三输入门,该门由TFET传输门实现,并由此衍生出一种新型紧凑门(如图7F所示)。传输门逻辑实现“AB + C”逻辑需要12个晶体管,而新型紧凑门仅需10个晶体管即可实现。

所示。在不改变TG AND逻辑功能的前提下,可将上部传输门的源极端子固定接地,如图7B所示。由于NTFET已足以传递逻辑“0”,且从传播延迟角度看并无额外优势,因此T1晶体管可以省略。这样便可去除上部传输门,从而降低电路对器件漏电的敏感性。最终得到的AND逻辑仅包含五个晶体管,对器件漏电具有较强的鲁棒性,如图7C所示。类似地,OR逻辑可按图7D所示方式进行修改。图7E展示了一个产生逻辑(AB + C)的三输入门,该门由TFET传输门实现,并由此衍生出一种新型紧凑门(如图7F所示)。传输门逻辑实现“AB + C”逻辑需要12个晶体管,而新型紧凑门仅需10个晶体管即可实现。

为了说明TFET TG和新型紧凑门的功能,以

)所示的AND逻辑为例。图8A展示了TFET传输门AND门,当输入A为逻辑“1”、B为逻辑“0”时,晶体管T3和T4导通(图8A中的下部传输门),AND门的输出变为逻辑“0”。同时,晶体管T1和T2必须处于关断状态(图8A中的上部传输门)。然而,当VDS (对于T1和T2)以及VGS (T2)变为负值时,上部传输门会产生p‐i‐n正向漏电流,该电流会缓慢地对输出端子(Y)充电。这将导致输出端的逻辑“0”电平下降,从而降低门的逻辑摆幅,进而恶化低电平噪声容限。图8B展示了新型紧凑型AND门,当输入A为逻辑“1”、B为逻辑“0”时,晶体管T4导通,输出变为逻辑“0”。同时,晶体管T2的偏置电压VDS和VGS为零,在这些偏置电压下不会产生漏电流。因此,提出的改进措施使新型紧凑型AND门对器件漏电具有更强的鲁棒性。结果表明,与传统的基于传输门的AND逻辑相比,新型紧凑型AND逻辑在第3.3节中表现出更低的功耗和更高的可靠性。

)所示的AND逻辑为例。图8A展示了TFET传输门AND门,当输入A为逻辑“1”、B为逻辑“0”时,晶体管T3和T4导通(图8A中的下部传输门),AND门的输出变为逻辑“0”。同时,晶体管T1和T2必须处于关断状态(图8A中的上部传输门)。然而,当VDS (对于T1和T2)以及VGS (T2)变为负值时,上部传输门会产生p‐i‐n正向漏电流,该电流会缓慢地对输出端子(Y)充电。这将导致输出端的逻辑“0”电平下降,从而降低门的逻辑摆幅,进而恶化低电平噪声容限。图8B展示了新型紧凑型AND门,当输入A为逻辑“1”、B为逻辑“0”时,晶体管T4导通,输出变为逻辑“0”。同时,晶体管T2的偏置电压VDS和VGS为零,在这些偏置电压下不会产生漏电流。因此,提出的改进措施使新型紧凑型AND门对器件漏电具有更强的鲁棒性。结果表明,与传统的基于传输门的AND逻辑相比,新型紧凑型AND逻辑在第3.3节中表现出更低的功耗和更高的可靠性。

3.2 | 三态门

另一种抑制漏电流效应的方法是使用三态门,如下所示。首先,TFET三态逻辑避免了双向电流导通机制(如传输门逻辑中的情况)。其次,PTFET和NTFET的源极端子分别固定在VDD和地,从而抑制了漏电流效应。图8C展示了在类似输入情况下三态AND门的工作状态。当输入A为逻辑“1”、输入B为逻辑“0”时,晶体管T5和T6导通(图8C中的右侧三态门),与门的输出变为逻辑“0”。同时,晶体管T1,、T2,、T7,和T8关断。晶体管T4也导通,且无正向漏电流流过。因此,通过使用三态逻辑的电路相互作用可以控制器件的漏电流,在与其他拓扑结构相比时表现出高能效,但存在额外的面积开销。

3.3 | 结果与分析

对采用第3.1节和第3.2节中介绍的三种不同拓扑结构实现的逻辑门的总功耗和噪声容限进行了分析。在电源电压 0.4和0.3V下,将TFET新型紧凑型门和三态门与TFET传输门设计进行了对比。

3.3.1 | 功耗

从

可以看出,在0.4V电源电压下,基于三态逻辑的两输入与门和或门相比传输门逻辑功耗降低了 6× 。还可以观察到,新型紧凑型逻辑相比基于传输门的设计功耗降低了 2×。类似地,基于隧穿场效应晶体管的新型紧凑型三输入逻辑(“A + BC”)相比传输门逻辑功耗降低了 2×。由于三态逻辑的静态拓扑结构,它具有与所有考虑的逻辑拓扑结构相比,该设计对漏电流效应具有较强的鲁棒性,并实现了低功耗,但增加了面积开销。

可以看出,在0.4V电源电压下,基于三态逻辑的两输入与门和或门相比传输门逻辑功耗降低了 6× 。还可以观察到,新型紧凑型逻辑相比基于传输门的设计功耗降低了 2×。类似地,基于隧穿场效应晶体管的新型紧凑型三输入逻辑(“A + BC”)相比传输门逻辑功耗降低了 2×。由于三态逻辑的静态拓扑结构,它具有与所有考虑的逻辑拓扑结构相比,该设计对漏电流效应具有较强的鲁棒性,并实现了低功耗,但增加了面积开销。

通过使用两输入与门和或逻辑门,实现了四输入逻辑门(树形结构)并进行了研究。图9B显示了三种拓扑结构下四输入与门、或门的功耗。TFET中的漏电流导致传输门在关断时发生反向传播。由于这一原因,四输入与门和或门相较于其他考虑的拓扑结构表现出较大的功耗。

3.3.2 | 逻辑摆幅和噪声容限

显示了在三种不同拓扑结构中实现的逻辑门的电压传输特性。可以观察到,由于TFET存在较大的漏电流,导致传输门逻辑的输出逻辑摆幅下降,而三态逻辑则表现出更好的性能。还可以观察到,与传输门逻辑相比,新型紧凑型门电路具有更优的逻辑摆幅。在0.4伏供电电压下计算了三种不同拓扑结构或门的噪声容限(NML、NMH)。从表2可以看出,基于TFET传输门的两输入或门与其他逻辑门相比,NML和NMH较低。这是由于传输门中的 p‐i‐n正向漏电流降低了输出逻辑电平,从而影响了门电路的噪声容限。另一方面,TFET新型紧凑型OR门在减小漏电效应的同时,噪声容限得到改善。具有高噪声容限的TFET三态逻辑表现出较强的鲁棒性漏电流影响下的性能。还可以观察到,三输入和四输入门电路也表现出类似的性能,如表2所总结的那样。

显示了在三种不同拓扑结构中实现的逻辑门的电压传输特性。可以观察到,由于TFET存在较大的漏电流,导致传输门逻辑的输出逻辑摆幅下降,而三态逻辑则表现出更好的性能。还可以观察到,与传输门逻辑相比,新型紧凑型门电路具有更优的逻辑摆幅。在0.4伏供电电压下计算了三种不同拓扑结构或门的噪声容限(NML、NMH)。从表2可以看出,基于TFET传输门的两输入或门与其他逻辑门相比,NML和NMH较低。这是由于传输门中的 p‐i‐n正向漏电流降低了输出逻辑电平,从而影响了门电路的噪声容限。另一方面,TFET新型紧凑型OR门在减小漏电效应的同时,噪声容限得到改善。具有高噪声容限的TFET三态逻辑表现出较强的鲁棒性漏电流影响下的性能。还可以观察到,三输入和四输入门电路也表现出类似的性能,如表2所总结的那样。

| 拓扑结构 | 两输入或门 | 三输入 AB+ C | 四输入或门 | |||

|---|---|---|---|---|---|---|

| NM L | NM H | NM L | NM H | NM L | NM H | |

| 传输门 | 0.173 | 0.164 | 0.161 | 0.162 | 0.161 | 0.16 |

| 新型紧凑型 | 0.193 | 0.192 | 0.181 | 0.182 | 0.181 | 0.18 |

| 三态门 | 0.197 | 0.197 | 0.196 | 0.197 | 0.195 | 0.196 |

| ## 4 | 利用TFET p‐i‐n正向泄漏实现硬件安全 |

本节介绍了探索隧穿场效应晶体管p‐i‐n正向漏电流在硬件安全应用中的方法。利用TFET传输门功能失效实现硬件混淆,该行为也被用于优化真随机数发生器等硬件安全原语。

4.1 | 利用TFET p‐i‐n正向漏电流实现器件级硬件混淆

由于TFET表现出显著的p‐i‐n正向漏电流而非单向电流导通,导致TFET传输门(TG)出现非正常行为。因此,如第2节所述,基于传输门的数字电路的功耗和能耗增加。除了这些挑战之外,本文还探索了利用TFET传输门功能失效实现硬件混淆的方法。例如,采用主从结构的动态正边沿触发触发器37来演示硬件混淆。

展示了使用传输门、三态门以及两者组合构成的混淆的触发器电路。在p‐i‐n正向漏电流的影响下,即使处于关断状态,TFET传输门也会部分导通。利用这一特性,这些触发器拓扑结构呈现出不同的功能行为。在正常情况下,图11A‐D中的触发器表现相似,因为所有触发器结构在逻辑上被认为是相同的。然而,在TFET正向漏电流影响下,每个触发器中的 TFET传输门表现出不同的行为,导致触发器实现不同的功能。表3总结了在TFET p‐i‐n正向漏电流影响下混淆的触发器的行为。这意味着,尽管电路架构在逻辑上看似相同,但其原始功能存在差异,这对攻击者而言并不明显。图11所示触发器的功能具体解释如下。

展示了使用传输门、三态门以及两者组合构成的混淆的触发器电路。在p‐i‐n正向漏电流的影响下,即使处于关断状态,TFET传输门也会部分导通。利用这一特性,这些触发器拓扑结构呈现出不同的功能行为。在正常情况下,图11A‐D中的触发器表现相似,因为所有触发器结构在逻辑上被认为是相同的。然而,在TFET正向漏电流影响下,每个触发器中的 TFET传输门表现出不同的行为,导致触发器实现不同的功能。表3总结了在TFET p‐i‐n正向漏电流影响下混淆的触发器的行为。这意味着,尽管电路架构在逻辑上看似相同,但其原始功能存在差异,这对攻击者而言并不明显。图11所示触发器的功能具体解释如下。

4.1.1 | 正边沿触发触发器

图11A展示了基于三态门的正边沿触发触发器。当CLK =“0”时,主级中的三态门导通,输入数据在存储节点X1上被采样。在此期间,从级中的三态门关断时,输出节点(Ya)处于高阻态(保持输出端的先前值)。在CLK的上升沿,从级中的三态门导通,节点X1上采样的值将传递至输出端(Ya)。由于TFET三态门对TFET的p‐i‐n正向漏电流具有鲁棒性,触发器恢复其原始工作原理。

展示了基于三态门的触发器的仿真瞬态特性。在0.4V供电电压下,基于三态门的触发器恢复了原始操作,如图12所示(Ya)。

展示了基于三态门的触发器的仿真瞬态特性。在0.4V供电电压下,基于三态门的触发器恢复了原始操作,如图12所示(Ya)。

4.1.2 | 触发器表现为缓冲器设计

图11B展示了使用TFET传输门实现的触发器。由于TFET p‐i‐n正向漏电流的存在,处于关断状态的TFET传输门/开关也会响应所加的输入信号,如第2节所述。因此,触发器中的TFET传输门会将输入信号传递到输出端,而无论 CLK控制如何。图12显示了基于传输门的触发器的仿真瞬态特性。可以观察到,触发器的输出(Yb)与输入相同,而无论CLK控制如何。由此可以得出结论:TFET的p‐i‐n正向漏电流导致基于传输门的触发器表现为缓冲器,这一点对攻击者是明显的。

4.1.3 | 触发器表现为负锁存器

图11C展示了使用TFET三态门和传输门(TG)实现的触发器电路。当CLK =为“0”时,主级中的三态门导通,输入数据被采样到存储节点X3上。在此期间,从级中的传输门必须处于关断状态,输出(Yc)应保持之前的值。但由于传输门的功能失效,它将节点X3的数据传递到了输出端(Yc)。因此,尽管该电路看似触发器,但实际上表现为负锁存器,这种行为对攻击者是明显的。类似的特性也可以从图12所示的瞬态特性中观察到。

4.1.4 | 触发器表现为正锁存器

图11D展示了使用TFET三态门和TG实现的正边沿触发触发器。当CLK =为“1”时,从级中的三态门导通,节点 X4处采样的数据被传递到输出端(Yd)。在此期间,主级中的TG必须处于关断状态,节点X4必须保持之前的值。由于TG功能失效,无论时钟控制如何,它都会将输入数据传递到节点X4。因此,该电路表现为一种正锁存器,这对攻击者来说是显而易见的。从图12可以看出,输出(Yd)所获得的瞬态特性与正锁存器的特性相似。

混淆的触发器与组合电路集成以生成多种功能。例如,考虑

所示的电路,该电路使用了一个与门和一个混淆的触发器。在此电路中,A和B是与门的输入,C用作触发器的CLK。与门的输出连接到触发器的数据输入,输出(Y)从触发器获得,如图13A所示。图13B显示了通过部署图11中的四种不同触发器所得到的瞬态特性。仿真结果 Y1,Y2,Y3,和Y4分别通过使用图11A‐D中的不同触发器电路拓扑获得。从图13B所示的瞬态特性可以看出,通过使用四种不同的触发器,可以生成四种不同的功能。因此,可以推断,在图13A所示的电路架构中使用多个触发器,可以生成多种功能。表4总结了电路中使用的触发器数量与生成的不同功能数量之间的关系。因此,通过探索TFET的 p‐i‐n正向漏电流,可以为硬件混淆应用生成多样化功能。

所示的电路,该电路使用了一个与门和一个混淆的触发器。在此电路中,A和B是与门的输入,C用作触发器的CLK。与门的输出连接到触发器的数据输入,输出(Y)从触发器获得,如图13A所示。图13B显示了通过部署图11中的四种不同触发器所得到的瞬态特性。仿真结果 Y1,Y2,Y3,和Y4分别通过使用图11A‐D中的不同触发器电路拓扑获得。从图13B所示的瞬态特性可以看出,通过使用四种不同的触发器,可以生成四种不同的功能。因此,可以推断,在图13A所示的电路架构中使用多个触发器,可以生成多种功能。表4总结了电路中使用的触发器数量与生成的不同功能数量之间的关系。因此,通过探索TFET的 p‐i‐n正向漏电流,可以为硬件混淆应用生成多样化功能。

| 使用的触发器数量 | 生成的函数数量 |

|---|---|

| 1 | 4 |

| 2 | 16 |

| 3 | 64 |

| . | . |

| . | . |

| n | 4^n |

4.2 | 硬件安全原语的功耗和面积优化

隧穿场效应晶体管p‐i‐n正向漏电流可优化真随机数发生器等硬件安全原语的功耗和面积。例如,考虑如

所示用于真随机数发生器设计的基于振荡崩溃时间的偶数级环形振荡器(RO)。该传统设计利用反相器中由工艺偏差引起的系统性失配。与工艺偏差不同,通过利用TFET传输门功能失效(由TFET p‐i‐n正向漏电流引起),可对图14A中的偶数级环形振荡器进行修改。如图14B所示。此处,两种设计均采用20纳米砷化铟TFET实现。在图14A中,由于是仿真工作,未使用工艺偏差,而是通过基于电容的延迟变化来获得足够的崩溃周期。可以看出,通过利用TFET的p‐i‐n正向漏电流,所提出的设计可实现40%的面积缩减。

所示用于真随机数发生器设计的基于振荡崩溃时间的偶数级环形振荡器(RO)。该传统设计利用反相器中由工艺偏差引起的系统性失配。与工艺偏差不同,通过利用TFET传输门功能失效(由TFET p‐i‐n正向漏电流引起),可对图14A中的偶数级环形振荡器进行修改。如图14B所示。此处,两种设计均采用20纳米砷化铟TFET实现。在图14A中,由于是仿真工作,未使用工艺偏差,而是通过基于电容的延迟变化来获得足够的崩溃周期。可以看出,通过利用TFET的p‐i‐n正向漏电流,所提出的设计可实现40%的面积缩减。

与传统设计相比有所减少。表5显示,提出的30级环形振荡器仅需使用92个门电路(假设一个传输门为一个门电路)即可实现,而传统架构则需要152个门电路。

在提出的RO设计中,由于器件漏电流的存在,传输门(TG)部分导通并呈现高阻态。因此,整个RO环路针对不同的控制位组合表现出非线性延迟变化,并实现了类似于传统RO设计的高度随机性。为了说明这一现象,考虑如

所示的三级级联TFET传输门延迟链。通过施加不同的控制位组合(X1, X2,和X3),理论上分析了输入( Vin)与输出(Vout)之间由RC组件引起的传播延迟。基于传输门的延迟链可建模为如图15B所示的等效RC网络。

所示的三级级联TFET传输门延迟链。通过施加不同的控制位组合(X1, X2,和X3),理论上分析了输入( Vin)与输出(Vout)之间由RC组件引起的传播延迟。基于传输门的延迟链可建模为如图15B所示的等效RC网络。

输入和输出之间的Elmore延迟(Td)可以表示如下:

$$

Td = R_1C_1 + (R_1 + R_2)C_2 + (R_1 + R_2 + R_3)C_3 \quad (1)

$$

通过考虑上述方程,可推导出三级延迟链在不同控制位组合下的传播延迟如下:

$$

Td(000) = 6R_N C \quad (2)

$$

$$

Td(001) = (K + 5)R_N C \quad (3)

$$

$$

Td(010) = (2K + 4)R_N C \quad (4)

$$

$$

Td(101) = (4K + 2)R_N C \quad (5)

$$

$$

Td(110) = (5K + 1)R_N C \quad (6)

$$

$$

Td(111) = (6K)R_N C \quad (7)

$$

其中,$ R_N $ 是 TG 在导通状态下的电阻(包括反相器电阻),$ K × R_N $ 是 TG 在关断状态下的电阻(“K”为常数K),$ C_1 = C_2 = C_3 = C $(假设为相同的电容值以简化计算)。

从方程(1)到(7)可以看出,三级TFET传输门链在不同控制位组合下会产生传播延迟的变化。

显示了使用TFET的两种设计的瞬态特性;可以看出,两个环形振荡器均达到了足够的崩溃所需周期数。图16B展示了通过应用不同配置位时环形振荡器崩溃所需的周期数。显然,通过改变配置位(如表6中所考虑的),基于多路复用器的传统偶数级环形振荡器25选择不同的反相器组合,从而产生随机周期数以实现崩溃。提出的30级环形振荡器也表现出类似的行为,如图16B所示,这是由于非线性延迟变化所致。显示了在0.4V供电电压下,从连续40个周期计算出的传统和提出的偶数级环形振荡器的平均功耗。利用TFET p‐i‐n正向漏电流的提出环形振荡器相比传统环形振荡器实现了 5×更低功耗,如图17所示。由于p‐i‐n正向漏电流的存在,TFET传输门在关断状态下表现出高传播延迟。这使得偶数级环形振荡器能够获得足够的抖动(延迟变化),并在无工艺偏差的情况下产生所需的崩溃周期数。由于传输门的高电阻,偶数级环形振荡器限制了流过环路的电流。因此,与传统的TFET偶数级环形振荡器设计相比,偶数级环形振荡器实现了功耗降低80%。因此,TFET p‐i‐n正向漏电流优化了硬件安全原语的功耗和面积。

| 序号 | 配置位 |

|---|---|

| 1 | 100100100100100100100100100100 |

| 2 | 110100110100110100100100100100 |

| 3 | 100001000010000100001000010000 |

| 4 | 110001110001100100001000010000 |

| 5 | 101001010010100100101001010010 |

5 | 结论

本文研究了TFETs的非对称特性,发现随着漏源电压的增加,p‐i‐n正向漏电流显著增大,这对TFET数字电路产生了不利影响。针对这一问题,提出了TFET新型紧凑型门和三态门以缓解p‐i‐n正向漏电流效应。所提出的TFET门电路在噪声容限和功耗方面表现出更高的可靠性。与传统TFET传输门相比,所提出的新型紧凑型门和三态门分别实现了 2×和 6×的更低功耗。此外,通过探索TFET p‐i‐n正向漏电流在硬件混淆应用中的利用,提出了一种新的硬件安全电路设计方法。该正向漏电流还被用于优化硬件密码原语(如TRNGs)的面积和功耗,分别减少了40% 和80%。

3241

3241

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?