声明:本博客并非严格的、完整的技术型文章,只是将本人所接触到的内容作学习记录,如有错误欢迎大家在评论区指正。如果这篇博客对你有帮助的话,请给我点一个免费的赞和关注,谢谢。本篇文章参考arm官网中的AMBA3 specification。

文章目录

一、AHB-Lite总线组件

AHB的信号都是以H开头,此外AHB-lite的硬件架构,可以分为四部分,分别是Master、Slave、Decoder以及MUX。

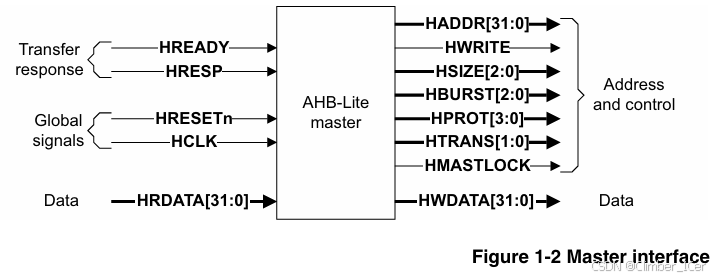

1. AHB-Lite master

信号可分为以下三组(属于同一个phase的信号在同一周期内都有效):

- global signals

- address phase signals:address and control

- data phase signals:r/w data and response

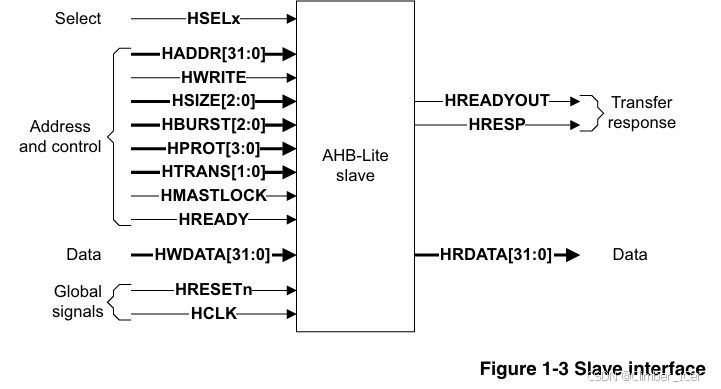

2. AHB-Lite slave

AHB-Lite slave的信号同样可以分为三组,值得注意的是Slave有一个输入的ready和一个 输出的ready。输入的HREADY用于告诉Slave和Master,整个总线上是否有未完成的传输,如果有则此时不能收transfer的命令。而输出的HREADYOUT,用来代表正在传输的那个slave是否已经准备进行真正的数据传输(而不是反压)。

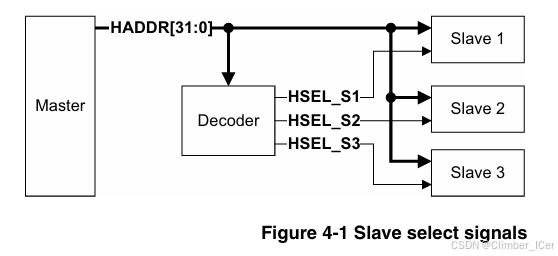

3. Decoder

把haddr译码,产生各个slave的hsel信号。此外这个信号不光要给Slave,通常还要给MUX,以方便Mux从多个Slave中选中一个,返回给Master。这个信号可能是HSELX本身,也可以是HSELX导出的信号。

Note:In multi-layer AHB-Lite implementations, the decoder function is usually included in the multi-layer interconnect component.

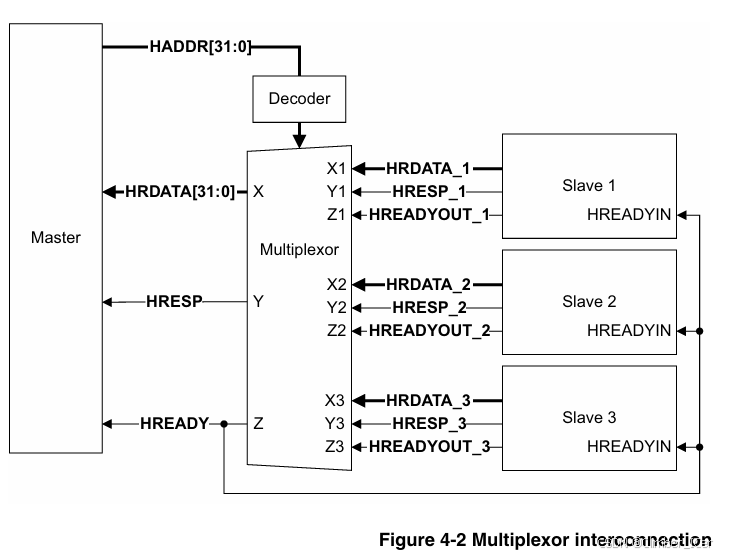

4. Multiplexor

单master多slave:

- 需要MUX把各个slave的hrdata,hresp选择后输出到master

- 需要MUX把各个slace的hready_out选择后输出到master/slave

多master多slave:

- single-layer(bus arbiter):需要MUX把各个master的address/control信号MUX后输出到slave;需要MUX把各个slave的hrdata,hresp选择后输出到master;需要MUX把各个slace的hready_out选择后输出到master/slave

- multi-layer(bus matrix):实现方法根据带宽需求而各不相同。

此外一个AHB-Lite系统,一般需要一个default slave。

- 当因为意外,一个系统未定义的地址出现在bus上时,decoder译码该地址后应该选中default slave;

- default slave对IDLE/BUSY trasns回okay response

- default slave对nonseq/seq trasns回error response

二、AHB-Lite信号及传输过程

信号与传输过程放在一起讲,更有助于学习和理解协议。

1. 信号列表

全局信号:

- HCLK:时钟信号,上升沿同步

- HRESETn:AHB-lite总线复位信号,低有效。复位时候HTRANS为IDLE,slave的HREADYOUT为高电平。

Master信号:

- HADDR[31:0]:32bit的地址总线(同时送给slave和decoder)

- HWRITE:高电平代表写传输,低电平代表读传输

- HSIZE[2:0]:指示传输的大小,通常为字节、半字或字,最大可达到1024bits

- HBURST[2:0]:突发传输类型

- HPROT[3:0]:保护控制信号

- HTRANS[1:0]:指示传输的类型

- HMASTERLOCK:用来实现原子操作的

- HWDATA[31:0]:写数据,一般建议最小为32bits,最大可以为1024bits

Slave信号:(信号都送往mux)

- HRDATA[31:0]:在读操作期间,读取数据总线将数据从选定的slave传输到多路复用器。然后,multiplexor 将数据传输到 master。建议最小数据总线宽度为 32 位。

- HREADYOUT:当为高电平时,该信号表示bus上的传输已经完成。该信号可以驱动为低电平来反压主机以延长传输。

- HRESP:指示传输状态。低电平时代表传输状态ok,高电平时代表传输状态error。

2. 传输流程

<1> Basic Transfers

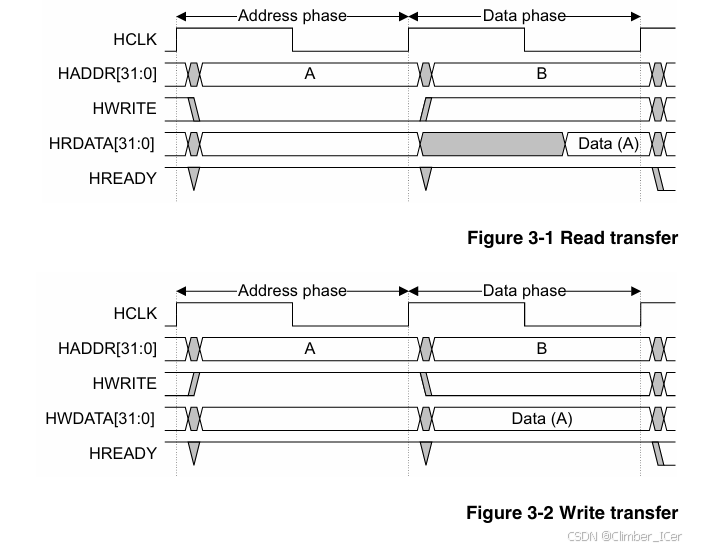

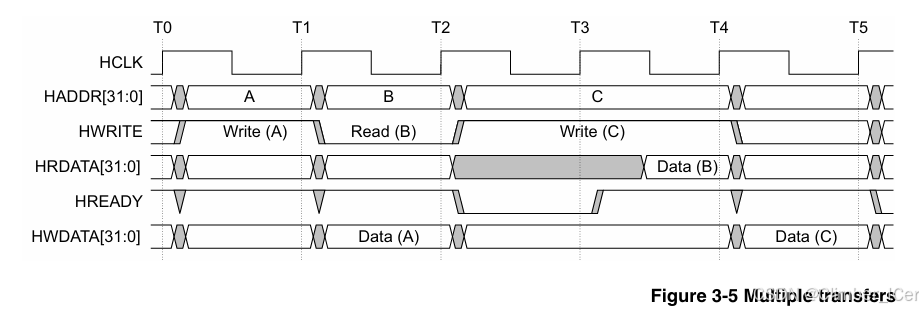

与APB中的setup phase和access phase相似,AHB-Lite中也将传输分为了两个阶段address phase和data phase。

Without wait transfer

下图时没有wait的transfer,在address phase阶段,decoder根据地址选中相应的slave;在data phase阶段slave和mux完成剩下的工作。第一次传输的数据阶段和第二次传输的地址阶段,是可以重叠的,相当于流水线操作。对比apb的读写操作,大大节省了时间。

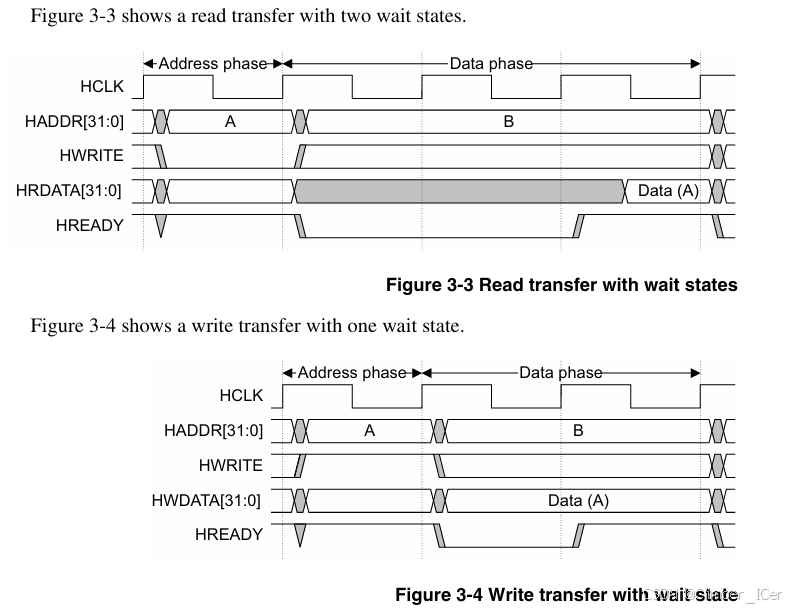

With wait transfer

对于写操作来说,master在被反压的周期内必须保持写数据稳定。

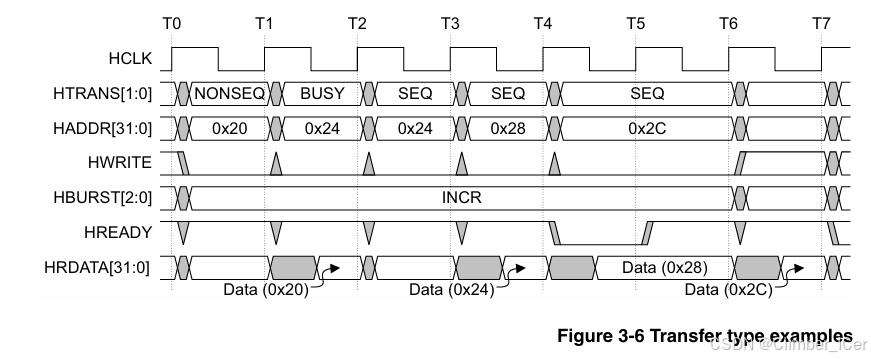

<2> HTRANS[1:0]—Transfer types

HTRANS[1:0]信号用于指示当前的传输类型,一共有四种类型:

- IDLE(b00):没有数据需要传输,其它的控制信号和地址信号不起作用。

- BUSY(b01):没有数据需要传输。这个信号可以在突发传输中用来插入空闲的cycle,表示主机在忙,也就是说传输还在继续,但是处于暂停状态。在不指定突发长度情况下,在最后一拍设为BUSY传输,来表明这是突发传输的最后一笔,之后master可以执行NONSEQ或IDLE。而固定长度的突发必须以SEQ来结束。

- NONSEQ(b10):需要传输数据。可能时传输一笔数据(single transfer)或者是突发传输的第一笔(the first transfer of a burst)。

- SEQ(b11):需要传输数据,用在突发传输中,代表连续的传输。地址需要增加(除非上一笔传输时BUSY),其他的控制信号不变。

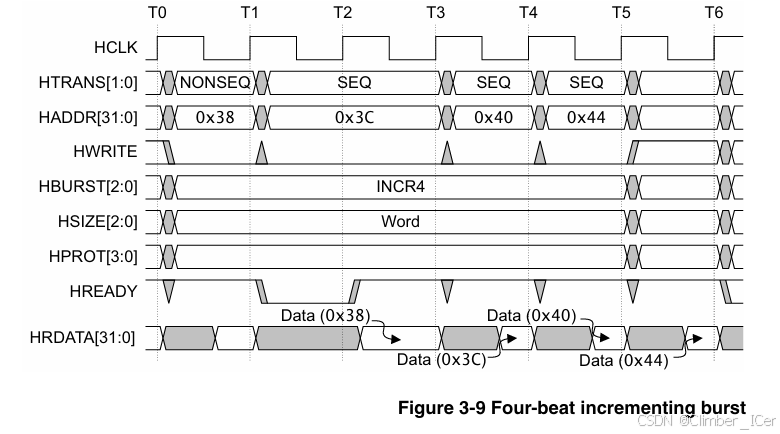

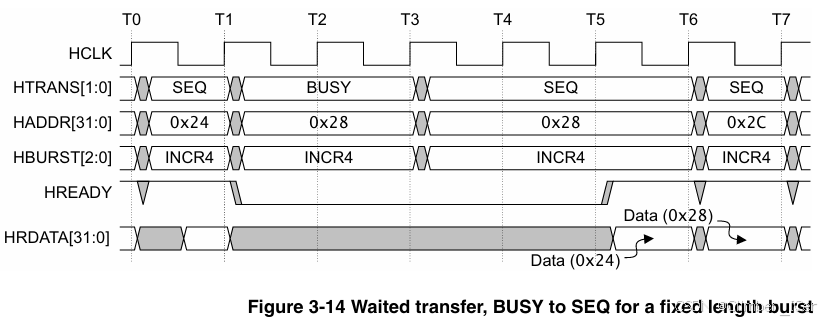

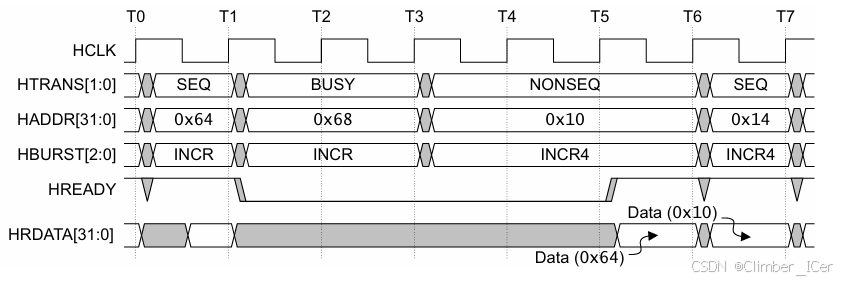

对上图的transfer过程以cycle为单位解析一下: - T0-T1:4-beat 读开始了伴随着一个NONSEQ transfer

- T1-T2:master无法执行second beat(第二笔),所以插入了一个BUSY transfer去延迟第二笔传输的开始。slave提供了first beat的read data。

- T2-T3:master现在准备好去开始第二笔传输,所以声明了SEQ transfer。同时master忽略了此时slave在bus上返回的read data。

- T3-T4:master执行第三笔传输。slave提供第二笔的读数据。

- T4-T5:master执行最后一笔传输。slave不能完成传输,所以使用HREADY来插入一周期的等待。

- T5-T6:slave返回第三笔的读数据。

- T6-T7:slave返回最后一笔的读数据。

注意:single突发之后不能加BUSY,必须是NONSEQ或IDLE

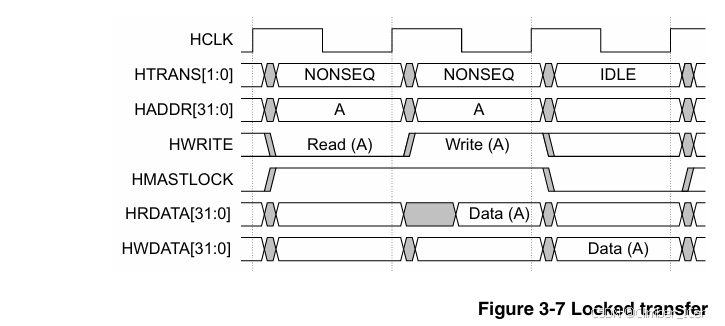

<3> HMASTERLOCK—locked transfers

如果主机想发起一次带锁的访问,那么就需要HMASTERLOCK信号。简单理解就是多主机可以访问一个从机的情况下,需要确保这个时间段只有该主机对其进行访问,避免数据出现错误。

同时协议建议(非必须),在一次locked transfer之后,master插入一个IDLE transfer。

在系统中,locked transfer是由bus结构保证的(非master/slave保证)。

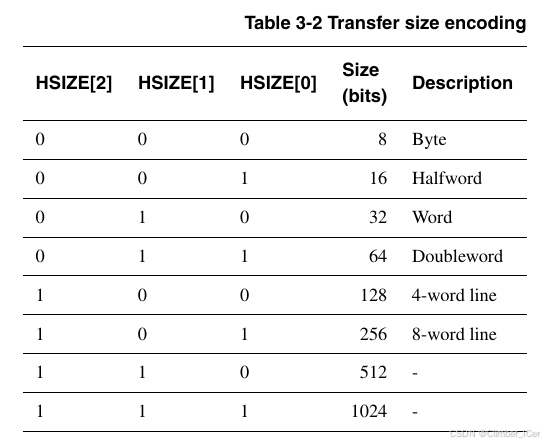

<4> HSIZE—transfer size

HSIZE[2:0]用来标志数据传输的位宽。其实HSIZE表明了在burst transfer中一个beat地址加多少。

注意以下三点:

- 通过HSIZE设置的transfer size必须小于或等于传输数据data的位宽。

- HSIZE和HBURST一起可以决定wrap burst的地址边界(address boundary)。

- HSIZE必须保持不变在一整个burst transfer中。

为什么需要HSIZE? 因为如果固定位宽的话,在一个复杂系统里面,其PPA不够优化。系统高带宽部分,使用更大的数据位宽;系统低带宽部分使用更小的数据位宽。

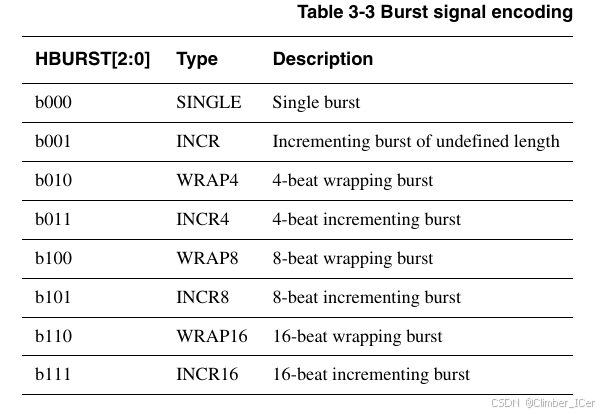

<5> HBURST[2:0] — Burst operation

协议支持4、8、16-beats和不定长突发,以及single transfer。同时有INCR(递增)和WRAP(回环)两种type。

值得注意的是,master在INC突发时不可以跨越1KByte边界,因为AHB规定不同的Slave最小粒度为1KB,因此跨越1KB可能访问到别的Slave去。

值得注意的点:

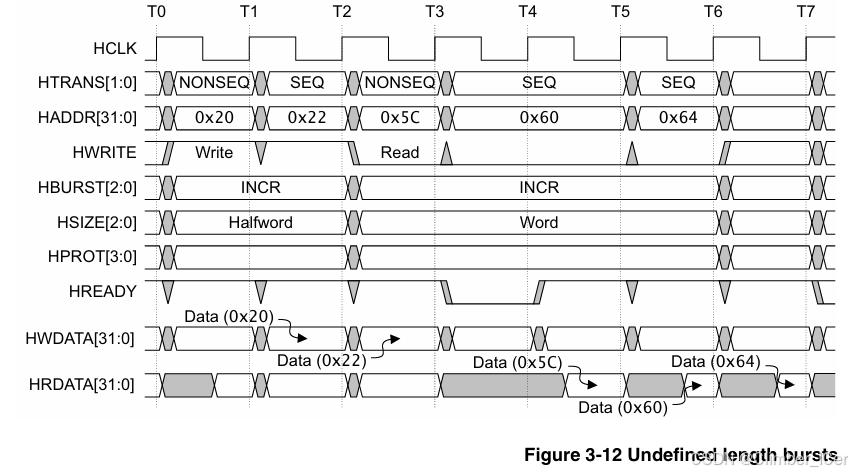

- INCR突发时,BUSY后面可以加NONSEQ或IDLE,表明当前突发已结束并开始下一次传输(NONSEQ)或没有传输(IDLE);

- INCRx突发时,必须以SEQ transfer来终止,不能使用BUSY终止。

- SINGLE突发后不能是BUSY,必须是IDLE或NONSEQ。

- 突发可以被提前终止由于:slave error response或multi-layer interconnect termination

为什么需要WARP的突发类型? 适用于cache line的访问。

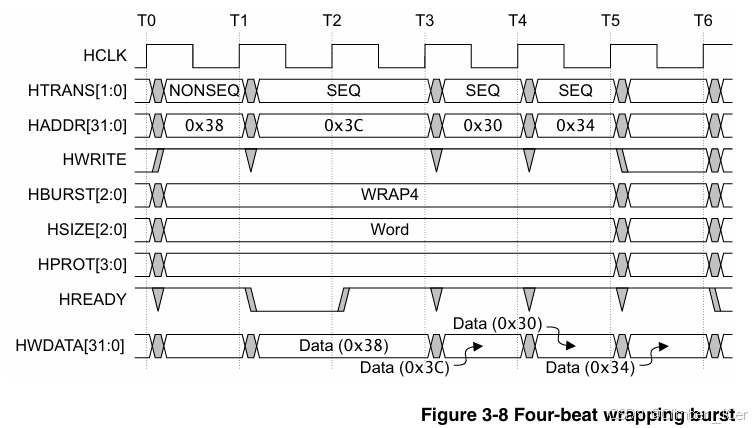

下面是INC4和WRAP4的例子:

从上图可以看到WRAP4中地址从0x3C跳到0x30,这是因为address wraps at 16-byte boundaries。也就是对于它来说0x10为一组,及0x00到0x0C为一组,0x10到0x1C为一组,0x20到0x2C为一组,0x30到0x3C为一组,依此类推。

<6> waited transfers

从机可以使用HREADY来反压主机,在反压的传输期间,master只能对transfer type和address进行更改。

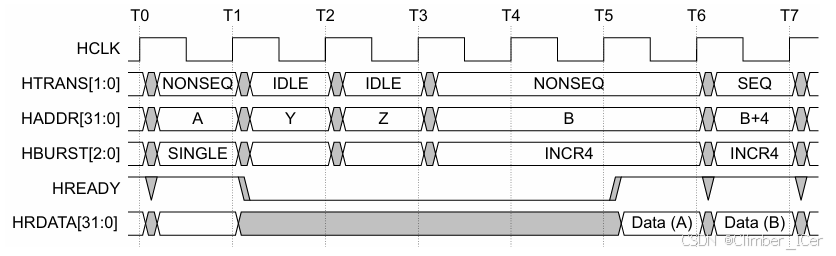

Transfer type changes during wait states

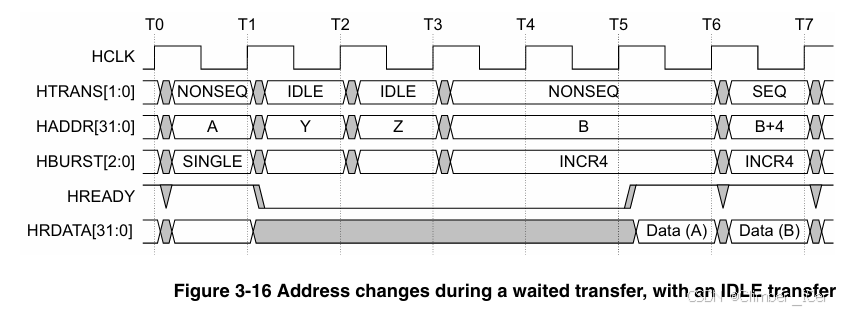

在等待传输期间,允许master从IDLE改为NONSEQ,但更改后必须保持HTRANS恒定直到HREADY拉高,如下所示。

在定长的突发传输中,允许从BUSY改为SEQ,但更改后必须保持HTRANS恒定直到HREADY拉高,如下所示。

在不定长的突发传输中,允许从BUSY改为SEQ继续传输,或改为IDLE与NONSEQ代表传输终止。

Address changes during wait states

在等待传输的过程中,允许master更改IDLE的地址,当HTRANS改为NONSEQ时,master必须保持地址不变直到HREADY拉高。

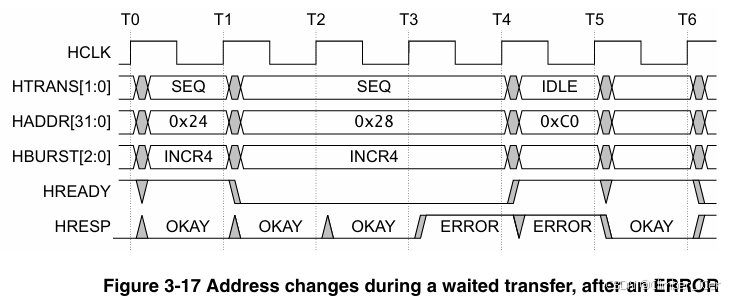

在等待传输过程中,如果slave以ERROR响应,则允许master在HREADY为低电平时更改地址。

<7> HPORT[3:0] — Protection control

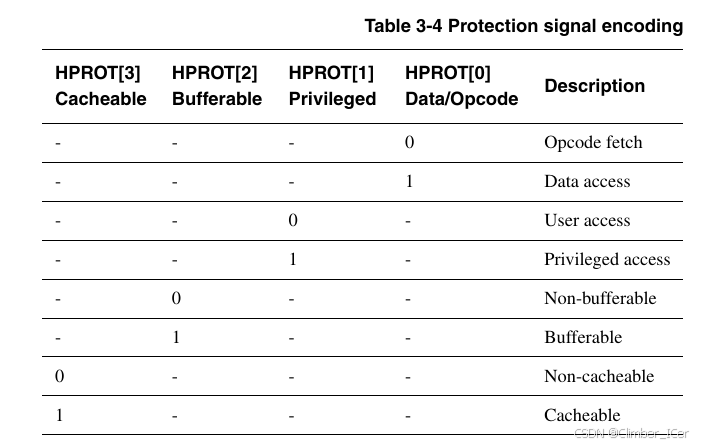

保护控制信号HPROT[3:0],每一位代表的含义如下表所示。

- bit0:代表取数据还是取指令。

- bit1:代表是特权模式还是非特权模式访问。有一些地址,非特权模式是不能访问的。

- bit2:代表bufferable,代表数据是可以写在buffer中还是一定要到达终端(最终的地址空间)

- bit3:代表cacheable,代表数据是放在cache中,还是终端地址。

如果不使用HPORT则master将HPORT设置为0011。

3. Slave Response Signaling

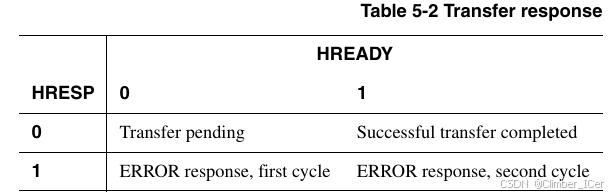

HRESP为0代表OK,为1代表ERROR,如果是ERROR则需要两个时钟周期来处理,可以理解为给master一个思考的时间(是继续传还是IDLE状态终止),在第二个时钟周期拉高HREADY。

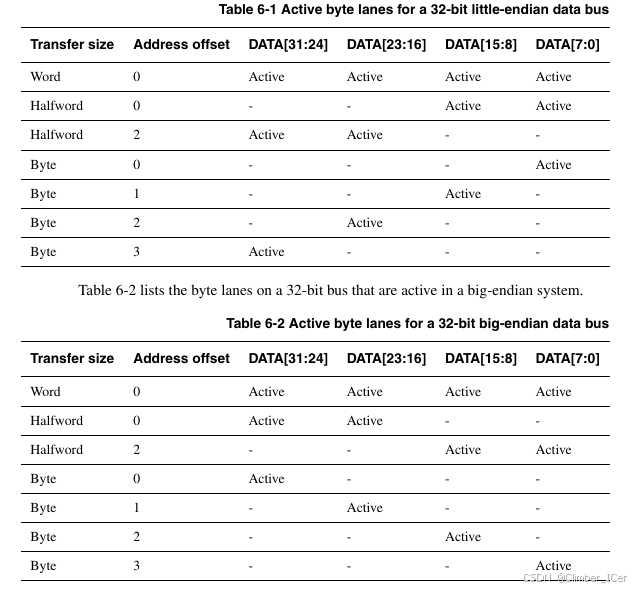

4. Data Buses

三、AHB历史演进版本

AMBA(AHB2):第一版;

AMBA3(AHB-Lite):

- master去掉hbusreq,hgrant信号;

- slave只保留okay/error response(去掉retry/split响应)

AMBA5(AHB5): - 把AHB-Lite重命名为AHB5

- master重命名为manager,slave重命名为subordinate

- manager增加write data enable:hwstrb

- manager/subordinate增加exclusive access的信号

- manager/subordinate增加user signaling

- odd parity protection

3123

3123

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?