FPGA基础之逻辑单元LE(三)

本文主要简单介绍下verilogHDL代码和LE的对应关系,也就是说我们的代码占用了LE当中的哪些资源LE:

- 如果是纯组合逻辑的话,会使用到LE中的查找表(LUT)等结构;

assign dout[0] = (din==3'b000)? 1'b1 : 1'b0;

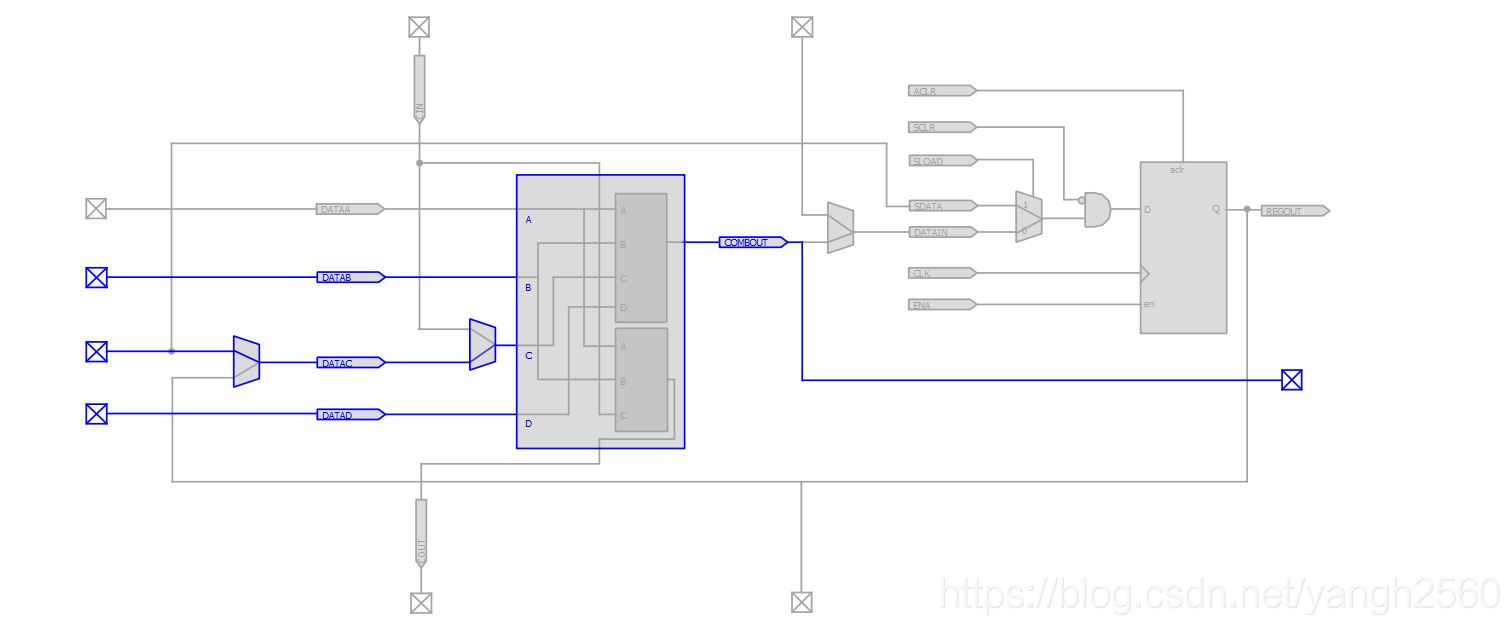

这是一段简单的组合逻辑代码,当din的3bit全为0时,dout[0]输出为1,否则为0;

通过上图可以看出,那一行组合逻辑代码在布局布线后占用一个LE的资源,并且仅占用了组合逻辑部分,LE内部使用了LUT的B、C、D输入端口,输出直接旁路输出,并没有占用寄存器资源。

- 在使用了时序逻辑后,将会用到LE中的寄存器(reg)等结构;

always@(posedge clk or negedge rst_n)

if(!rst_n)

dout[0] <= 1'b0;

else if(din==3'b000)

dout[0] <= 1'b1;

else

dout[0] <= dout[0];

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

4万+

4万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?