提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

状态机专题练习

要求

1、根据以下描述功能用verilog编写一段代码,并用状态机来实现该功能。

(1)状态机:实现一个测试过程,该过程包括启动准备状态、启动测试、停止测试、查询测试结果、显示测试结果、测试结束返回初始化6个状态;用时间来控制该过程,90秒内完成该过程;

(2)描述状态跳转时间;

(3)编码实现。

- 画出可以检测10010串的状态图, 并用verilog编程实现之。

(选做,FPGA实训同学必做)完成作业并提交MD文档和博客地址。

一、

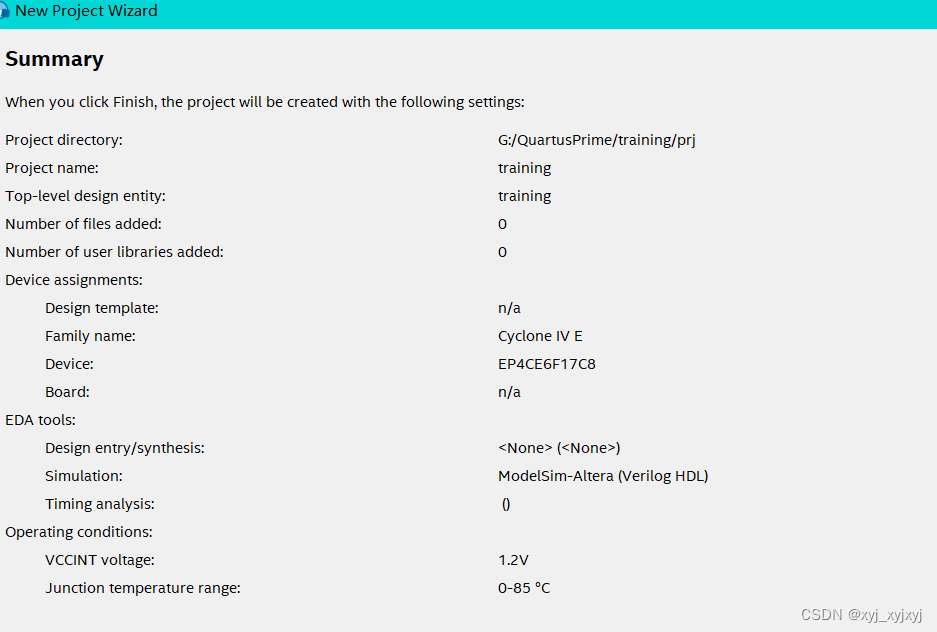

1. 新建一个项目

2. 新建一个Verilog HDL文件

每个状态保持15s。每个状态对应的led状态各不相同。led的状态值为当前状态值。

module training_1(

input wire clk,

input wire rst_n,

output reg [3:0]led

);

localparam [2:0] S1 = 1;

localparam [2:0] S2 = 2;

localparam [2:0] S3 = 3;

localparam [2:0] S4 = 4;

localparam [2:0] S5 = 5;

localparam [2:0] S6 = 6;

parameter [29:0] MAX_COUNT = 750_000_000;//15s

reg [29:0] count;

reg [2:0] current_state;

reg [2:0] next_state;

//15s 计时器 以及 状态转移

always@(posedge clk or negedge rst_n) begin

if(!rst_n) begin

current_state <= S1;

count <= 30'd1;

end

else if (count == MAX_COUNT) begin

count <= 30'd1;

end

else begin

count <= count + 30'd1;

current_state <= next_state;

end

end

// 状态判断

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

next_state <= S1;

end

else begin

case (current_state)

S1: begin

if(count == MAX_COUNT) begin

next_state <= S2;

end

else begin

next_state <= next_state;

end

end

S2: begin

if(count == MAX_COUNT) begin

next_state <= S3;

end

else begin

next_state <= next_state;

end

end

S3: begin

if(count == MAX_COUNT) begin

next_state <= S4;

end

else begin

next_state <= next_state;

end

end

S4: begin

if(count == MAX_COUNT) begin

next_state <= S5;

end

else begin

next_state <= next_state;

end

end

S5: begin

if(count == MAX_COUNT) begin

next_state <= S6;

end

else begin

next_state <= next_state;

end

end

S6: begin

if(count == MAX_COUNT) begin

next_state <= S1;

end

else begin

next_state <= next_state;

end

end

default: next_state <= S1;

endcase

end

end

//状态输出 根据当前状态点亮不同的灯

always @(posedge clk or negedge rst_n) begin

if (!rst_n) begin

led <= 4'd0;

end

else begin

case

本文介绍了使用Verilog HDL设计一个包含启动准备、启动测试、停止测试、查询结果、显示结果和初始化状态的FPGA测试过程。每个状态持续15秒,通过LED显示不同状态。同时,提到了状态机的编码实现以及状态图的绘制,适用于FPGA实训作业。内容包括新建项目、编写Verilog文件、创建仿真文件及Tcl脚本,以及状态机的消抖处理。

本文介绍了使用Verilog HDL设计一个包含启动准备、启动测试、停止测试、查询结果、显示结果和初始化状态的FPGA测试过程。每个状态持续15秒,通过LED显示不同状态。同时,提到了状态机的编码实现以及状态图的绘制,适用于FPGA实训作业。内容包括新建项目、编写Verilog文件、创建仿真文件及Tcl脚本,以及状态机的消抖处理。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

2490

2490

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?