在做一款消费电子产品时,需要采集电池电压(3.3V-4.2V),同时在休眠的时候希望尽量减小待机电流。电池电压采集电路采用两个1%的300K电阻进行分压,由该电路引起的待机电路为4.2/(300+300)mA=7uA.此时比较合理(整机的待机电流要求30uA以内)。

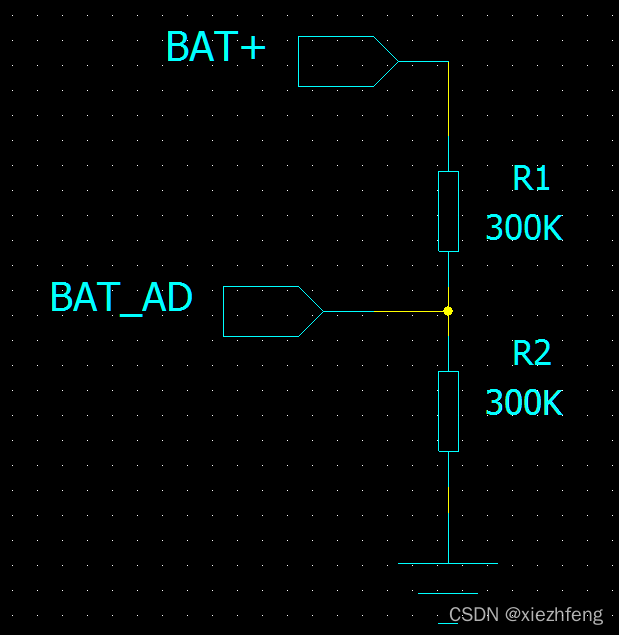

初始设计电路如下:

在编程采集数据时发现测试电压与实际电压有偏差,测试值总比实际值偏小一点。在软件上做补偿,把值修正了。

但是换一个板子测试的时候发现测试的电压又不准了,此时知道通过软件补偿这种方法行不通。那么只能从硬件找原因。

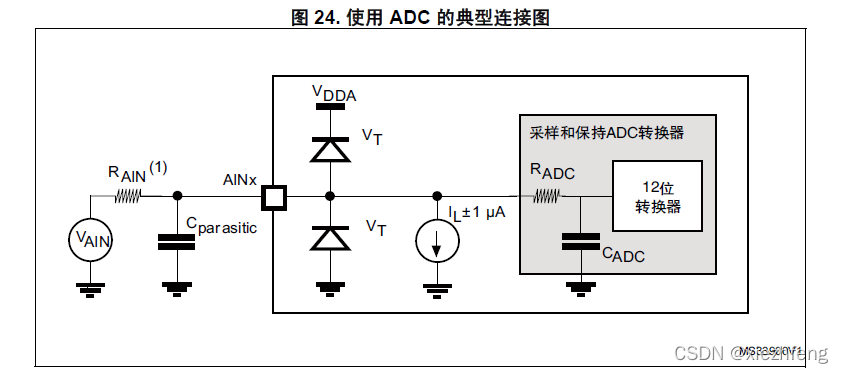

查找datasheet发现AD的输入阻抗最大只有50KΩ。

图中RAIN:外部输入阻抗,STM32芯片中这个值最大为50KΩ;

RADC:采样开关电阻,最大值为1KΩ;

CADC:内部采样和保持电容,最大值为8pF.

在ADC数据采集的时候需要有电流流入,那么RAIN会产生一个压降。阻容网络中的RADC和CADC上,对电容的充电由RADC控制。随着源电阻(RADC)的增加,对保持电容的充电时间也相应增加。

对CADC的充电由RAIN+RADC控制,因此充电时间常数为tc = (RADC + RAIN) × CADC。如果时间过短,ADC转换的数值会小于实际值。

通过以上数据知道,采集精度跟采集时间和输入阻抗有关。但是通过计算得知,如果输入阻抗为300KΩ,那么充电时间约为2.4uS。在软件上把采样周期调到最大(ADC_SampleTime_239_5Cycles,频率为12M,时间19.9uS),还是存在误差。说明此时跟周期不是主要原因。

问题出在输

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?