目录

文章总目录点这里:《FPGA接口与协议》专栏的说明与导航

1、时钟设计

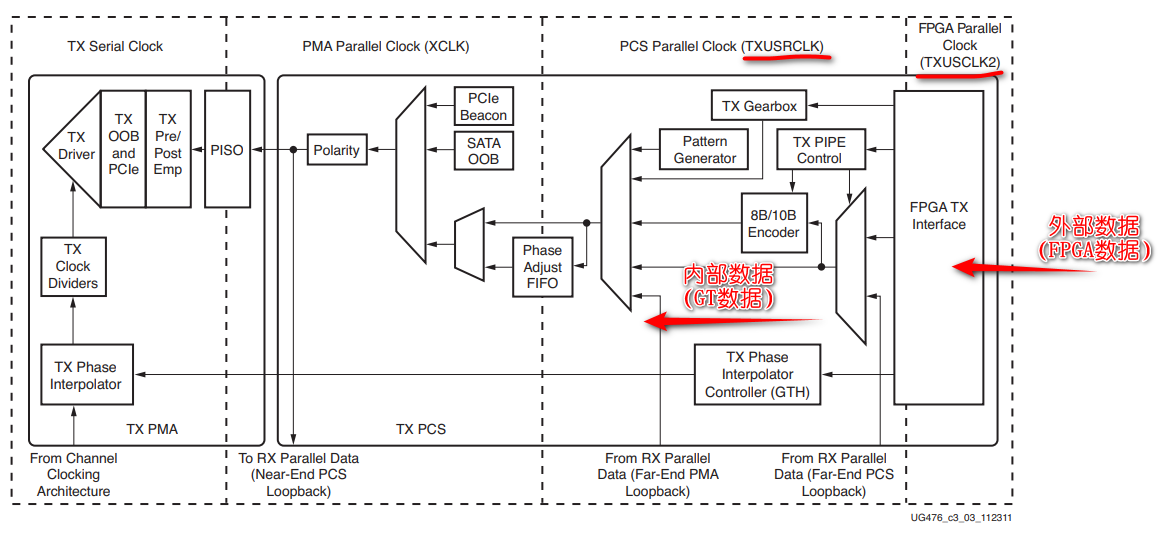

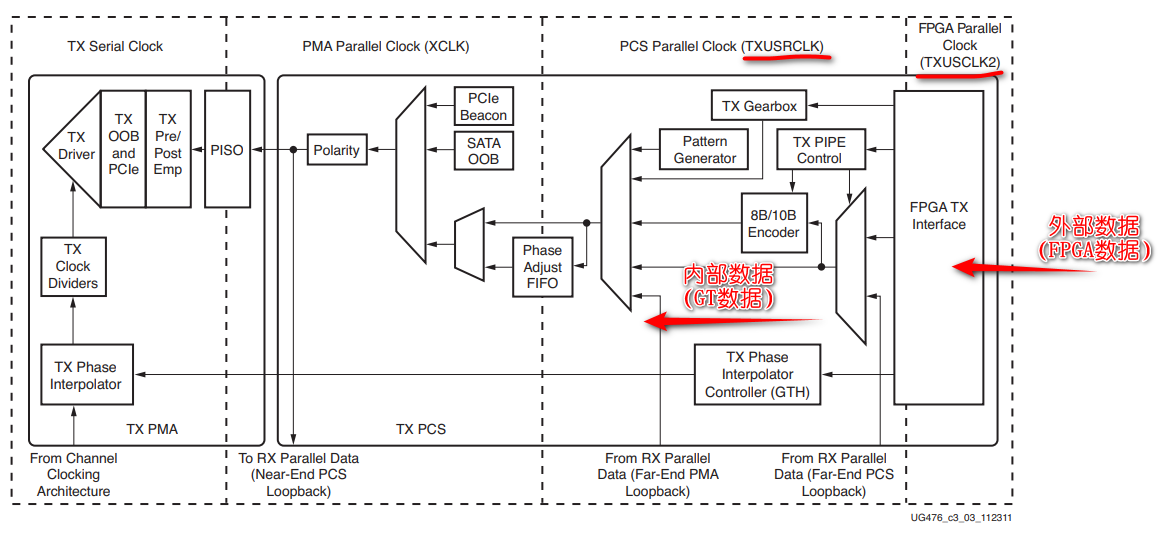

GT收发器内部比较复杂,所使用的时钟不止一个。其中比较主要的时钟有两个,架构示意图如下:

-

TXUSRCLK2:这个时钟是和FPGA逻辑交互的时钟,FPGA要通过GT收发器发出的数据都工作在这个时钟下

-

TXUSRCLK:这个时钟是GT收发器内部数字逻辑所使用的工作时钟

目录

文章总目录点这里:《FPGA接口与协议》专栏的说明与导航

GT收发器内部比较复杂,所使用的时钟不止一个。其中比较主要的时钟有两个,架构示意图如下:

TXUSRCLK2:这个时钟是和FPGA逻辑交互的时钟,FPGA要通过GT收发器发出的数据都工作在这个时钟下

TXUSRCLK:这个时钟是GT收发器内部数字逻辑所使用的工作时钟

1万+

1万+

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?