Zynq UltraScale+ MPSOC在PS侧扩展了PS-GTR接口,可以灵活的支持PCIe、SATA和USB3.0连接。我们在自己开发的板卡上支持了SATA数据接口。

Step1:SATA数据接口

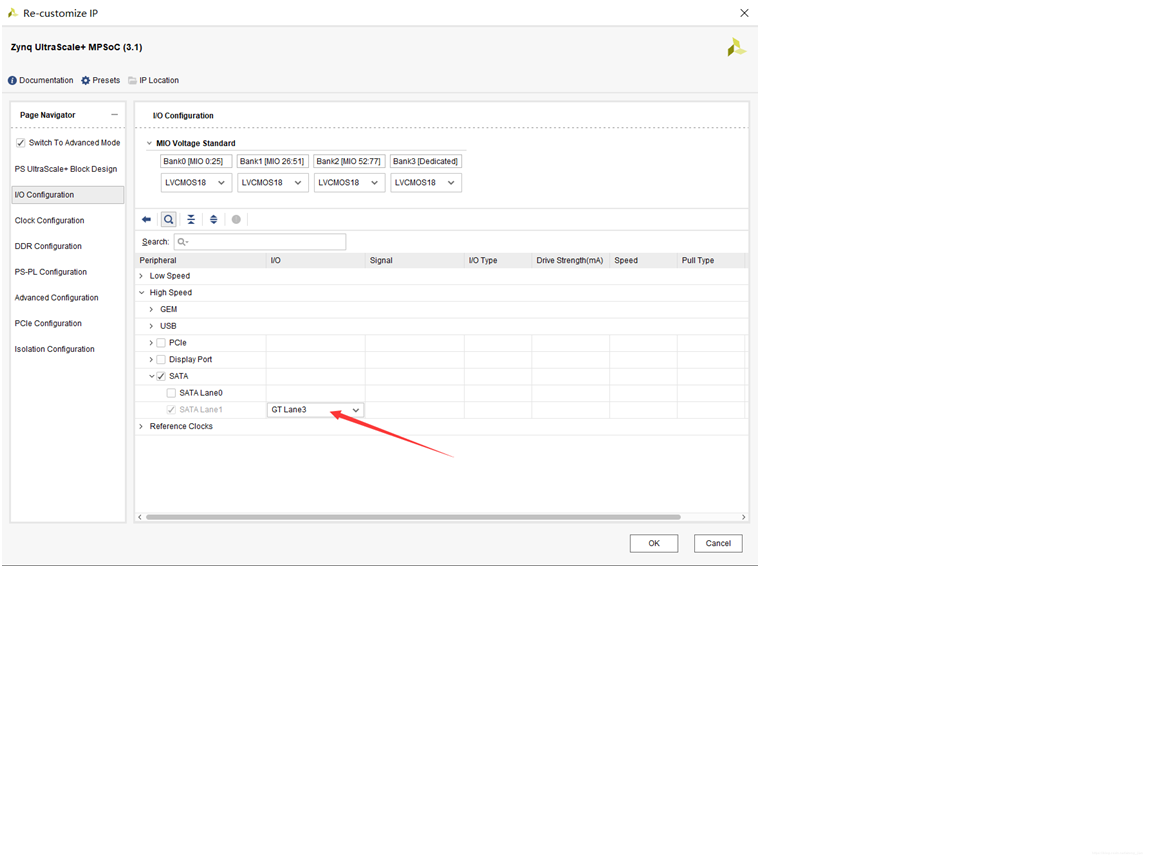

根据实际板卡设计,在PCW(Processor System Configuration Wizard)中选择SATA对应的物理连接,例如,我们的板卡中,SATA接口使用了GT Lane3,这里,我们在PCW中选择GT Lane3。

Step2:SATA时钟

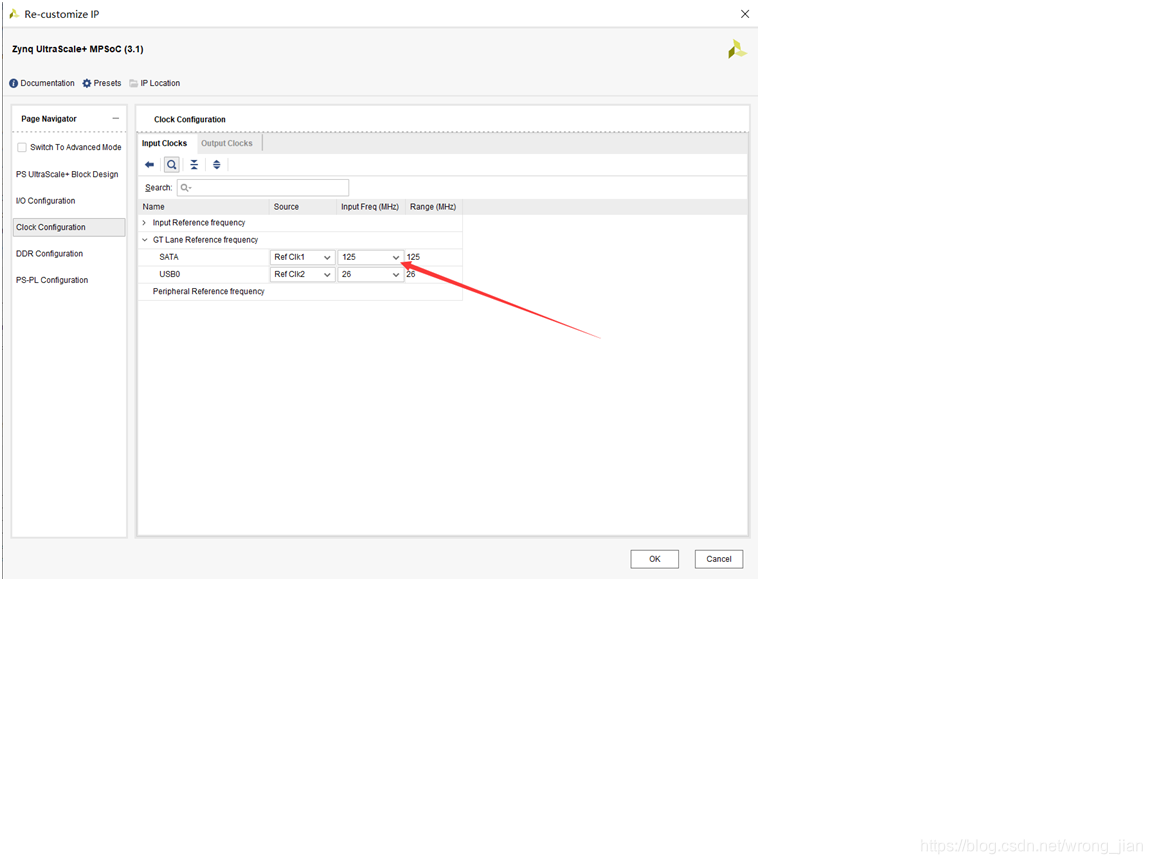

根据Xilinx UG1085,SATA的参考时钟可以是125MHz或者150MHz,我们的定制板卡上采用的时钟为125MHz。PCW中,按照板卡的使用时钟源进行配置:

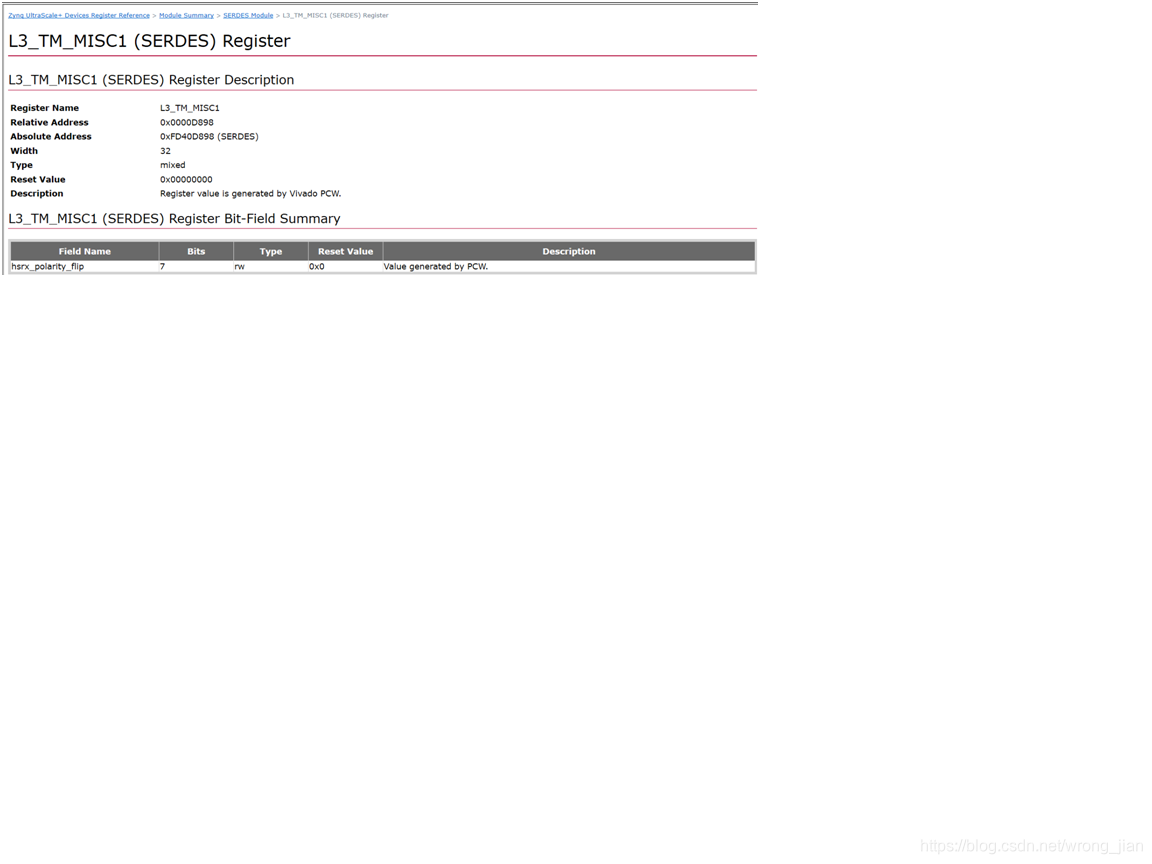

Know-How:硬件设计调线处理

有些板卡中,为了方便PCB的Layout,设计中进行了调线。例如,将PS-GTR的RX的PN进行了翻转。针对这种情况,可以在PS-GTR中进行对应的寄存器设置。在Xilinx UG1087(Zynq UltraScale+ MPSOC Register Reference)中,列出了PS-GTR的寄存器。比较遗憾的是,Xilinx没有给出pdf版本的文档,采用的是Web页面形式。

例如,硬件设计中,如果GTR的RX的PN接反,可以通过修改寄存器的方式将PN进行翻转。

其他:

Petalinux下的具体操作过程参考Xilinx UG1144,这里不再赘述。

Zynq UltraScale+ MPSOC SATA接口设计与调线

Zynq UltraScale+ MPSOC SATA接口设计与调线

本文介绍了如何在Petalinux下进行Zynq UltraScale+ MPSOC的SATA接口设计,包括数据接口的选择配置、时钟设置,以及针对硬件设计中的调线处理。在Step1中,通过PCW选择了GT Lane3作为SATA接口。Step2中,配置了125MHz的SATA参考时钟。在硬件调线部分,讨论了如何处理RX PN翻转的问题,并提到可通过修改寄存器解决。

本文介绍了如何在Petalinux下进行Zynq UltraScale+ MPSOC的SATA接口设计,包括数据接口的选择配置、时钟设置,以及针对硬件设计中的调线处理。在Step1中,通过PCW选择了GT Lane3作为SATA接口。Step2中,配置了125MHz的SATA参考时钟。在硬件调线部分,讨论了如何处理RX PN翻转的问题,并提到可通过修改寄存器解决。

2950

2950

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?