目录标题

参考文档:Arm® CoreLinkTM GIC-700 Generic Interrupt Controller Technical Reference Manual A.5 Setting multichip options

涉及的寄存器:GICD_CHIPSR、GICD_DCHIPR、GICD_CHIPR(n),详细寄存器描述:GIC700 Multichip operation

如下配置流程以Chip0为主die,连接其他Chip为例,讲解Multichip之间如何进行连接:

一、设置rt_owner

- 配置GICD_DCHIPR.rt_owner=0(DIE0对应的chip_id,设置Chip0为主die);

- 读GICD_DCHIP.PUP=0表示步骤1设置成功。

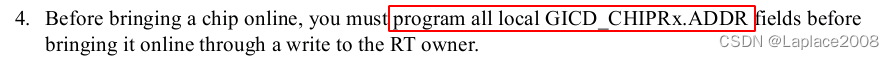

二、设置GICD_CHIPRx.ADDR

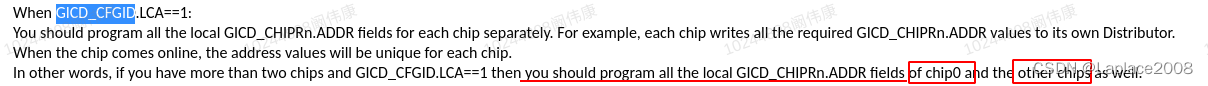

设置所有Chip的本地寄存器:GICD_CHIPRx.ADDR (读出GICD_CFGID.LCA==1,即需要对每个chip进行单独配置)

根据主DIE与其他各DIE的连接关系,此处描述为需要在芯片online之前,完成对所有需链接芯片的本地GICD_CHIPRx.ADDR的配置。其中此处配置的ADDR为其他各DIE的ccg NodeId对应的A4S logical id。

配置D1_GICD_CHIPR<0>.ADDR = 5

配置D2_GICD_CHIPR<0>.ADDR = 75

配置D3_GICD_CHIPR<0>.ADDR = 75

配置D2_GICD_CHIPR<1>.ADDR = 82

配置D3_GICD_CHIPR<1>.ADDR = 82

配置D3_GICD_CHIPR<2>.ADDR = 5

//如下配置ADDR的步骤需要在DIE0 online之前完成:

配置D1_GICD_CHIPR<2>.ADDR = 82 (对应其中一路ccg的icdrtdest)

配置D1_GICD_CHIPR<3>.ADDR = 75(对应其中一路ccg的icdrtdest)

配置D2_GICD_CHIPR<3>.ADDR = 2(对应其中一路ccg的icdrtdest)

三、Bringing Chip0 online

- 配置GICD_CHIPR<0>.SPI_BLOCK_MIN & SPI_BLOCKS,由于die0 spi INTID 范围32-511,得出SPI_BLOCK_MIN = 0和SPI_BLOCKS =15;

- 配置GICD_CHIPR<0>.SocketState=1 使chip 0上线,并读取以下位域表明chip 0上线成功,处于连接状态;

- 读取GICD_CHIPR<0>,校验上述写入操作是否成功;

- 读取以下寄存器,如果读取数据与此一致,说明芯片 x 现在处于Consistent状态并准备好接受与系统配置中其他芯片的连接。

Check Sequence :

四.Chip0连接Chip1/2/3

将与DIE0连接的各die配置起来,此时需要配置DIE0的寄存器,(步骤四、五、六都需要配置)

- 配置GICD_CHIPR(1)

- 配置GICD_CHIPR<1>.ADDR = 2 (对应其中一路ccg的icdrtdest)

- 配置GICD_CHIPR<1>.SPI_BLOCK_MIN & SPI_BLOCKS

- 配置GICD_CHIPR<1>.SocketState=1 使DIE1上线

- 校验是否写入成功:

①.轮询GICD_DCHIPR.PUP=0,表示连接成功;

②.校验配置GICD_CHIPR<1>的值是否生效

- 配置GICD_CHIPR(2)

- 配置GICD_CHIPR<2>.ADDR = 82 (对应其中一路ccg的icdrtdest)

- 配置GICD_CHIPR<2>.SPI_BLOCK_MIN & SPI_BLOCKS

- 配置GICD_CHIPR<2>.SocketState=1 使DIE2上线

- 校验是否写入成功:

①.轮询GICD_DCHIPR.PUP=0,表示连接成功;

②.校验配置GICD_CHIPR<2>的值是否生效

- 配置GICD_CHIPR(3)

- 配置GICD_CHIPR<3>.ADDR = 75 (对应其中一路ccg的icdrtdest)

- 配置GICD_CHIPR<3>.SPI_BLOCK_MIN & SPI_BLOCKS

- 配置GICD_CHIPR<3>.SocketState=1 使DIE3上线

- 校验是否写入成功:

①.轮询GICD_DCHIPR.PUP=0,表示连接成功;

②.校验配置GICD_CHIPR<3>的值是否生效

五.Chip1连接Chip2/3

配置D1_GICD_CHIPR<2>

1. 配置D1_GICD_CHIPR<2>.ADDR = 82 (对应其中一路ccg的icdrtdest)

2. 配置D1_GICD_CHIPR<2>.SPI_BLOCK_MIN & SPI_BLOCKS

3. 配置D1_GICD_CHIPR<2>.SocketState=1 使DIE2上线

4. 校验是否写入成功:

①.轮询D1_GICD_DCHIPR.PUP=0,表示连接成功;

②.校验配置D1_GICD_CHIPR<2>的值是否生效

配置D1_GICD_CHIPR<3>

1. 配置D1_GICD_CHIPR<3>.ADDR = 75(对应其中一路ccg的icdrtdest)

2. 配置D1_GICD_CHIPR<3>.SPI_BLOCK_MIN & SPI_BLOCKS

3. 配置D1_GICD_CHIPR<3>.SocketState=1 使DIE3上线。

4. 校验是否写入成功:

①.轮询D1_GICD_DCHIPR.PUP=0,表示连接成功;

②.校验配置D1_GICD_CHIPR<3>的值是否生效

六.Chip2连接Chip3

配置D2_GICD_CHIPR<3>

1. 配置D2_GICD_CHIPR<3>.ADDR = 2(对应其中一路ccg的icdrtdest)

2. 配置D2_GICD_CHIPR<3>.SPI_BLOCK_MIN & SPI_BLOCKS

3. 配置D2_GICD_CHIPR<3>.SocketState=1 使DIE3上线

4. 校验是否写入成功:

①.轮询D2_GICD_DCHIPR.PUP=0,表示连接成功;

②.校验配置D2_GICD_CHIPR<3>的值是否生效

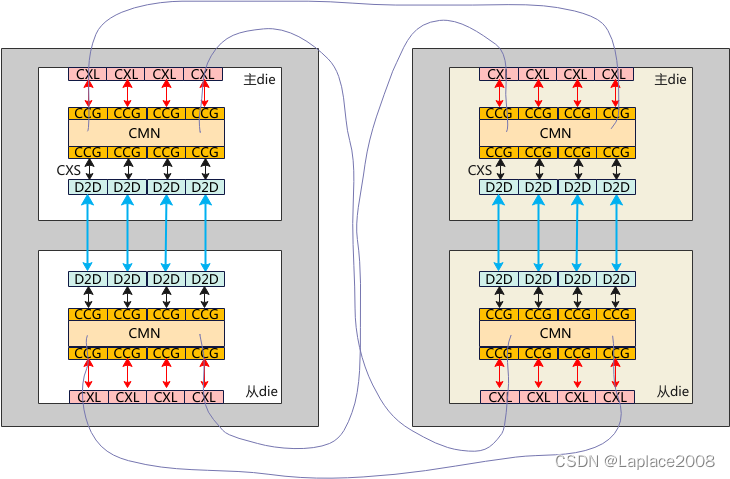

MultiChip连接方式

此处仅展示同一个socket内双die之间的连接方式和数据通路,以及双socket间不同die之间的连接方式和数据通路。

同一个socket内的两个die通信可以使用任一组D2D进行通信。

die间传输:数据流从主die CMN的CCG结点,转换成CXS接口信号,经过die2die将数据发到从die,从die经过die2die和ccg结点,将数据传输到cmn内部并做后续处理。

不同socket之间各die的通信:

不同类型的transaction通过CCG模块,经过CCIX链路转换成CXS接口所支持的flit数据包,flit数据包经过PCX16的CXS接口输入,在PCX16内部打包成TLP包,并经过链路层和物理层,发送到对端PCX16控制器。对端PCX16控制器完成解析,经过CCIX控制器后将数据包发到CCG结点,完成一次跨socket数据传输。

1025

1025

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?