在soc项目中,小到模块级验证,大到子系统或系统级验证,都有一项不可或缺的验证feature,那就是中断,同时中断也是验证检查清单中一项必需的check点。今天主要探讨一下中断的概念并总结一下SoC项目中针对中断的主流验证方法。

一、中断概述

1. 什么是中断?

关键词:中断 中断源

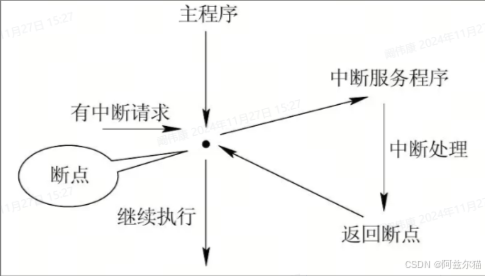

中断是指cpu对系统中发生某个事件做出的一种反应。cpu在运行过程中,当出现某些意外情况需要处理时,cpu能够停止正在执行的程序,保留现场后并自动执行相应的中断程序,待处理完后,又可以返回原被暂停的程序继续运行。

引起中断的事件或发出中断请求的来源称为中断源,中断源向cpu提出的处理请求称为中断请求。发生中断时,被打断程序的暂停点称为断点。

举个例子:

假如你是cpu,当前你正在书房看书(cpu执行程序),突然客厅的电话响了(中断请求),你需要打断看书的动作(保存现场,用书签记录看到了哪一页),去客厅接电话(中断服务程序),打完电话后回书房从打断的页继续看(恢复现场并继续执行原程序)。

倘若没有中断的,cpu只能通过查询的方式去poll某个状态或寄存器的值,这样会大大降低cpu的利用率。同时中断对整个设备的省电有极大的意义,当前若没有需要执行的命令,cpu可以进入休眠模式,当外设有业务需要cpu处理,可以以中断的方式将cpu唤醒,处理完之后cpu继续休眠,这样可以大大节省功耗。

2. 中断如何分类

关键词:中断分类

根据不同的标准可以将中断划分成不同的种类:

脉冲中断:持续时间较短,一般为一个或数个cycle

电平中断:一般持续多个时钟宽度,多用于维测性质的中断上报等

事件中断:外设业务触发,通知软件介入处理某些具体事务,比如完成一次dma数据搬运操作等,事件中断属于软硬件协同工作上的一环

异常中断:硬件不可预期的行为导致发生的错误,当发生中断时,硬件可能无法通过自身解决这种错误,需要cpu进行干涉

function中断:需要直接送到对应的cpu(gic)进行处理

safety中断:需要上报给safety island进行系统级安全处理

3.中断树与中断合并

中断树 中断合并 中断配套寄存器

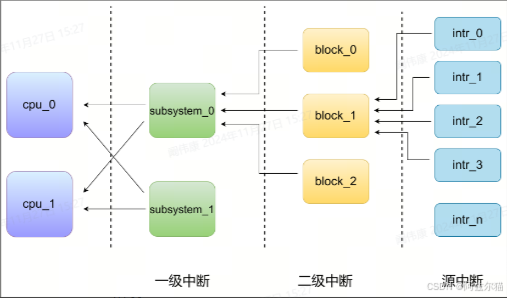

SoC中的中断树

在大部分soc芯片系统中,都会存在众多的外部中断源,比如业务上报中断,总线挂死中断,定时器中断,parity中断,ecc中断等,这些中断源都会经过多层级的子系统合并处理,最终接入到cpu的外部中断信号上,的称为soc中断树。

最接近cpu的一层为一级中断,向下依次为二级中断,三级中断…,最低端的称作源中断。

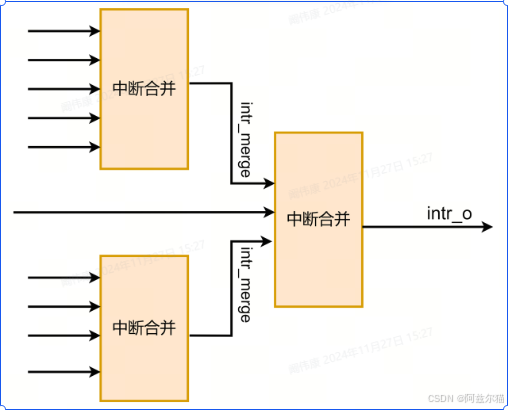

中断合并

在大型soc芯片中,往往cpu所能接收到的中断的数量是有限的,但soc所需要上报或产生异常的中断常常远大于cpu所能接收的中断数量,因此就需要在源中断产生的模块内部进行合并,或将源中断与其他模块的中断进行合并,合并成单个中断后再送到上一级模块,直到送到cpu入口。

中断并不是可以随意合并的,同时cpu在接收到一个中断时,需要知道具体是哪个中断,才能做出对应的处理,因此在进行中断合并时需要遵循一些原则:

- 中断合并一般按照相同类型的源中断进行。比如多个脉冲中断合并为一个脉冲中断/电平中断,多个电平中断合并为一个电平中断,电平合并成脉冲并不常见;function中断一般不与safety中断合并。

- block可以按照各自的需求将不同的中断进行分类。对于无实时性需求,不要求cpu立即响应的中断可以将中断合并输出;

- block内部的中断(源中断)需要有独立的mask,state和clear等中断配套寄存器,用于保证cpu可以通过这些寄存器逐级查询到源中断并进行处理。

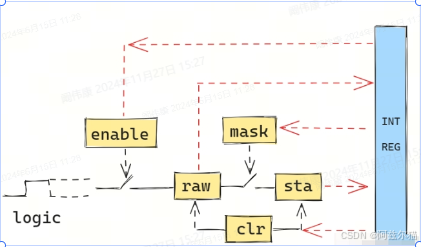

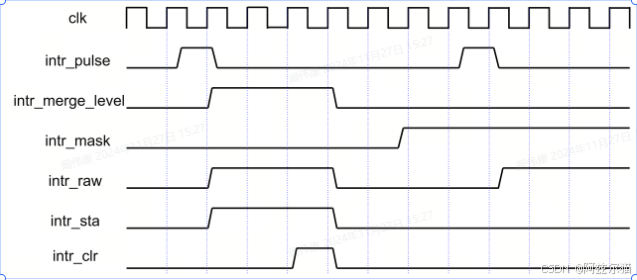

常见的中断配置寄存器:

- enable寄存器,用于控制是否产生中断信号;

- mask寄存器,中断屏蔽寄存器,当mask=1时会将产生的源中断屏蔽,当mask=0时会将产生的源中断输出;

- raw寄存器,原始中断状态寄存器,不管mask是何值,只要有源中断产生,该寄存器会自动置1;

- sta寄存器,中断状态寄存器,受mask寄存器控制,当mask=0时,sta寄存器的值与raw寄存器的值一致,mask=1时,中断被屏蔽掉,sta寄存器保持为0;

- clr寄存器,中断清除寄存器,用于清除中断。当cpu查询到源中断后,需要将sta和raw寄存器清除,否则sta一直保持为1,cpu会一直收到中断。clr寄存器配置1清除sta和raw。

同时,并不是所有的中断都包含clr寄存器,一般来说只有脉冲类型的中断才会配套clr寄存器。电平类型的源中断一般都是由源模块产生,cpu是无法通过clr寄存器清除。

二、通用中断验证方法

1.block级中断验证方法

对于模块级验证中断特性,验证人员首先要考虑中断是否与设计方案中描述一致(中断数量,中断类型,触发方式等),然后要考虑这些中断能否正常触发,能否正常上报和清除,中断清除后能否被再次触发,结合中断配套寄存器进行验证。在包含合并中断的模块,要确认能否根据上报的中断查询到源中断等。

1)中断信号的产生是否符合预期

中断是否可以按照设计文档中的描述正常产生,中断信号的触发形式(电平触发或脉冲触发,脉冲宽度等)是否与设计文档描述一致;

2)中断的上报,这个和具体功能无关,只验证中断的上报和中断配套寄存器功能正确性(中断屏蔽时中断信号不会上报到中断控制器,但是可以通过状态寄存器读到对应中断状态信息;中断的屏蔽和清除要精确到每一个中断等);

3)功能相关,在TC中构造异常激励多次触发中断,在验证结束时,检查中断状态,中断计数等信息;

4)为避免出现非预期中断出现的风险,验证环境也需要对中断进行持续监测,当预期中断拉高时进入中断服务程序,出现非预期中断时报错

2.系统级验证方法

对于系统级验证,验证人员的工作重点不再是底层中断功能的实现,而是要考虑各个模块,各个子系统的中断集成的正确性,中断线是否正确送到中断控制器,送到中断控制器的中断是否正常发送到cpu中断管脚等

1)集成连线的正确性

主要检查是否有漏接或错接的情况,一般通过独热码的方式逐一force起发起端信号,检查接收端所有中断信号,每次理应只有一个对应的信号拉起

2)执行中断服务函数

中断上报到中断控制器后,中断控制器是否正常上报到cpu进行处理,一般需要从软件的角度做端到端的验证。

同时也可以对发起端和接收端中断信号的形式进行覆盖,比如发起端中断是低电平有效,接收端认为是高电平有效,那么在集成时就需要添加取反逻辑。如果忘记添加取反逻辑,在芯片上电,cpu使能中断控制器后,cpu会不停执行中断服务程序,陷入死循环

一旦中断上报,中断服务程序执行中一般要通过访问一堆寄存器来确认是哪个源中断,从验证角度看,同时需要保证与此相关的配置寄存器的正确性,一般主要是状态寄存器。

3)中断优先级

当多个中断同时触发时,系统会先处理哪个中断,这个一般有接收端cpu决定,在最初一般规定中断号越小,中断优先级越高。后来随着中断控制器GIC的引入,可以通过配置GIC寄存器决定各个中断的优先级

4)cpu自身的中断

cpu一般作为中断接收端,但是cpu也有自己的中断,比如计时器中断,软件中断等,这部分的验证需要结合设计手册或官方文档描述配置产生中断进行验证

5)和block级类似,在chip级进行验证时也需要对非预期中断进行监控,当预期中断拉高时进入中断服务程序,出现非预期中断时报错

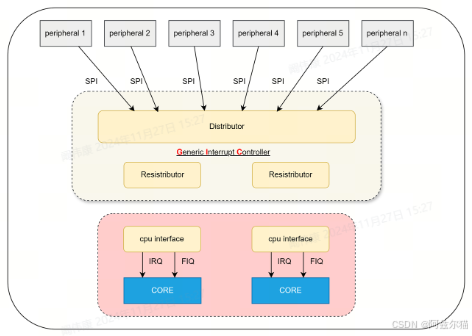

3.arm通用中断控制器和验证方法

在大型soc芯片中,随着外设中断的增多,通常使用中断控制器GIC对中断进行统一管理。外设中断通常是以SPI(shared peripheral interrupt,共享外设中断)的形式传输到GIC,下图中也仅画出了与此相关的SPI中断。

以当前项目所使用的GIC600AE为例,SPI支持如下特性:

支持独立配置每个spi的路由目标

支持独立配置每个spi的触发类型(边沿触发或电平触发)

支持独立配置每个spi的优先级

最大支持960个SPIs,中断号范围32-991

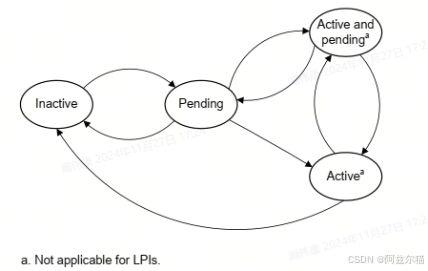

对于SPI中断,中断控制器的状态有以下4种:

- Inactive:中断源未触发,出于无效状态;

- Pending:中断处于有效状态,但cpu还没有响应该中断;

- Active:cpu在响应该中断;

- Active&Pending:cpu在响应该中断,但是该中断源又发送过来该中断。

中断处理流程,包含了以下几步:

1)GIC决定每个中断的使能状态,不使能的中断,是无法将中断传递到cpu;

2)如果某个中断的中断源有效,GIC将该中断的状态设置为pending状态,然后判断该中断的目标core;

3)对于每一个core,GIC将当前处于pending状态的优先级最高的中断,发送给该core的cpu interface;

4)cpu interface接收GIC发送的中断请求,判断优先级是否满足要求,如果满足,就将中断通过FIQ或IRQ管脚,发送给core;

5)core响应该中断,通过读取 ICC_IAR 寄存器,来认可该中断。读取该寄存器,如果是软中断,返回源处理器ID,否则返回中断号;

6)当core认可该中断后,GIC将该中断的状态,修改为active状态;

7)当core完成该中断后,通过写 EOIR (end of interrupt register)来实现优先级重置,写 ICC_DIR 寄存器,来无效该中断。

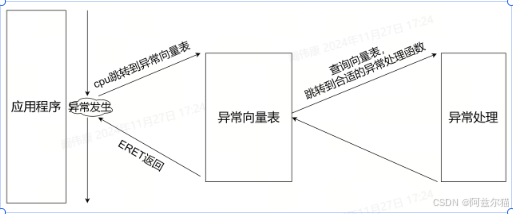

软件层面中断的触发和返回

当有中断发生时,cpu会自动(硬件层面)将PSTATE寄存器的值保存到SPSR,将返回地址的值保存到ELR,并将PSTATE中的D,A,I,F标志位置1,然后跳转到中断向量表;

软件根据中断的类型,在中断向量表中找到对应的入口,在中断向量表中的每一项都有一个跳转指令,用于跳转到恰当的异常处理函数并进行异常处理;

当异常处理完成后,通过调用ERET指令可以从异常返回,该指令会自动将PC指针从ELR恢复,同时将PSTATE从SPSR恢复出来。

对该部分的验证,主要关注点在于IP所支持的特性的验证,比如所支持的SPI的中断优先级,中断路由验证等。

对于SPI中断需要做如下部分的验证:

1)从中断控制器SPI输入接口依次拉起中断,结合GIC寄存器配置,验证是否所有的spi中断都可以被cpu正常响应;

2)多个SPI中断同时拉起时,cpu是否正确按照所配置优先级进行处理;

3)SPI中断路由验证,一般soc系统中不止存在一个cpu,将不同的spi中断配置路由到不同的cpu处理,验证cpu能否接收到对应的中断并正确处理。

784

784

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?