前言

本博文承接博文 https://blog.youkuaiyun.com/wenhao_ir/article/details/145663029 。

本博文和博文 https://blog.youkuaiyun.com/wenhao_ir/article/details/145663029 的目录是找出百问网(100ask)的IMX6ULL开发板与NXP官方提供的公板MCIMX6ULL-EVK(imx6ull14x14evk)在以太网硬件实现上的不同,进而去修改NXP官方提供的公板的BSP里的u-boot,使得u-boot能正常初始化以太网。

由于是要找出不同,所以本篇博文就一边研究芯片(LAN8720A)与MAC(以太网控制器)的每个连接,一边对比看有没有什么不同。

注意:物理层芯片(LAN8720A)只支持“RMII”协议,不像物理层芯片KSZ8081RNB那还还支持“MII”协议。

相关的实现协议:“RMII”已经在博文https://blog.youkuaiyun.com/wenhao_ir/article/details/145663029中介绍过了。

原理图下载地址

百问网(100ask)的IMX6ULL开发板的原理图的百度网盘下载地址:

https://pan.baidu.com/s/1YqW8V3eQ42gD9FfZ2jf-Mw?pwd=g6e1

芯片(LAN8720A)的Data sheet下载地址

芯片(LAN8720A)的Data sheet的百度网盘下载地址

https://pan.baidu.com/s/1ZCVbzF2QH1SYCKOtnvSUWg?pwd=7i7a

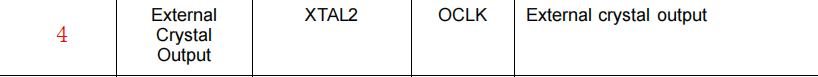

芯片(LAN8720A)的封装图

芯片(LAN8720A)的模块结构图

芯片(LAN8720A)对引脚Buffer Types的描述

关于Buffer Types的详情说明,见我的另一篇博文,https://blog.youkuaiyun.com/wenhao_ir/article/details/145703444

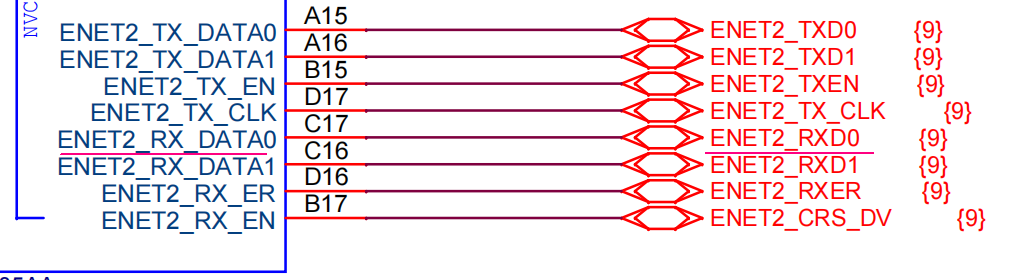

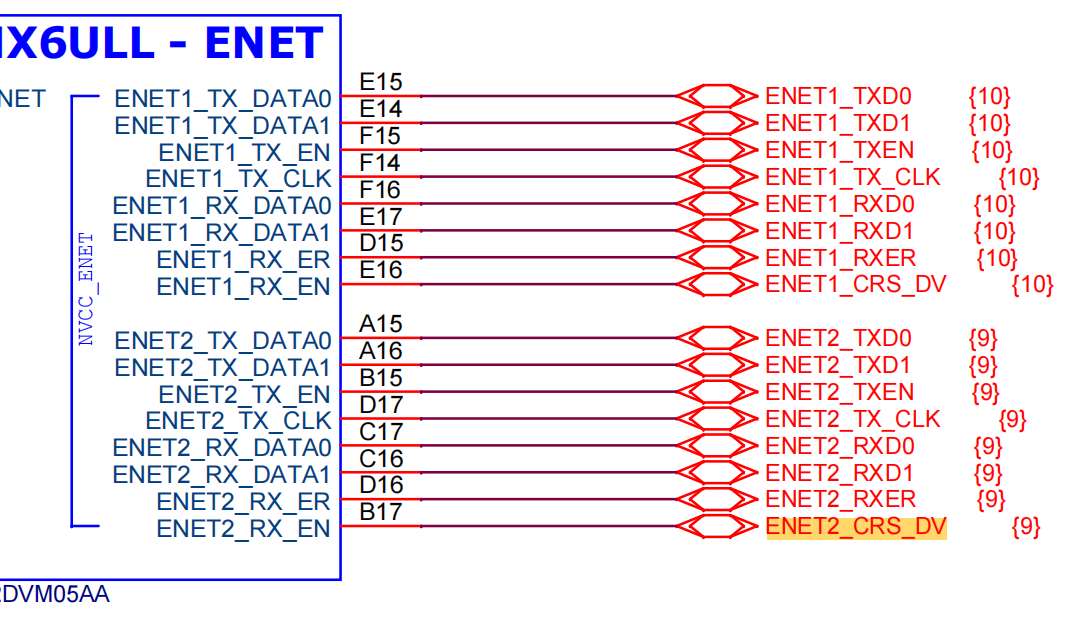

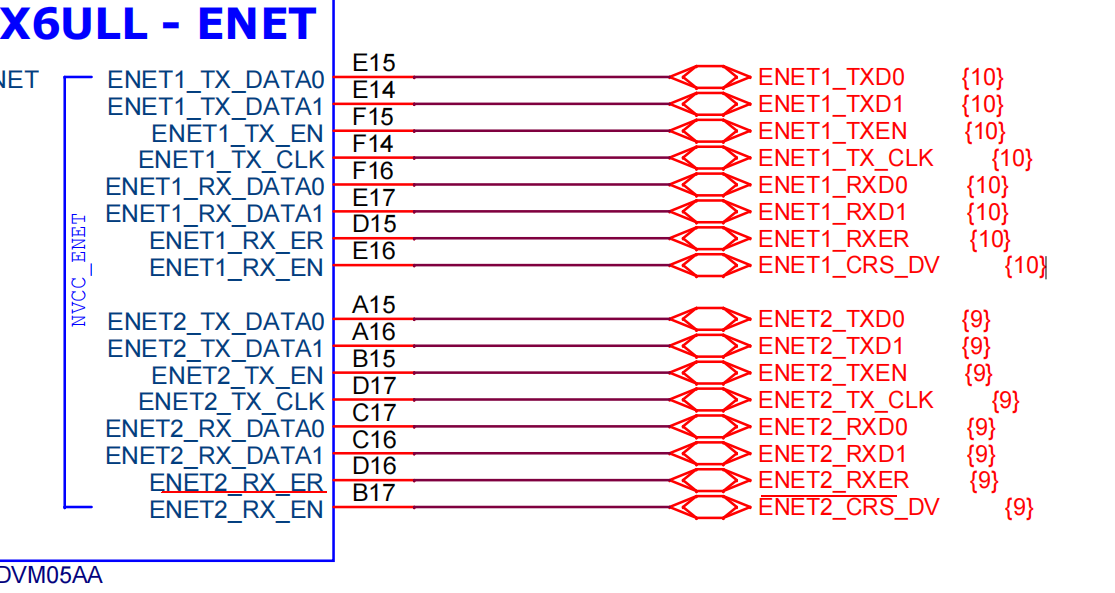

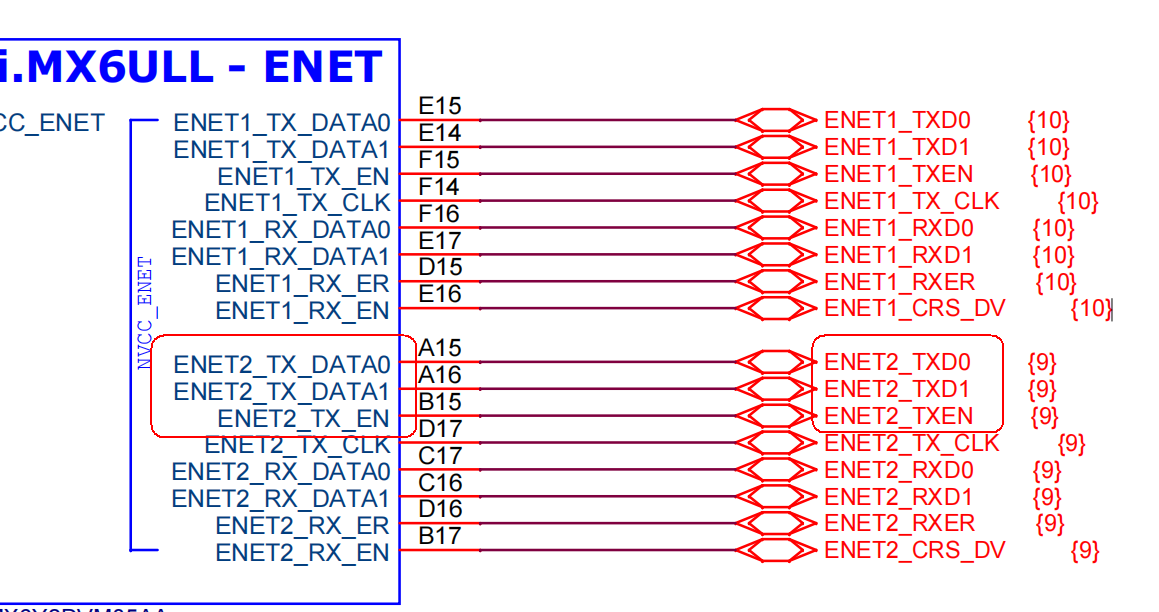

原理图中MAC(以太网控制器)的相关部分

打开原理图文件:“\06_开发板原理图\02_Core_board(核心板)\MYC-Y6ULX1211.pdf”

翻到第7页,就有MAC(以太网控制器)的相关原理图,截图如下:

两个物理层芯片的寄存器的相关设置是一样的(两个板子的相关代码是通常用)

这篇博文有一个目的,就是要搞清楚公板的以太网实现与开发板的以太网实现有何区别,当然最大的区别就是物理层芯片不一样,不过,光知道物理层芯片不一样是不行的,还要搞清楚二者有何使用上的差别。

通过查阅相关资料,我发现两个芯片都是利用由引脚MDIO 和引脚MDC构成的“SMI(Serial Management Interface)”接口来读取和写入寄存器的,这是它们的共同点,而两个板子中引脚MDIO 和引脚MDC与主机的连接都是相同的,所以我们只需要去看二者的寄存器一不一样,就知道在寄存器配置上二者是否一样了。

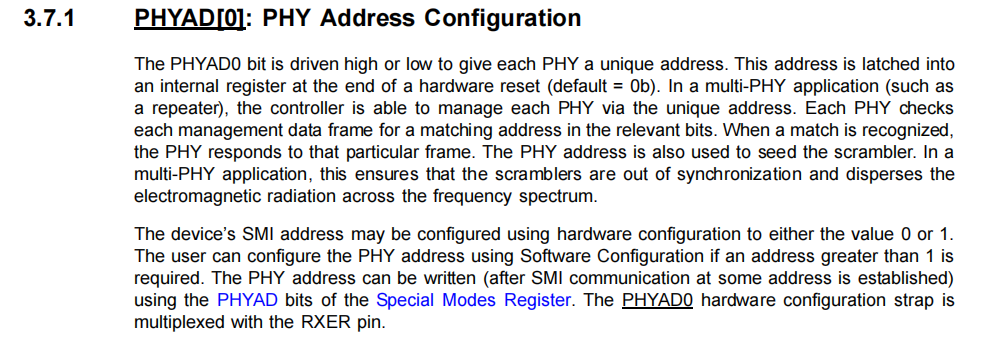

两个物理层芯片的寄存器映射表

物理层芯片KSZ8081RNB的寄存器映射表的截图如下:

物理层芯片LAN8720A的寄存器映射表的截图如下:

从两个芯片的寄存器映射表可以看出,最主要的前4个寄存器(索引值为0~3)的名称都是一样的。

物理层芯片LAN8720A的寄存器的个数明显是少于物理层芯片KSZ8081RNB的,原因很简单,因为物理层芯片KSZ8081RNB不仅支持RMII协议,还支持MII协议呀。

两个物理层芯片的Basic Control Register寄存器的详情

我们再看下具体的各寄存器的意义一不一样,以索引值为0的寄存器Basic Control Register为例,我们来看一看。

物理层芯片KSZ8081RNB的0号寄存器Basic Control Register的详情截图如下:

物理层芯片LAN8720A的0号寄存器Basic Control Register的详情截图如下:

可见,二者是完全兼容一致的。

我又看了下1号寄存器的前几位,发现也是一样的:

结论:两个板子的相关代码是通用的

综上,我们可以得出结论,两个板子通过两个物理层芯片的寄存器设置其功能和模式的相关代码是通常用。

通过原理图提取物理层芯片的相关引脚

以太网1的相关引脚提取

说明:百问网的开发板,以太网1的物理层芯片不像公板那样,是放在底板的原理图中的,而是放到核心版中的,以太网2的物理层芯片才像公板那样,是放在底板的原理图中的。

打开原理图文件:“\06_开发板原理图\02_Core_board(核心板)\MYC-Y6ULX1211.pdf”

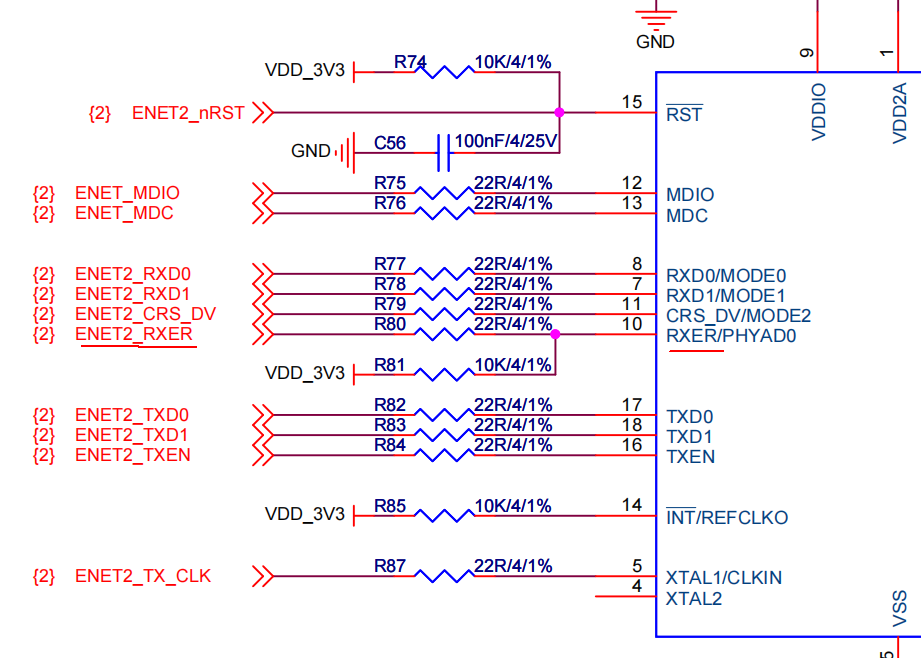

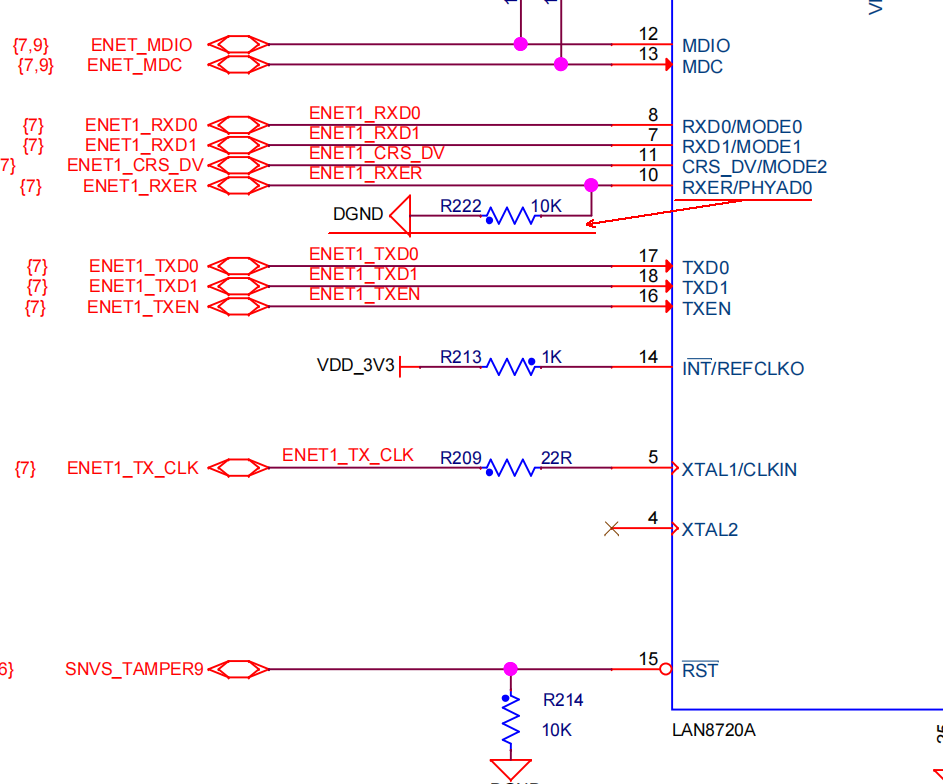

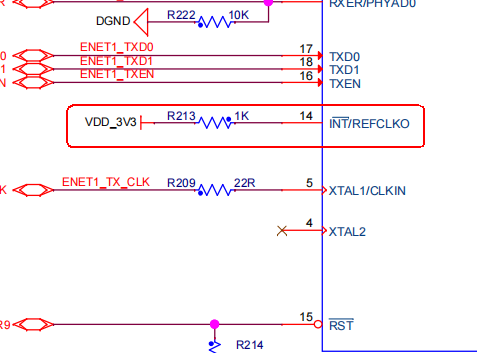

翻到第10页,就能发现以太网1的MAC控制器所连接的物理层芯片(LAN8720A)的原理图了,截图如下:

我们感兴趣的引脚提取如下:

MDIO

MDC

RXD0/MODE0

RXD1/MODE1

CRS_DV/MODE2

RXER/PHYAD0

TXD0

TXD1

TXEN

INT/REFCLKO

XTAL1/CLKIN

XTAL2

RST

可见,一共有13个我们感兴趣的引脚。

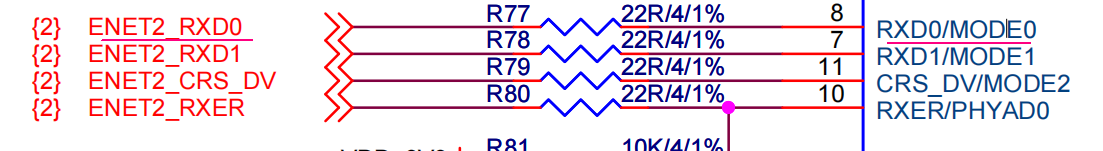

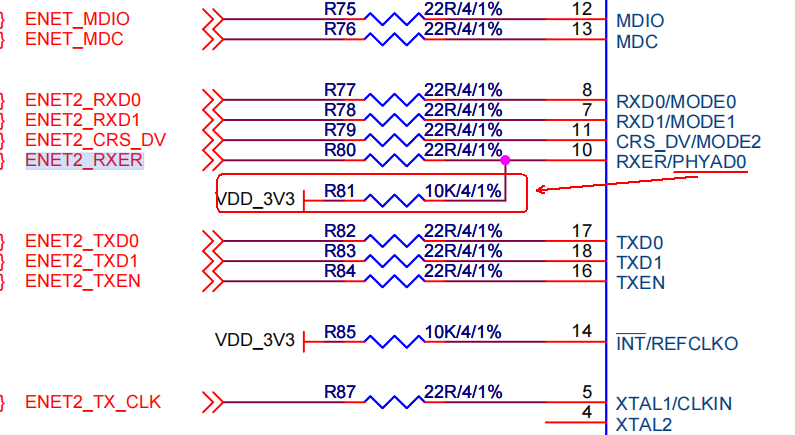

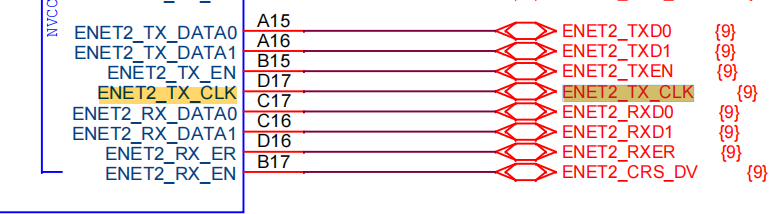

以太网2的相关引脚提取

说明:百问网的开发板,以太网1的物理层芯片不像公板那样,是放在底板的原理图中的,而是放到核心版中的,以太网2的物理层芯片才像公板那样,是放在底板的原理图中的。

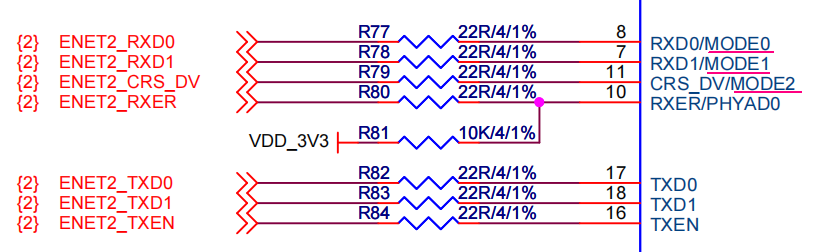

打开原理图文件:“\06_开发板原理图\01_Base_board(底板)\100ask_imx6ull_v1.1.pdf”

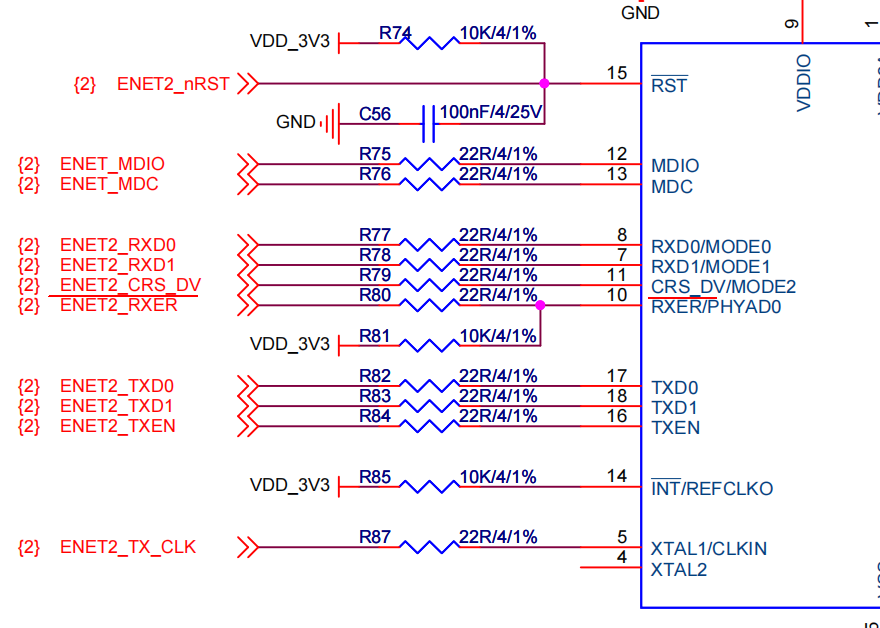

翻到第10页,就能发现以太网1的MAC控制器所连接的物理层芯片(LAN8720A)的原理图了,截图如下:

RST

MDIO

MDC

RXD0/MODE0

RXD1/MODE1

CRS_DV/MODE2

RXER/PHYAD0

TXD0

TXD1

TXEN

INT/REFCLKO

XTAL1/CLKIN

XTAL2

可见,一共也有13个我们感兴趣的引脚。

接下来,我们就来分析这些引脚的连接情况。

为什么从以太网2的物理层芯片开始分析?

很简单:因为官方提供的移植教程只分析了以太网2的连接情况,其实以太网1和以太网2的连接情况基本上是一样的。

以太网2的物理层芯片各引脚连接情况分析

在本篇博文的上面,已经提取了以太网2的物理层芯片各个感兴趣的引脚,接下来就开始分析。

引脚RST(nRST)【与公板不一样】

功能: 用于对 PHY 芯片进行硬件复位。通过将该引脚拉低,PHY 可以被复位,恢复到初始状态。

相关原理图如下:

可见,这个复位引脚是直接连到处理器的SNVS_TAMPER6引脚上的,而通过博文 https://blog.youkuaiyun.com/wenhao_ir/article/details/145663029 我们可以知道,公板的物理层芯片KSZ8081RNB的复位引脚是连接到74LV595PW芯片上的,74LV595PW 是一款 8位串行输入/并行输出 移位寄存器(Shift Register)芯片,74LV595PW连接到处理器,由处理器驱动它产生复位信号。

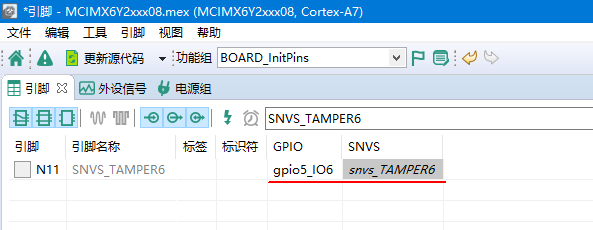

所以复位信号的来源就大不一样了,所以我们要去修改u-boot的代码让引脚的SNVS_TAMPER6产生复位信号。引脚SNVS_TAMPER6上可以分配的信号如下面截图所示:

所以,显然,我们应该是让GPIO5_IO6来产生这个复位信号。

信号snvs_TAMPER6是输入型的,所以不行。在 i.MX6ULL 系列芯片中,信号 snvs_TAMPER6 是 SNVS(Secure Non-Volatile Storage) 子系统的一部分,专门用于 防篡改(Tamper Detection)功能。具体来说,snvs_TAMPER6 是 SNVS 系统中的一个输入信号,通常用于检测外部环境是否存在恶意或非正常篡改行为,比如物理攻击、温度异常、电压不稳定等。

引脚MDIO和MDC【与公板一样】

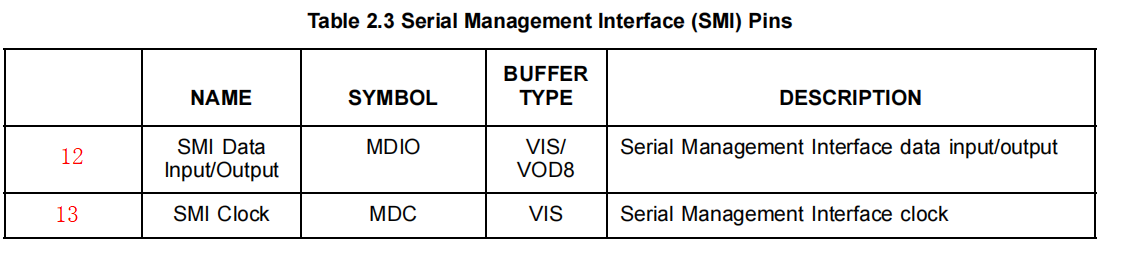

MDIO 是一种串行数据线,通过MDC引脚传来的时钟信号进行同步,用于在主机和 PHY 之间传输控制信息,这种串行控制接口在芯片(LAN8720A)的Data sheet中被称为“SMI”。

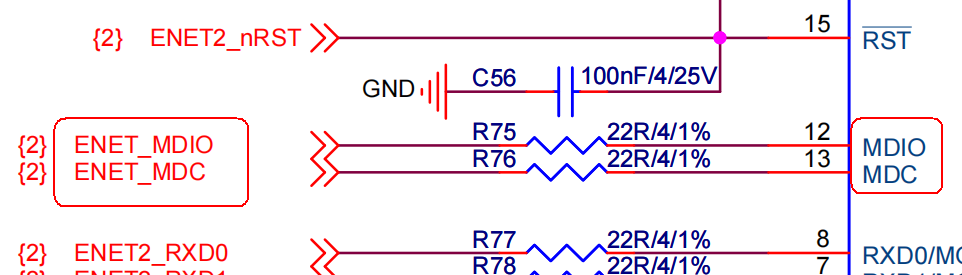

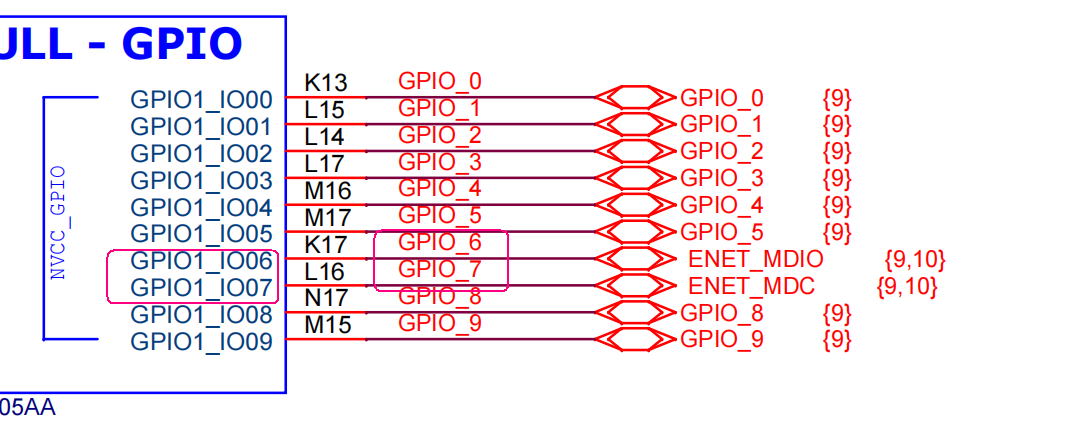

相关原理图如下:

可见,引脚MDIO连接是的GPIO1_IO06,而引脚MDC连接的是GPIO1_IO07。

这与公板的连接情况是相同的。

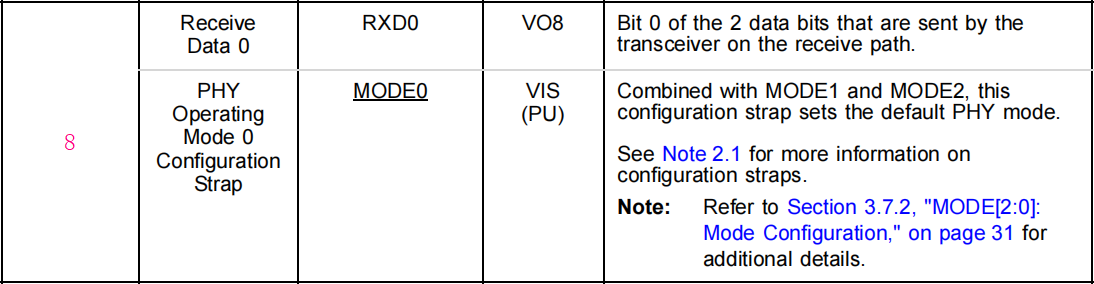

引脚RXD0/MODE0【RXD0与公板一样;MODE0虽然与公板不一样,但不影响】

RXD0功能: 物理层芯片收到来自网线的数据后需要发给IMX6ULL的MAC(以太网控制器),RXD0就表示发送数据的第0位,注意,是发送数据哈,不是接收数据,这里的发送和接收是在MII/RMII框架的基础上来说的,而MII/RMII框架是把MAC(以太网控制器)作为主端的,即发送和接收是相对于MAC(以太网控制器)来说的。

RXD0显然应该是连接到以太网2的MAC的ENET2_RX_DATA0引脚的,相关相关原理图如下:

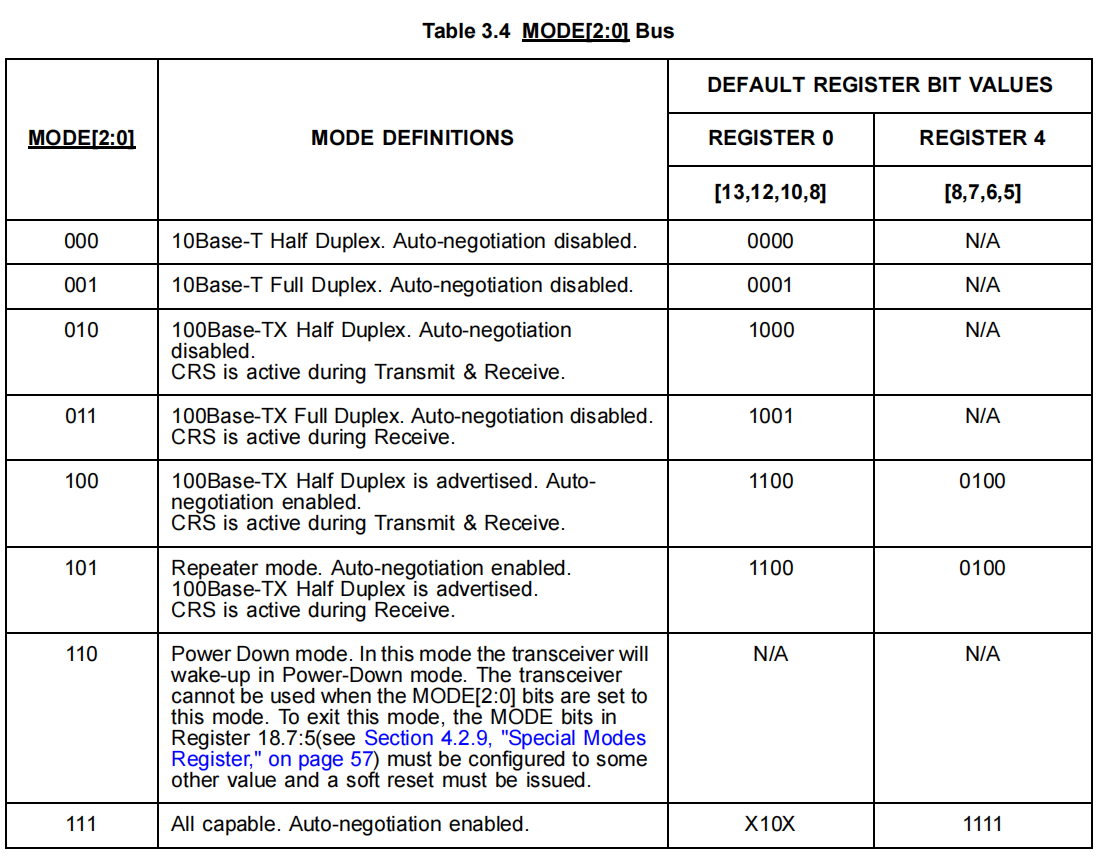

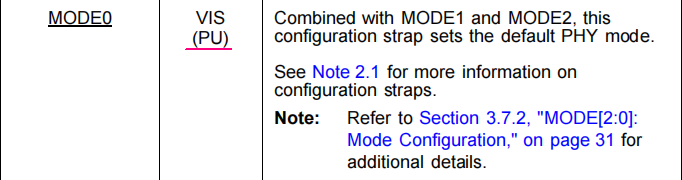

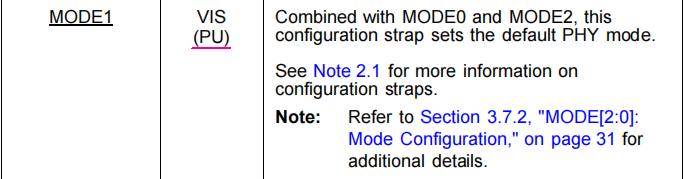

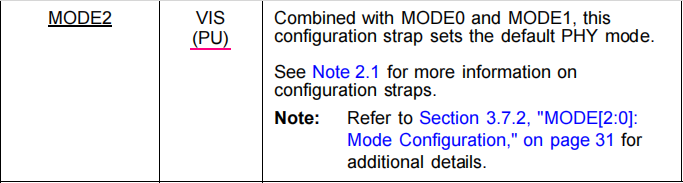

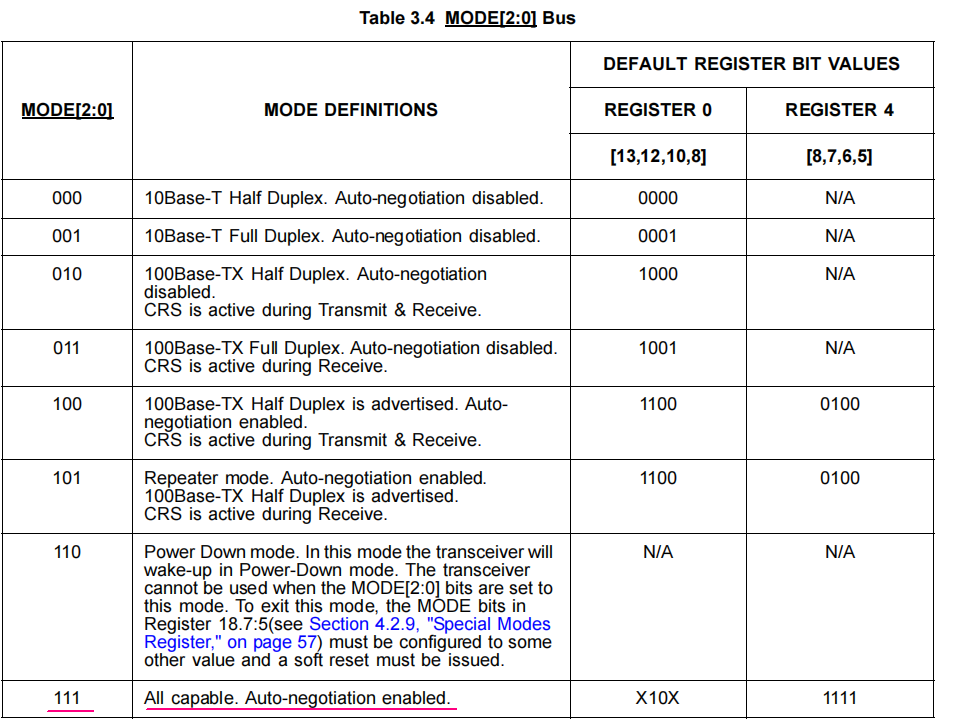

MODE0-MODE1-MODE2对芯片模式的配置

其复用功能MODE0与MODE1、MODE2一起用来配置物理层芯片LAN8720A的模式。

配置详情如下:

我们看下百问网(100ask)的开发板是如何设置这几个的电平值的,当然配置方式依然和博文 https://blog.youkuaiyun.com/wenhao_ir/article/details/145663029 中那样,在复位信号解除有效时,其值被锁存。

相关的原理图如下:

从这个原理图中,我们可以看出,根本就没有相关电路去设置,那就用的是其默认值了,那默认值是多少呢?查Data sheet呗。

上面截图中的PU表示内部有上拉电阻,VIS的详细解释见我的另一篇博文 添加链接描述

上面截图中的PU表示内部有上拉电阻,VIS的详细解释见我的另一篇博文 添加链接描述

所以,在这里,MODE0-MODE1-MODE2组成的值为111,对应的模式如下表所示:

即在速率和双工模式上,芯片处于自动协商模式(Auto-negotiation),它会与网线另一端的物理层芯片进行自动协商速率和双工模式,详情见 https://blog.youkuaiyun.com/wenhao_ir/article/details/145704025

当然这个模式也可以在中途通过软复位并通过引脚MDC和MDIO组成的SMI串口通信接口来设置,详情见下面这段描述:

上面这段的解释如下:

-

MODE[2:0] 配置带:

MODE[2:0]是一个 3 位配置带(即硬件跳线或焊接的引脚),它控制着 LAN8720A 的 10/100 Mbps 数字模块的配置。通过配置这 3 个引脚,可以选择不同的工作模式,比如选择 10 Mbps 或 100 Mbps 的工作模式。

-

nRST 引脚复位功能:

- 当芯片的 nRST(复位引脚)去复位(即去掉低电平信号,复位解除),芯片内部的寄存器值会根据 MODE[2:0] 配置带的设置来加载。也就是说,芯片初始化时,这些跳线引脚的状态会决定数字模块的初始配置。

-

软复位:

- 软复位是通过基本控制寄存器(Basic Control Register)中的“软复位位”(Soft Reset bit)来实现的。当执行软复位时,芯片内部的 10/100 数字模块配置将由寄存器中的值控制,而 MODE[2:0] 配置带将不再起作用。

-

用户配置模式:

- 用户可以通过 SMI(Serial Management Interface) 操作寄存器来配置芯片的工作模式。这些寄存器允许用户通过软件来进一步配置 LAN8720A 的工作模式,例如选择速度或工作模式等。

总结一下:

- MODE[2:0] 配置带用于芯片初始化时配置 10/100 数字模块的工作模式。

- 当芯片被复位(nRST去复位)时,配置会根据 MODE[2:0] 的状态来加载。

- 在软复位后,配置将由寄存器控制,MODE[2:0] 将不再起作用。

- 用户可以通过 SMI 操作寄存器来手动配置芯片的工作模式。

简单来说,MODE[2:0] 配置带在芯片启动时控制工作模式,但一旦软复位发生,寄存器配置会替代它的作用,允许更灵活的控制。

公板的物理层芯片中的相关模式

很遗憾的是,公板的物理层芯片KSZ8081RNB的MODE[2:0] 配置带是用来选择下面的模式的:

即到底是MII模式还是MII back-to-back模式还是RMII模式,而不是速率模式和双工模式的选择。

所以我们需要去看物理层芯片KSZ8081RNB的Data sheet。

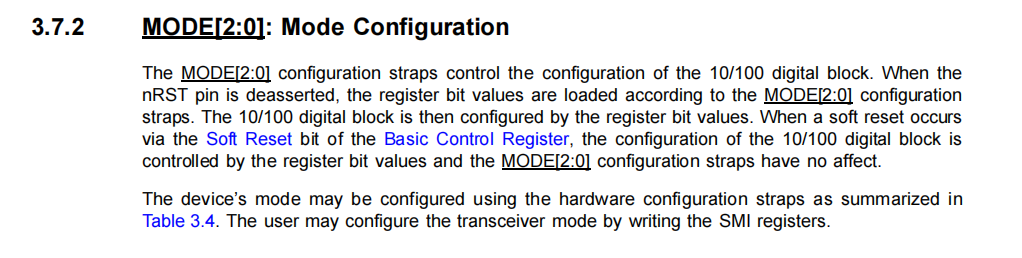

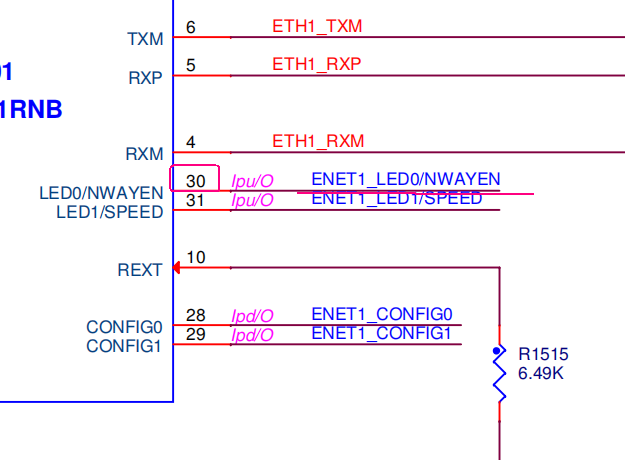

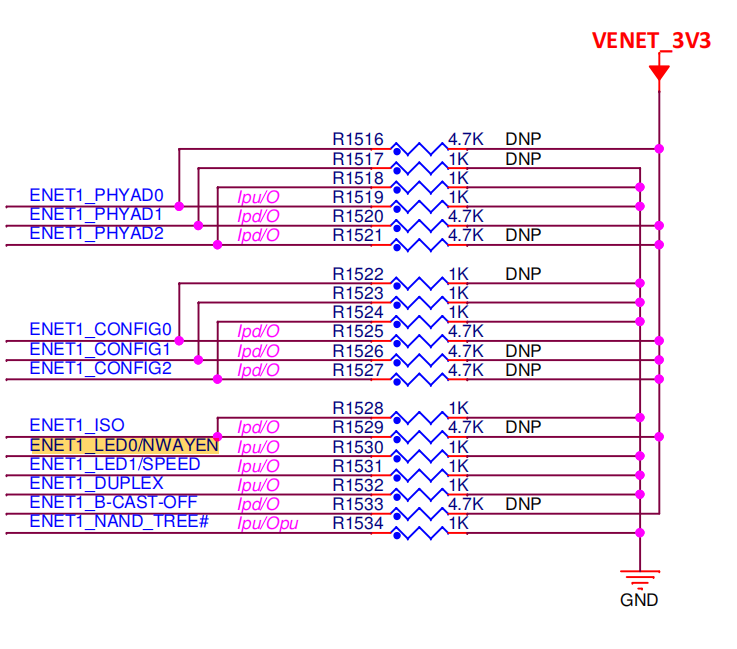

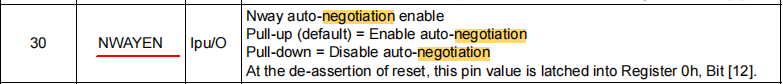

不妨在物理层芯片KSZ8081RNB的Data sheet里搜索关键词“negotiation”,有了,如下图所示:

可见,如果在复位信号解除有效时,其值为高电平,则启用自动协商模式(Auto-negotiation),如果其值为低电平,则禁用自动协商模式(Auto-negotiation)。

公板中的相关原理图如下:

DNP 是 “Do Not Populate” 的缩写,表示“不要焊接”或“不要安装,而ENET1_LED0/NWAYEN连接的线是上面第3组的第3根,所以没有影响。所以在复位信号解除有效时,其值被锁存为低电平0。根据下面这幅截图:

结论:虽然速率和双工模式不一样,但不影响程序

从上面截图中我们知道它是禁用了自动协商模式(Auto-negotiation)的,即公板中是禁用了自动协商模式(Auto-negotiation)的。

这就与百问网的开发板不一样了,百问网的开发板是启用了自动协商模式(Auto-negotiation)的,不过根据博文 https://blog.youkuaiyun.com/wenhao_ir/article/details/145704025 我们可以知道的是自动协商与MAC(以太网控制器)无关,它实际上是两个物理层芯片通过网线进行协商的行为,所以这并不影响我们的程序。

引脚RXD1/MODE1【 RXD1与公板一样】

略,RXD1引脚肯定和公板相同的,至于MODE1引脚,在对引脚RXD0/MODE0的介绍中已经说得很清楚了,所以也略过了。

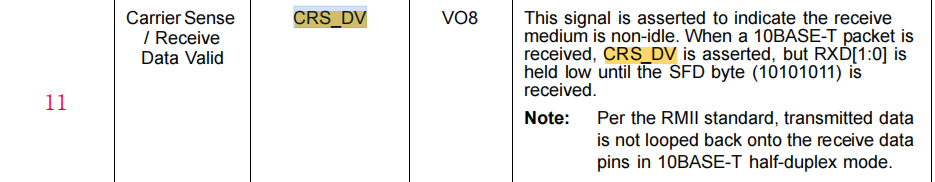

引脚CRS_DV/MODE2【CRS_DV与公板一样】

这段话主要是在描述 LAN8720A 物理层芯片中的 CRS_DV 引脚的功能,以及它在接收 10BASE-T 数据包时的行为。我们来逐步解析这段话的意思:

-

CRS_DV 的作用:

- CRS_DV 是一个 接收状态信号,它的作用是指示接收介质是否处于非空闲状态。

- asserted 意味着该信号被激活(通常是低电平或高电平,取决于具体芯片设计)。当 CRS_DV 被激活时,表示 接收数据介质 上有数据正在传输,也就是说,接收到的数据不是空闲的。

-

10BASE-T 数据包的接收:

- 注意:这里只是以

10BASE-T 数据包为例进行说明,实际上100BASE-T 数据包也是同样的,并不是说100BASE-T 数据包下,CRS_DV信号就没有被使用了,实际上在上100BASE-T 数据包的情况下也是一样的。 - 当接收到 10BASE-T 数据包 时,CRS_DV 信号会被激活(asserted)。

- RXD[1:0] 是接收数据引脚,它们将接收到的数据传递给上层。根据这段描述,RXD[1:0] 在 CRS_DV 激活时 会被 保持为低电平,直到接收到 SFD(Start Frame Delimiter)字节。

- SFD 字节 是每个以太网帧的开始标志,通常为 10101011(二进制)。当接收到这个字节后,RXD[1:0] 会开始传输实际的数据。

- 注意:这里只是以

-

SFD 字节:

- SFD(Start Frame Delimiter,帧开始定界符)是以太网帧的开始标志。它帮助接收端识别数据帧的起始位置。该字节的值为 0xAB(即 10101011),当接收端检测到这个字节时,它开始将接收到的帧数据传递到 RXD 引脚。

-

注意事项:

- Per the RMII standard, transmitted data is not looped back onto the receive data pins in 10BASE-T half-duplex mode.

- 根据 RMII(Reduced Media Independent Interface)标准,在 10BASE-T 半双工模式 下,发送的数据不会通过 接收数据引脚 (RXD)进行回环。

- 这意味着,在半双工模式下,发送的数据不会被直接反馈到接收引脚(RXD),因此接收端不会看到自己发送的内容。这个特点是与 全双工模式 不同,在全双工模式下,发送和接收可以同时进行,且数据可以回环到接收引脚。

- Per the RMII standard, transmitted data is not looped back onto the receive data pins in 10BASE-T half-duplex mode.

总结:

- CRS_DV 信号被激活时,表示接收到的数据正在传输(即,介质不空闲)。当接收到 10BASE-T 或100BASE-T数据包时,CRS_DV 被激活,但 RXD[1:0] 会保持低电平直到接收到 SFD 字节(10101011)为止,此时开始传输实际的数据。

- 在 10BASE-T 或100BASE-T的半双工模式 下,发送的数据不会通过接收引脚回环,因此不会出现在 RXD 引脚上。

百问网的开发板的原理图如下:

可见,引脚CRS_DV的连接与公板是一样的。

至于MODE2引脚,在对引脚RXD0/MODE0的介绍中已经说得很清楚了,所以就略过了。

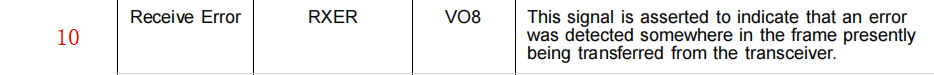

引脚RXER/PHYAD0【RXER与公板一样但PHY地址的设置不一样】

RXER 是接收错误信号,当物理层芯片KSZ8081RNB接收到错误的帧时该引脚会变为高电平,进而通知处理器的MAC出现错误帧。

开发板中的相关原理图如下:

可见 RXER引脚的连接是与公板中的连接相同的。

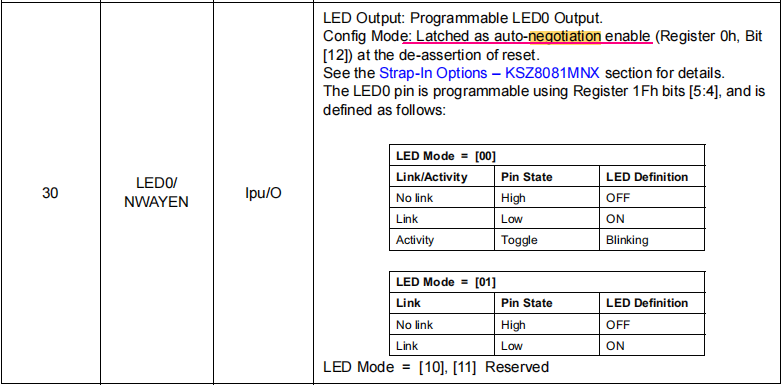

开发板中两个以太网MAC控制器对应的是哪个物理层芯片(芯片LAN8720A设置PHY地址的方法)

但是对于引脚复用的PHYAD0那就和公板中的物理层芯片KSZ8081RNB有挺大的区别了。

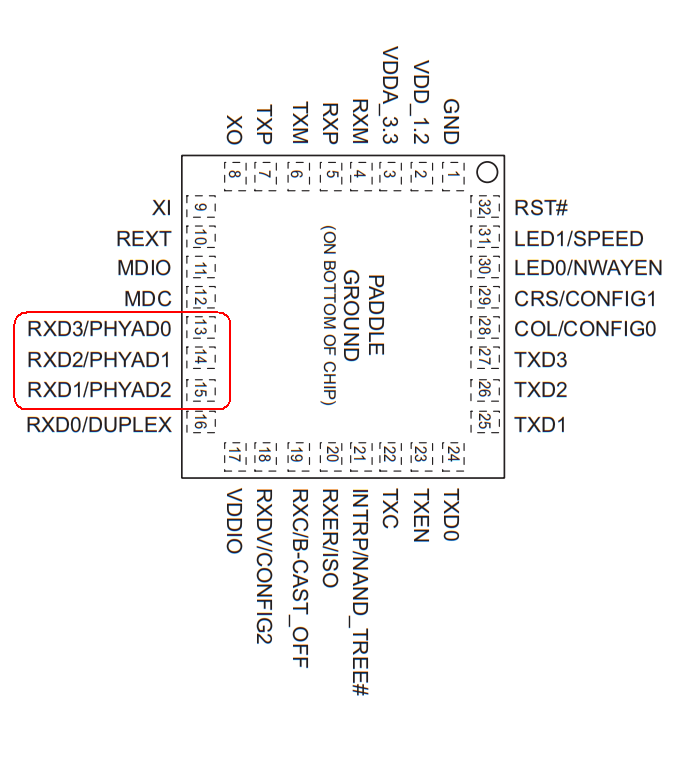

公板中的物理层芯片KSZ8081RNB有三个引脚用于在初始化的时候组成芯片的PHY地址的配置带,分别为:RXD3/PHYAD0、RXD2/PHYAD1、RXD1/PHYAD2,如下图所示:

通过回顾博文:https://blog.youkuaiyun.com/wenhao_ir/article/details/145663029 我们知道在公板中,PHY地址1对应的以太网2,PHY地址2对应的是以太网1,我当时还在博文中评价道,刚好相反,设计者真2。

但是物理层芯片LAN8720A却只有一个引脚,即引脚RXER/PHYAD0用于设置PHY地址的第0位,所以当PHY地址超过1时,就需要通过内部的寄存器来设置另外两位PHY地址了。

我们首先看下在开发板PHYAD0的电平设置,相关电路原理图如下:

可见PHYAD0在在复位信号解除有效时,被锁存的值为高电平,即逻辑值1,所以在开发板中,以太网2对应的物理层芯片的PHY地址的最低位为1。

我们看下另外一块物理层芯片:

打开原理图文件:“\06_开发板原理图\02_Core_board(核心板)\MYC-Y6ULX1211.pdf”,翻到第10页:

所以,很明显,开发板的以太网1对应的物理层芯片的PHY地址的最低位为0。

如果要设置PHY地址的另外两位怎么办呢?

答:通过设置其内部寄存器来设置呗,内部寄存器的设置通过引脚MDIO和MDC组成的“SMI”接口来实现。

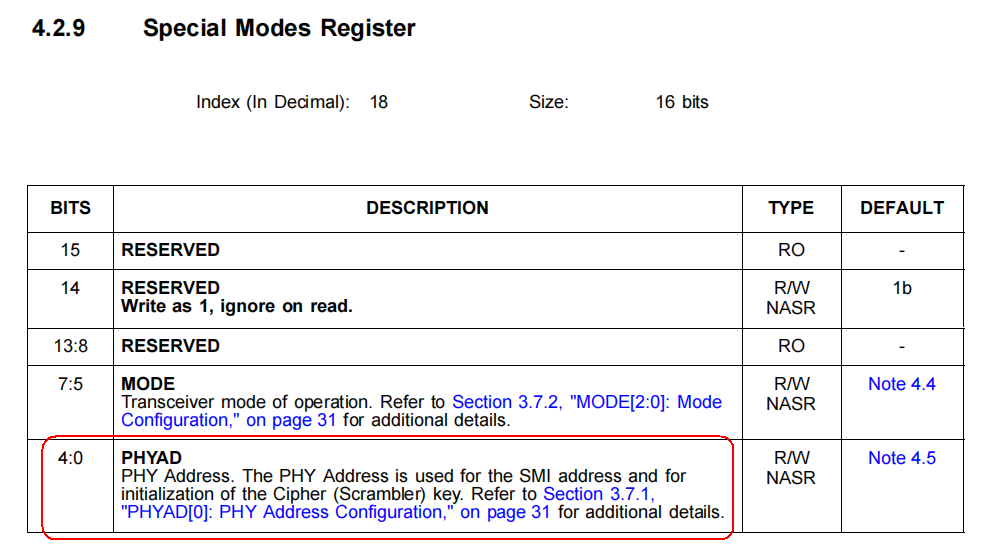

我们查看下物理层芯片LAN8720A的Data sheet中的相关说明:

The PHYAD0 bit is driven high or low to give each PHY a unique address. This address is latched into

an internal register at the end of a hardware reset (default = 0b). In a multi-PHY application (such as

a repeater), the controller is able to manage each PHY via the unique address. Each PHY checks

each management data frame for a matching address in the relevant bits. When a match is recognized,

the PHY responds to that particular frame. The PHY address is also used to seed the scrambler. In a

multi-PHY application, this ensures that the scramblers are out of synchronization and disperses the

electromagnetic radiation across the frequency spectrum.

The device’s SMI address may be configured using hardware configuration to either the value 0 or 1.

The user can configure the PHY address using Software Configuration if an address greater than 1 is

required. The PHY address can be written (after SMI communication at some address is established)

using the PHYAD bits of the Special Modes Register. The PHYAD0 hardware configuration strap is

multiplexed with the RXER pin.

这段话在解释 LAN8720A 物理层芯片 中 PHY 地址(PHY Address) 的配置方法,主要涉及 PHY 地址的硬件和软件配置、在多 PHY 应用中的管理机制以及地址配置对数据传输的影响。让我们逐步解释这段话。

-

PHY 地址配置:

-

PHY 地址 是每个物理层芯片(PHY)在网络中用于唯一标识的地址。每个 PHY 都有一个唯一的地址,以便 控制器 可以区分并独立管理每个 PHY。

-

PHYAD0 是 PHY 地址配置 中的一个引脚(或者说信号),用于设置 PHY 地址。通过将 PHYAD0 引脚拉高或拉低,可以为每个 PHY 设置一个唯一的地址。例如,当 PHYAD0 为 低电平(0) 时,PHY 地址就是 0;当 PHYAD0 为 高电平(1) 时,PHY 地址就是 1。

-

-

地址配置时机:

- 在硬件复位结束时,PHY 地址 会被锁存到内部寄存器中,并且其默认值为 0b(即地址为 0)。这意味着,当设备启动并完成硬件复位时,PHY 地址的值会被初始化并存储为 0。

-

多 PHY 应用:

- 在一些应用中,可能有多个 PHY 芯片工作在同一个系统中(例如一个 中继器(repeater))。在这种情况下,PHY 地址 用来唯一标识每个 PHY。每个 PHY 会检查通过 管理数据帧(即管理协议数据包)中传输的地址,并根据地址匹配来决定是否响应该帧。

- 如果管理帧的地址与当前 PHY 的地址匹配,PHY 才会处理这个管理帧,否则就忽略它。

-

地址配置的作用:

- PHY 地址 还用于 初始化数据混乱器(scrambler)。数据混乱器是用来处理数据流,以减少电磁干扰(EMI)。在 多 PHY 系统 中,通过确保每个 PHY 地址不同,可以使得所有 PHY 的数据混乱器的工作状态不同,这有助于分散电磁辐射,避免多个 PHY 同步工作时产生强烈的干扰。

-

SMI 地址配置:

- SMI(Serial Management Interface) 是一个用于 PHY 芯片的管理接口,通过它可以进行寄存器访问和控制。该段话提到,PHY 地址 的配置有两个选择:

- 可以通过硬件配置将 SMI 地址 设置为 0 或 1。

- 如果需要更大的地址(即地址大于 1),则可以通过 软件配置 来设置地址。通过软件配置时,用户需要在建立 SMI 通信 后,使用 Special Modes Register(特殊模式寄存器) 中的 PHYAD 位来写入地址。

- SMI(Serial Management Interface) 是一个用于 PHY 芯片的管理接口,通过它可以进行寄存器访问和控制。该段话提到,PHY 地址 的配置有两个选择:

-

PHYAD0 与 RXER 引脚的多路复用:

- PHYAD0 引脚与 RXER 引脚是多路复用的,即它们在同一个物理引脚上,通过选择不同的功能来实现不同的功能。具体来说,在 PHY 地址配置 时,PHYAD0 用于设置 PHY 地址;而在 RX 错误检测(RXER) 时,该引脚用于指示接收错误。

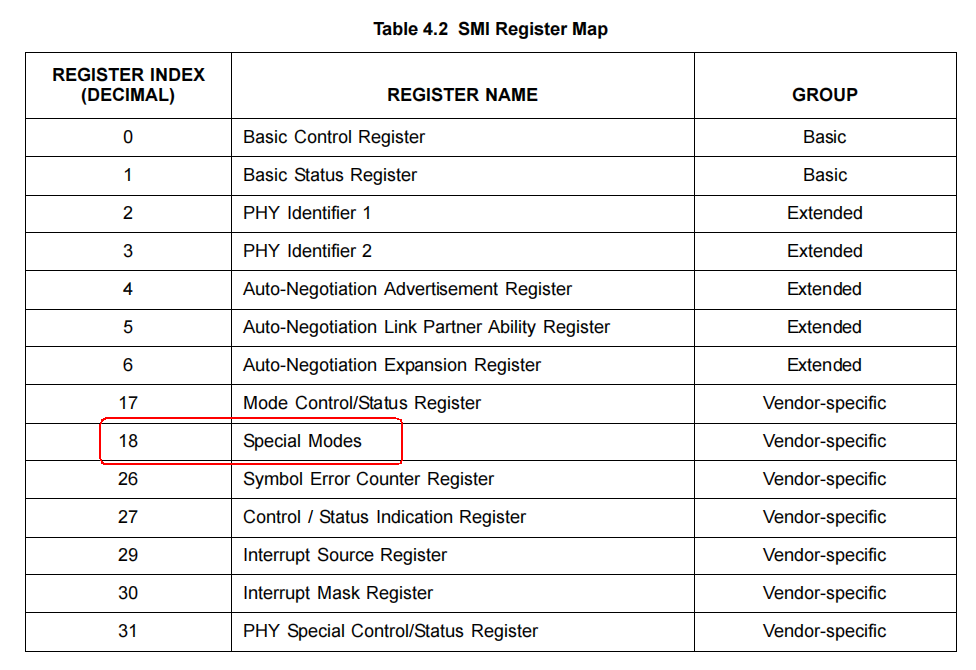

由此可见,我们需要去看Special Modes Register的介绍。

可见,索引值为18的寄存器的第0位到第4位用于配置其PHY地址,当然是通过由引脚MDIO 和引脚MDC构成的“SMI(Serial Management Interface)”接口来配置的。

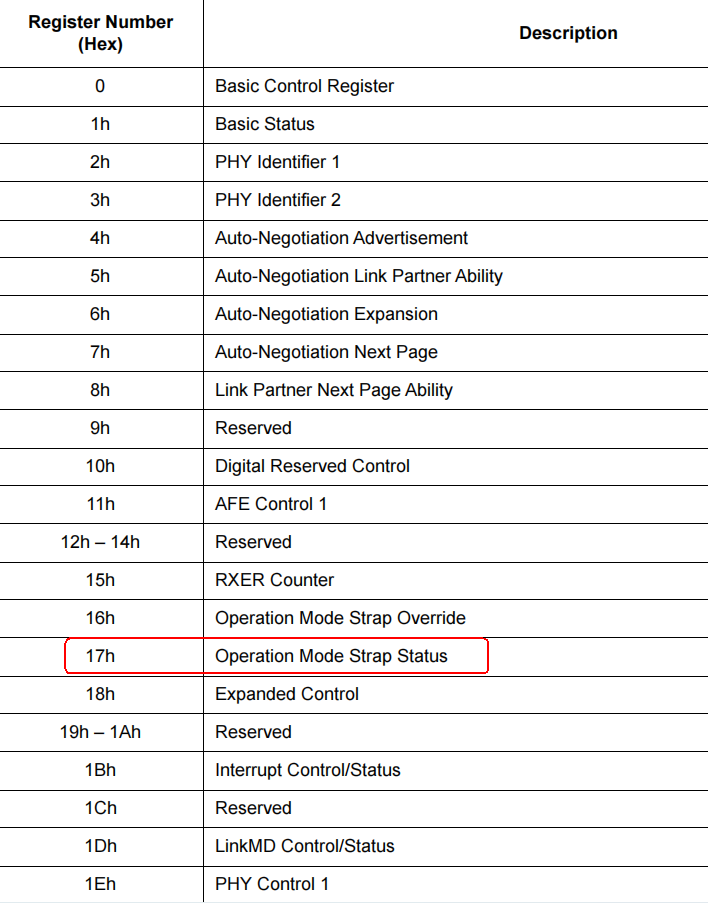

我们再去看下公板中的物理层芯片LAN8720A是通过哪个寄存器来配置PHY地址的,其Data sheet中的相关资料如下:

注意:如果一个寄存器中的名字中带有单词Strap,那么就表明这个寄存器的值来自外部引脚的电平状态,而不是由SMI 等接口去配置的。详情见 https://blog.youkuaiyun.com/wenhao_ir/article/details/145712197

我在公板的物理层芯片KSZ8081RNB的Data sheet中搜索关键词PHY Address,发现没有一个地方提到了可以用由引脚MDIO 和引脚MDC构成的“SMI(Serial Management Interface)”接口来进行设置,再结合博文https://blog.youkuaiyun.com/wenhao_ir/article/details/145712197 看,可以大概率确定物理层芯片KSZ8081RNB的PHY地址是由RXD3/PHYAD0、RXD2/PHYAD1、RXD1/PHYAD2这几个引脚在在复位信号解除有效时的电平值来决定的。

综上两个物理层芯片的PHY地址在0和1的配置是一样的,但是超过1之后就不一样了,公板中的物理层芯片由几个引脚来决定,而百问网的开发板则需要去配置寄存器Special Modes Register的第0到4位。

对于百问网的开发板,如果是一个正常的设计者,那么它在写相应的程序时肯定会把板子上的两个物理层芯片的PHY地址设为0和1,而不会超过1,超过1就是自己在给自己找麻烦。

总结(该怎么修改u-boot中与PHY地址相关的代码)

对于公板而言,前面已经在博文 https://blog.youkuaiyun.com/wenhao_ir/article/details/145663029 中分析过了,以太网1对应的物理层芯片的PHY地址为2,以太网2对应的物理层芯片的PHY地址为1,现在为了把这个u-boot移植到我们百问网的开发板上,我们需要做如下修改:

把以太网1对应的物理层芯片的PHY地址设置为0,把以太网2对应的物理层芯片的PHY地址设置为1。

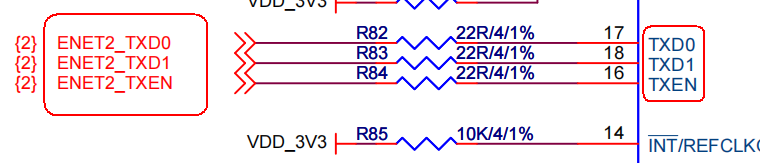

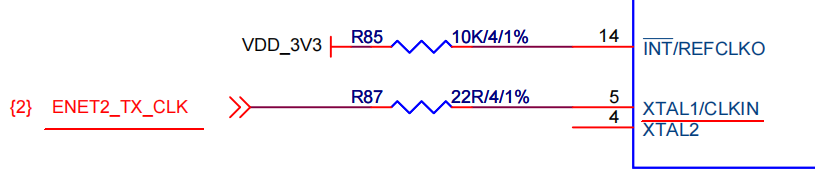

引脚TXD0、TXD1、TXEN【与公板一样】

这3个引脚不用说,肯定和公板的连接情况是一样的,相关原理图如下:

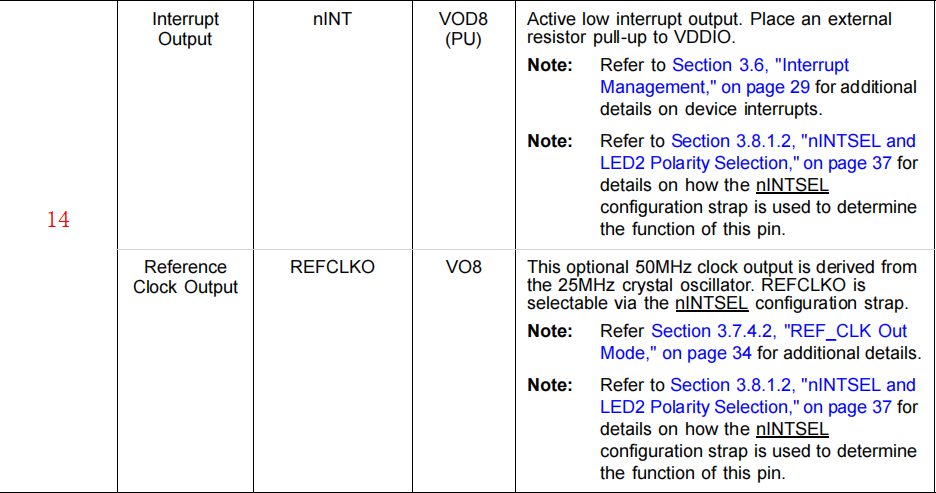

引脚INT/REFCLKO【INT与公板不一样但相关程序是通用的】

这个引脚在Data sheet中的说明如下:

相关的说明文字提取如下:

INT:Active low interrupt output. Place an external resistor pull-up to VDDIO.

REFCLKO:This optional 50MHz clock output is derived from the 25MHz crystal oscillator. REFCLKO is selectable via the nINTSEL configuration strap.

nINTSEL:

This configuration strap selects the mode of the

nINT/REFCLKO pin.

①When nINTSEL is floated or pulled to VDD2A,

nINT is selected for operation on the

nINT/REFCLKO pin (default).

②When nINTSEL is pulled low to VSS,

REFCLKO is selected for operation on the

nINT/REFCLKO pin.

这段说明详细描述了 LAN8720A 物理层芯片的引脚 INT/REFCLKO 以及该引脚的模式选择机制。引脚的功能可以在 中断输出(INT) 和 参考时钟输出(REFCLKO) 之间切换,具体模式取决于引脚 nINTSEL 的配置。下面是对每一部分的详细解释:

-

引脚 INT/REFCLKO

- 该引脚具有两种功能,分别是:

- INT(中断输出):当芯片需要向外部系统发出中断信号时,该引脚会以低电平方式输出中断信号。INT 信号为 低电平有效(Active low),即当发生中断时,该引脚输出低电平。

- REFCLKO(参考时钟输出):这是一个可选的 50 MHz 时钟输出,该时钟源来自于 25 MHz 晶体振荡器。该功能可以用于提供给其他模块或者设备作为时钟源。

- 该引脚具有两种功能,分别是:

-

引脚 nINTSEL

- nINTSEL 是一个配置引脚,用于选择 INT/REFCLKO 引脚的工作模式。其配置方式如下:

- nINTSEL 引脚浮空或拉高至 VDD2A:如果 nINTSEL 引脚浮空(即没有连接,或未被拉低)或者拉高至 VDD2A 电压,那么在复位信号解除有效时,INT 功能会被启用,INT/REFCLKO 引脚将作为中断输出(INT)来工作。这是 默认模式。

- nINTSEL 引脚拉低至 VSS:如果 nINTSEL 引脚被拉低至地(VSS),那么在复位信号解除有效时,则 REFCLKO 功能会被启用,INT/REFCLKO 引脚将作为 50 MHz 时钟输出(REFCLKO) 工作。

- nINTSEL 是一个配置引脚,用于选择 INT/REFCLKO 引脚的工作模式。其配置方式如下:

-

关于 INT 和 REFCLKO 的详细功能:

- INT(中断输出):当 LAN8720A 物理层芯片检测到某些特定事件或错误时,它会通过 INT 引脚 发出 低电平中断信号,通知外部系统。此信号通常需要外部上拉电阻将其拉高到 VDDIO 电压。

- REFCLKO(参考时钟输出):此功能提供 50 MHz 时钟,其源自芯片内部的 25 MHz 晶体振荡器。当 nINTSEL 引脚拉低至 VSS 时,INT/REFCLKO 引脚会作为时钟输出。这通常用于为其他设备提供参考时钟。

-

配置方式总结:

- nINTSEL 引脚控制 INT/REFCLKO 引脚的功能选择,具体取决于 nINTSEL 的电平:

- 默认状态:如果 nINTSEL 引脚浮空或拉高至 VDD2A,则 INT 模式(中断输出)被启用,INT/REFCLKO 引脚作为中断信号输出。

- REFCLKO 模式:如果 nINTSEL 引脚被拉低至 VSS,则 REFCLKO(50 MHz 时钟输出)功能被启用,INT/REFCLKO 引脚作为时钟输出。

- nINTSEL 引脚控制 INT/REFCLKO 引脚的功能选择,具体取决于 nINTSEL 的电平:

总结:

- INT/REFCLKO 引脚在 LAN8720A 中具有 两种功能,分别为 中断输出(INT) 和 50 MHz 时钟输出(REFCLKO),而选择哪种模式是由 nINTSEL 引脚的状态决定的。

- 通过配置 nINTSEL 引脚,可以选择:

- INT 模式(默认):当 nINTSEL 引脚浮空或拉高至 VDD2A,INT/REFCLKO 引脚作为中断输出。

- REFCLKO 模式:当 nINTSEL 引脚拉低至 VSS,INT/REFCLKO 引脚作为 50 MHz 时钟输出。

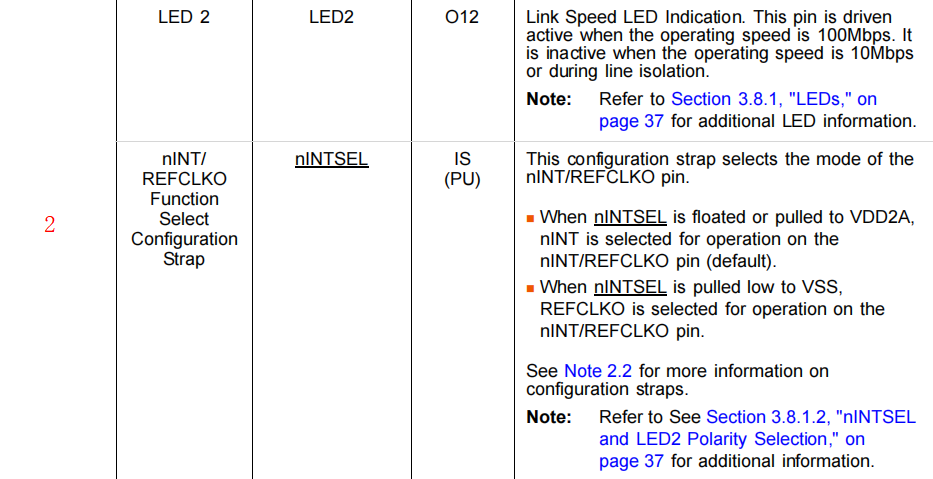

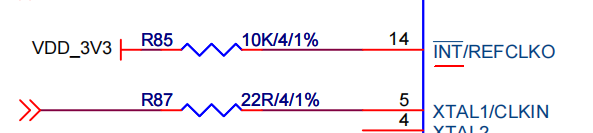

相关的电路原理图如下:

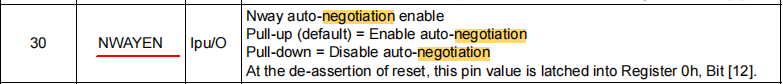

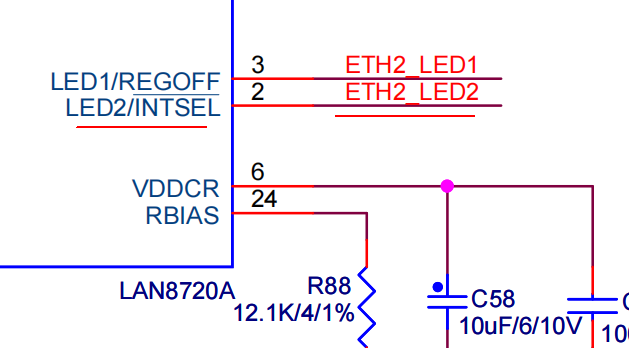

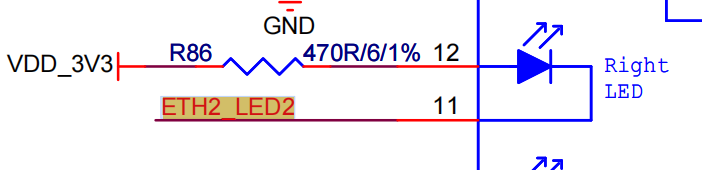

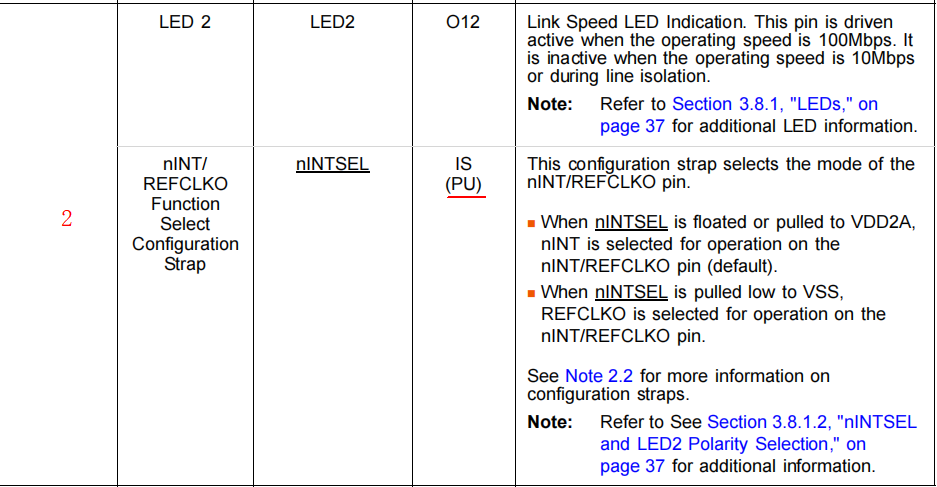

在复位信号解除有效时,引脚LED2/INTSEL由于内部有上拉电阻,相关Data sheet如下:

所以Right LED的两端的电平值相当于都是高电平,所以Right LED不会被导通,所以Right LED相当于开路状态,所以在复位信号解除有效时,LED2/INTSEL的电平值为高电平,所以引脚INT/REFCLKO的功能被选择为INT状态,即作为中断输出引脚,如果作为中断输出引脚,需要外部上拉电阻将其拉高到高电平状态。

但是,从原理图中可以看出,虽然将引脚INT/REFCLKO选择为了中断输出,但百问网的开发板实际上没有用这个中断输出信号。我看了以太网1的物理层芯片的连接图,也是一样的没有用,如下图所示:

虽然公板用了这个信号,并连接到了IMX6ULL的处理器的引脚上SNVS_TAMPER5,但是程序还是显然是通用的呀,在百问网的板子中,只是程序收不到物理层芯片的异常中断信号,正常工作时,这个异常中断信号是不会产生的。

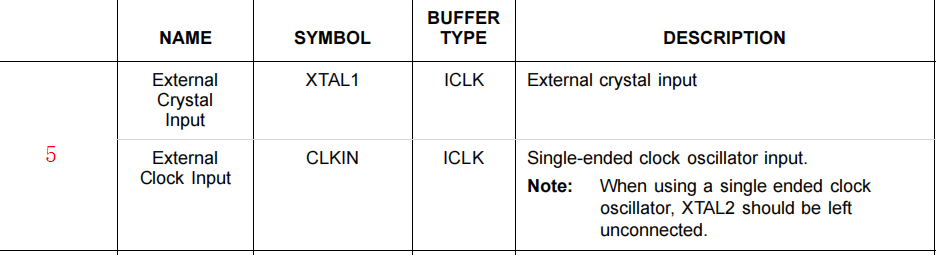

引脚XTAL1/CLKIN 【与公板一样】

这个引脚不用说,肯定和公板的连接情况是一样的,相关原理图如下:

对比博文 https://blog.youkuaiyun.com/wenhao_ir/article/details/145663029 果然是一样的,这里是使用处理器的MAC的引脚ENET2_TX_CLK提供时钟信号。注意,MAC的引脚ENET2_TX_CLK并不只是提供发送数据时的时钟,也提供接收数据时的时钟哦,相关情况请访问博文 https://blog.youkuaiyun.com/wenhao_ir/article/details/145663029 并搜索关键词“佐证我们的想法”。

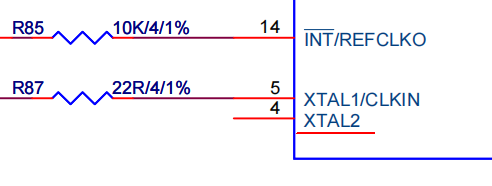

引脚XTAL2【与公板一样】

如果用外部晶体振荡器作为时钟源,那么这个引脚作为外部晶体振荡器的反馈引脚,不要看到Data sheet的描述中有个output,就以为是时钟输出哈,不是的哈。

这个引脚与公板一样,都没有使用,相关原理图如下:

以太网1的物理层芯片各引脚连接情况分析

只有1个地方与上面已经分析了的以太网2不一样,那就是PHY地址的设置,我上面已经分析出了:以太网1的物理层芯片PHY地址设置为了0,以太网2对应的物理层芯片的PHY地址设置为了1。

所以对“以太网1的物理层芯片各引脚连接情况分析”略。

总结:与公板不一样而导致要改代码地方

根据上面的分析结果,我们可以看出,实际上就两个地方由于不一样而导致要去修改对应的程序,在这里我要移植的是u-boot,所以去修改u-boot的代码。

具体的两个不同的地方是:

①复位信号来源不一样:详情请在本篇博文中搜索:“这个复位引脚是直接连到处理器的”。

②两个以太网对应的物理层芯片的PHY地址不一样:详情请在本篇博文中搜索:“对于公板而言,前面已经在博文“。

百问网IMX6ULL开发板以太网PHY芯片引脚分析

百问网IMX6ULL开发板以太网PHY芯片引脚分析

6475

6475

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?