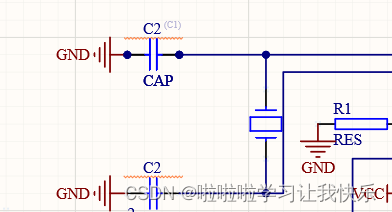

一、位号的重复

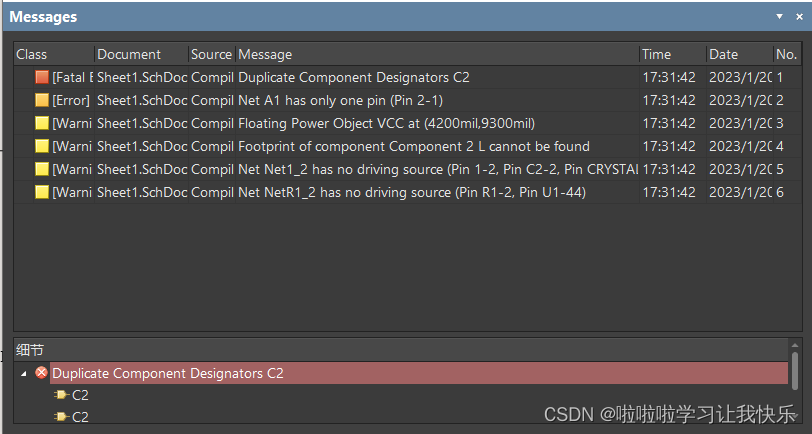

在一张原理图上,每个元件分别对应一个位号,如果同一个位号对应两个甚至多个元件,就会造成原理图混乱,因此我们要设置明显的报错提示。假如我们同时设置两个C2,就会有红色波浪线提醒我们错误。

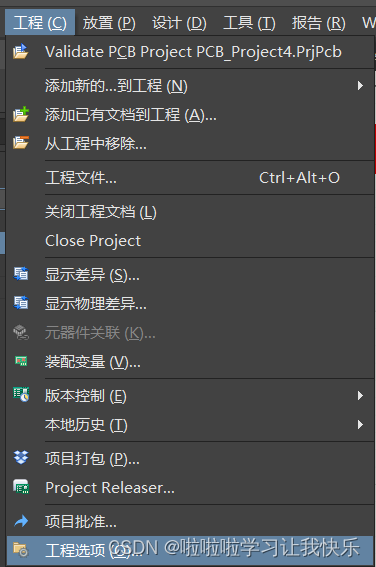

点击【工程】-》【工程选项】

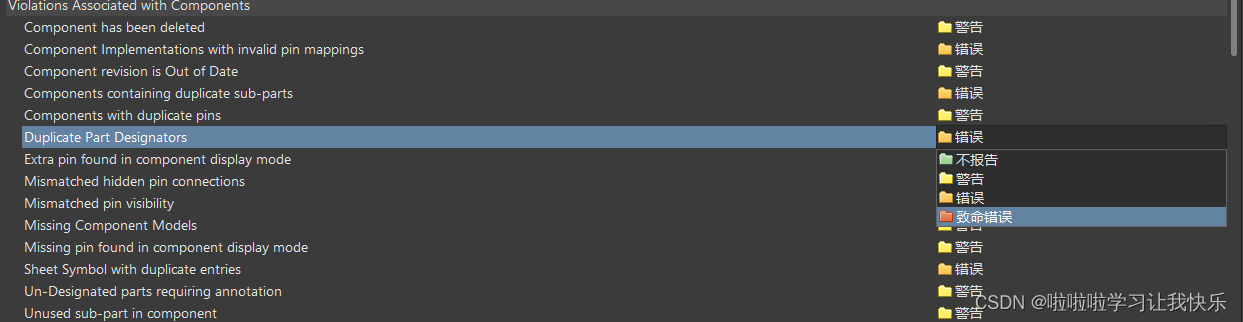

将【Violations Associated with Components】下的【Duplicate Part Designators】选择【致命错误】,这样发生错误时更明显。

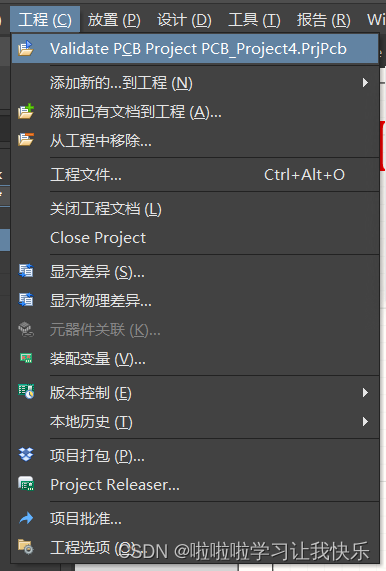

点击【工程】-》【Validate PCB Project…】编译验证

然后就会弹出【Message】框来提示错误

二、网络是否悬浮

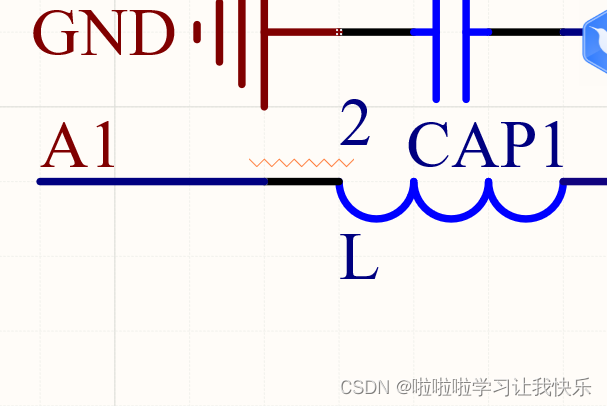

网络悬浮就是我们添加的网络标签或者电源网络没有连接到导线上,网络悬浮也分为普通网络悬浮和电源网络悬浮,如图:

1是电源网络悬浮,2是普通网络悬浮

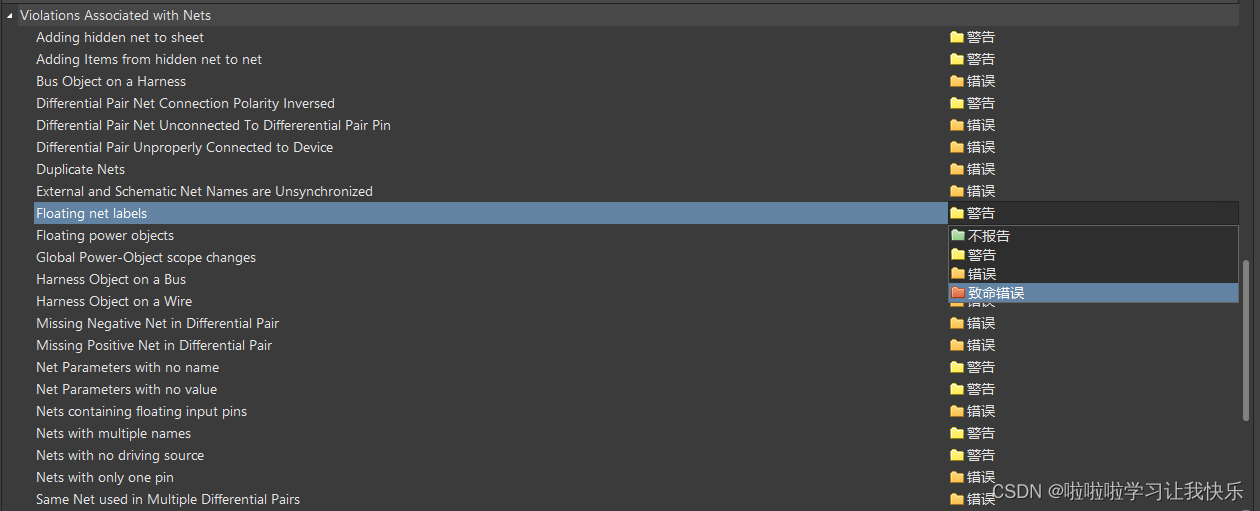

将【Violations Associated with Nets】下的【Floating net labels】选择【致命错误】,同样编译的时候也会报警。

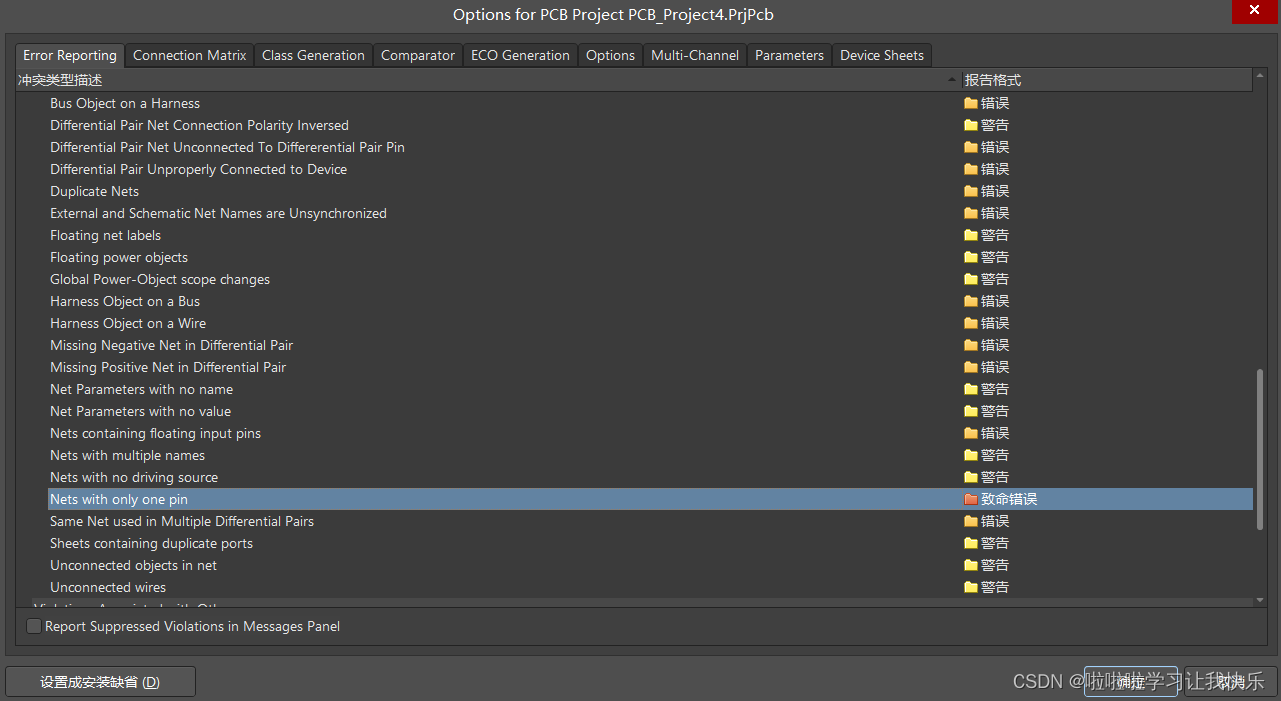

三、是否有单端网络

当使用网络标签连接两个导线时,可以通过【ALT+左击右键】来寻找同样标号的网络,而当我们所添加的网络标签只有一个时,没有对应的网络相连,就称为单端网络,如图

我们同样也要将其设置为【致命错误】

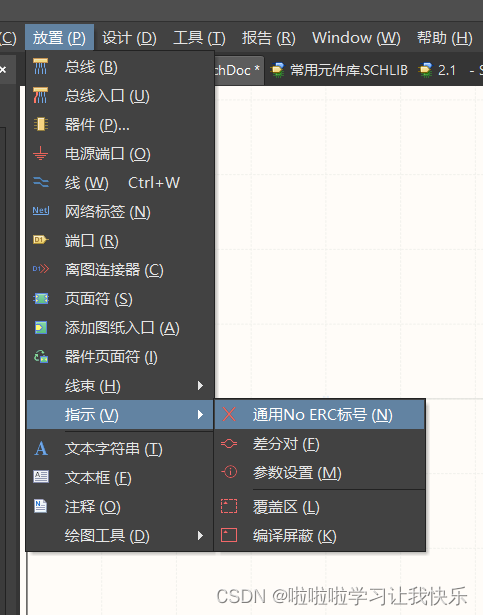

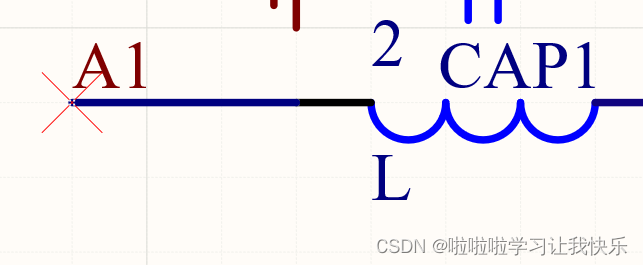

但假如原理图就是单端网络,可以检查后忽略错误,并且在【放置】-》【指示】-》【通用No ERC标号】

表示这里是单端网络

文章讲述了在原理图设计中需要注意的三个关键问题:位号不能重复,避免网络悬浮,以及检查单端网络。通过设置错误提示为致命错误,可以在编译时及时发现并解决这些问题。对于单端网络,如果是故意设计的,则可以使用通用NoERC标号表明。

文章讲述了在原理图设计中需要注意的三个关键问题:位号不能重复,避免网络悬浮,以及检查单端网络。通过设置错误提示为致命错误,可以在编译时及时发现并解决这些问题。对于单端网络,如果是故意设计的,则可以使用通用NoERC标号表明。

1918

1918

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?