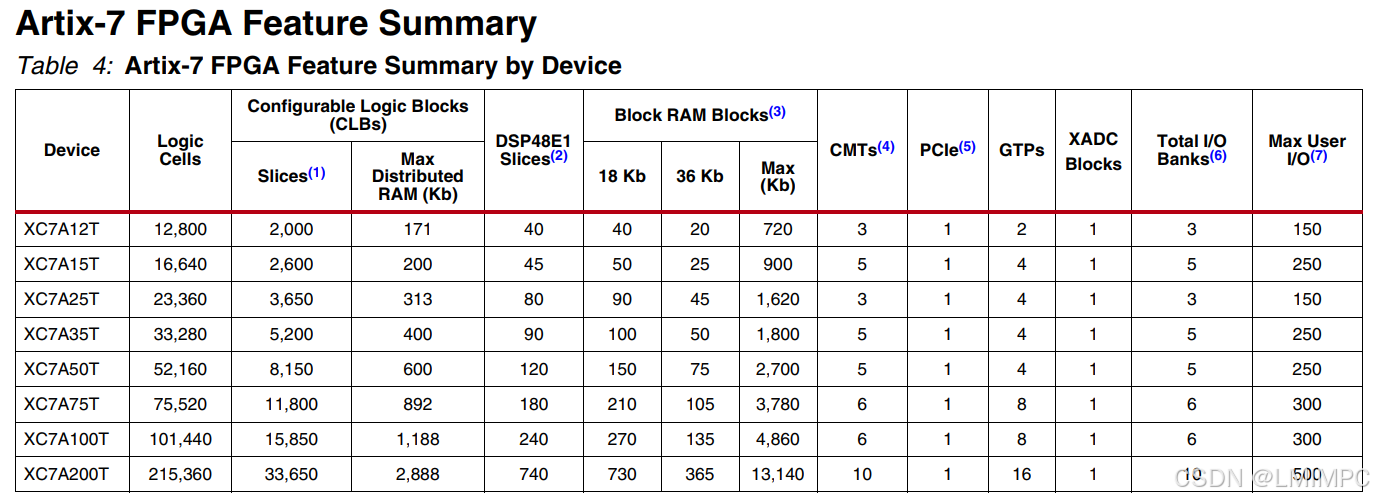

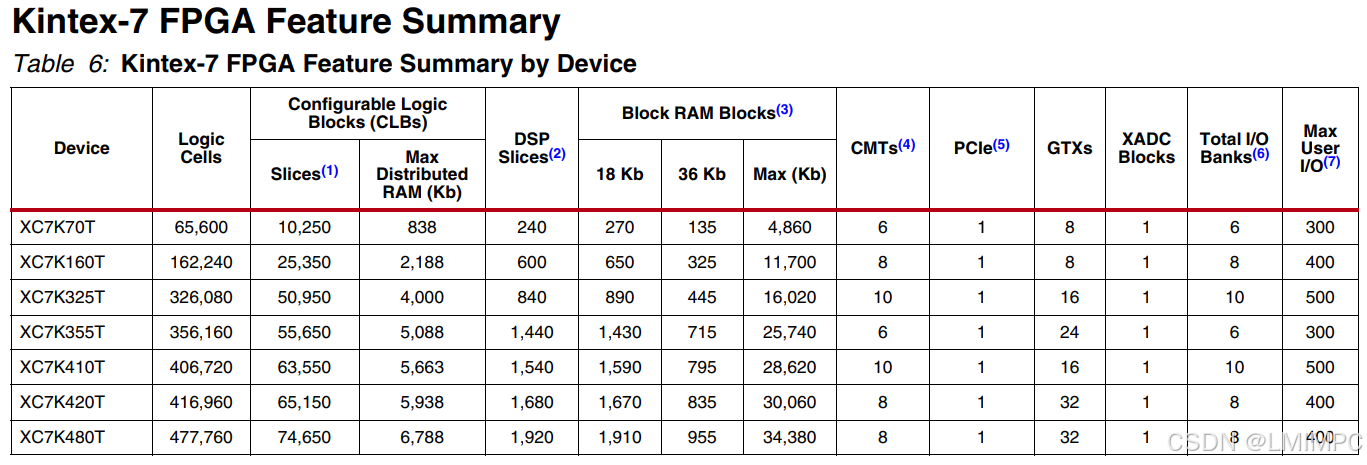

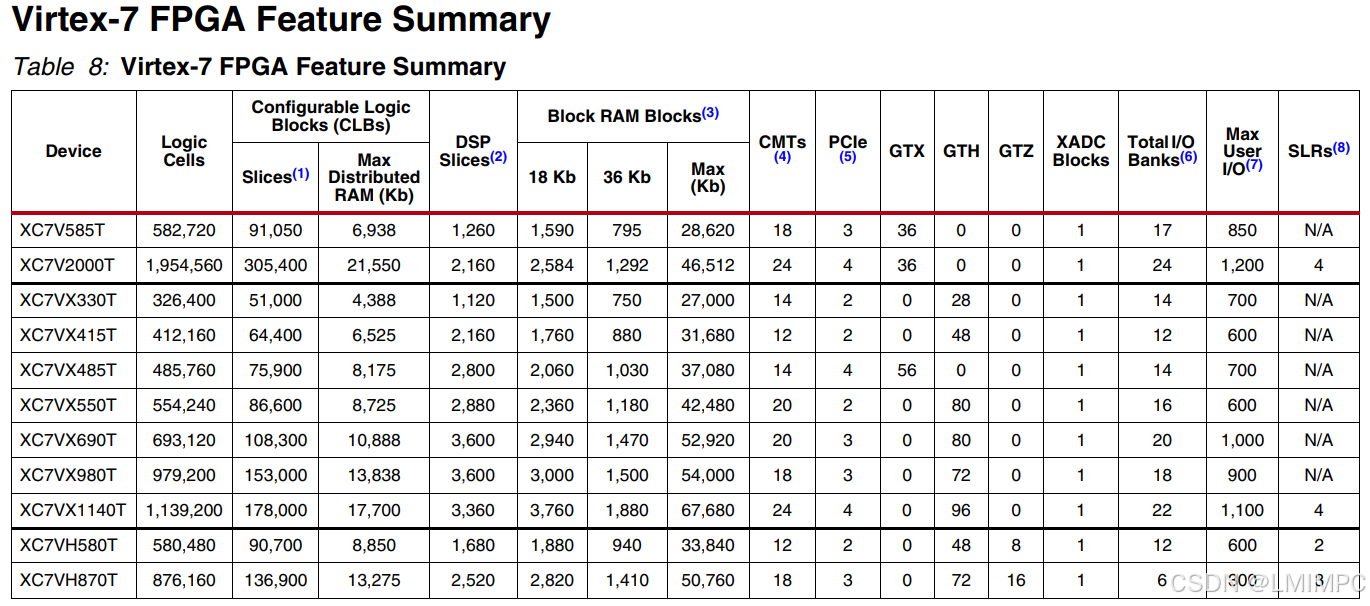

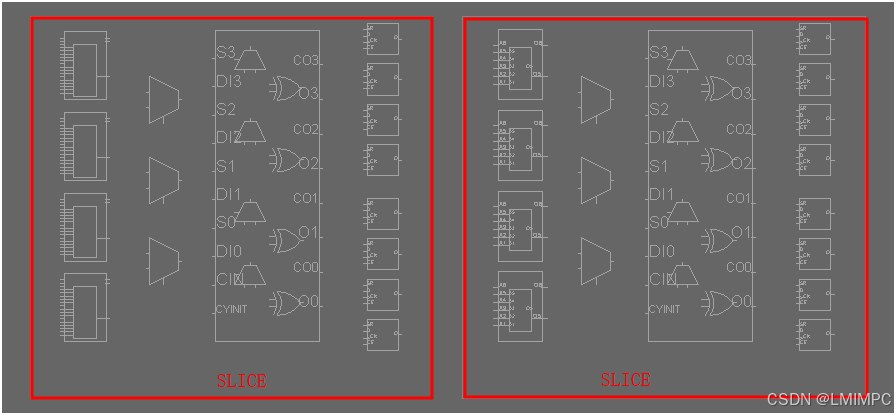

以Xilinx 7系列为例,Logic Cell(逻辑单元)是FPGA芯片资源大小的度量单位,与LUT(Look Up Table,查找表)的关系是,Logic Cell的数量等于LUT的数量*1.6,参考图1和图5对应型号计算,没有专门的电路单元与之对应,Slice和CLB(Configurable Logic Block,可配置逻辑块)有专门电路单元与之对应;1个Slice包含4个LUT,8个FF(Flip Flop,触发器),3个MUX(Multiplexer,多路复用器)和1个CARRY4(超前进位链),与Logic Cell的关系是,Slice的数量等于6.4*Logic Cell的数量,通过手册计算可知,如图1~3;1个CLB包含2个Slice,如图4。

图1 A7资源统计

图2 K7资源统计

图2 K7资源统计

图3 V7资源统计

图4 CLB和Slice 关系

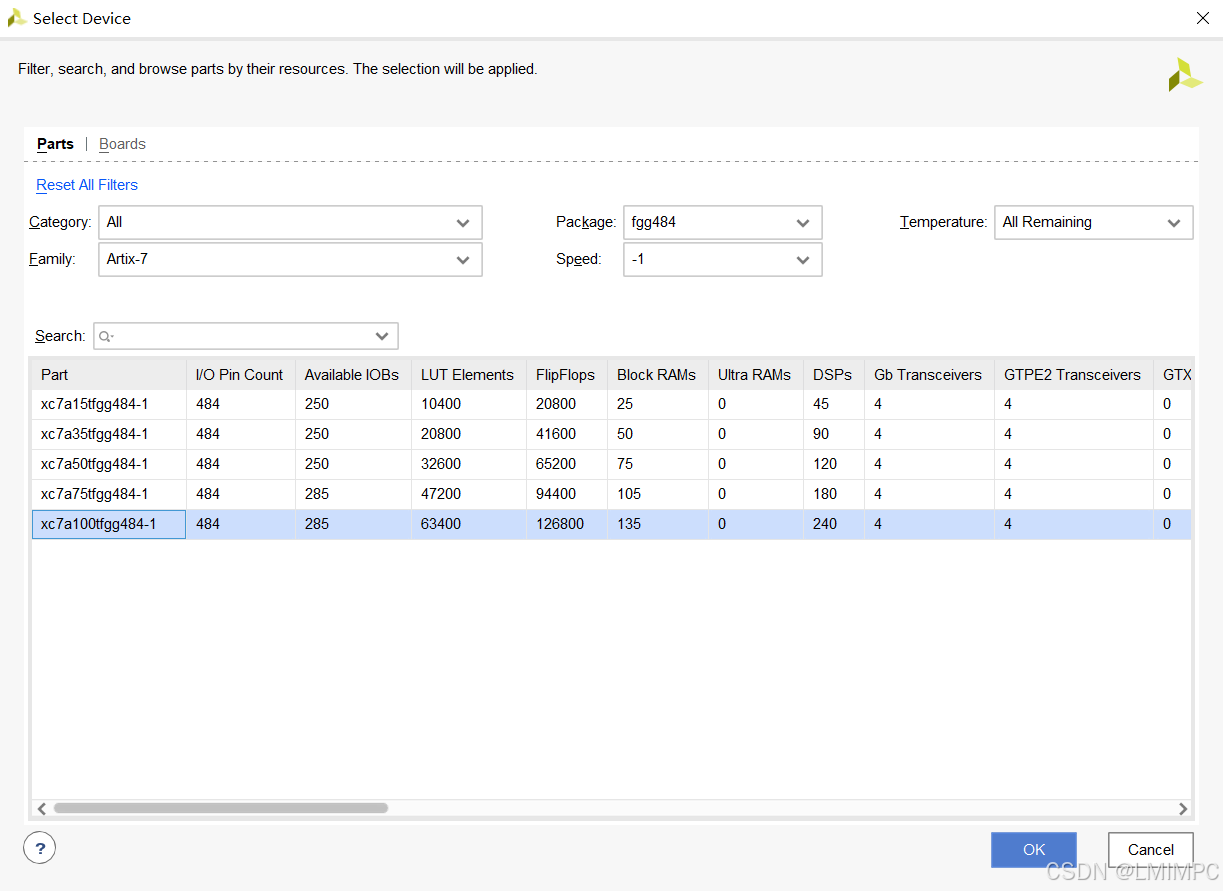

图5 芯片选择

2964

2964

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?