verilog的学习过程目录

1.verilog文件编写格式与modelsim的环境配置方法

全加器

全加器,是用门电路实现两个半加器实现二进制数相加并求出和的组合线路,称为一位全加器。一位全加器可以处理低位进位,并输出本位加法进位,所以我们需要构建半加器,再通过元件例化进行连线,在进行仿真。

一、元件与仿真代码编写

半加器的代码

module adder_h( //verilog的module的格式为module 器件名(端口定义);endmodule

input wire a, //创建输入线a

input wire b, //创建输入线b

output wire co, //创建输出线co

output wire so //创建输出线so !注意这里没有逗号!

);

assign co = a & b; //对a和b进行逻辑与,所得到的值给到co

assign so = a ^ b; //对a和b进行逻辑异或,所得到的值给到so

endmodule

全加器元件代码

module adder_f(

input wire A , //创建输入线A

input wire B , //创建输入线B

input wire CIN , //创建输出线CIN

output wire COUT, //创建输出线COUT

output wire SUM //创建输出线SUM

);

wire co1,co2,so1; //定义导线型变量co1,co2,so1

assign COUT = co1 | co2;//assign用于对wire类型变量赋值

//对元件进行例化

adder_h adder_h_inst1(

.a (A ), //将adder_h中的a 对应到例化器件块端口A

.b (B ), //将adder_h中的B 对应到例化器件块端口B

.co (co1), //将adder_h中的co对应到例化器件块端口co1

.so (so1) //将adder_h中的so对应到例化器件块端口so1

);

adder_h adder_h_inst2(

.a (so1), //将adder_h中的a 对应到例化器件块端口so1

.b (CIN), //将adder_h中的B 对应到例化器件块端口CIN

.co (co2), //将adder_h中的co对应到例化器件块端口co2

.so (SUM) //将adder_h中的so对应到例化器件块端口SUM

);

endmodule

modulesim仿真代码

`timescale 1ns / 1ns //定义仿真时间 格式 `timescale 仿真时间单位/时间精度

module tb_top(); //定义module tb_top

reg A,B,CIN; //定义寄存器型变量A,B,CIN

wire COUT,SUM; //定义线型变量COUT,SUM;

initial begin //定义一个初始化块

$display("A\tB\tCIN\tCOUT\tSUM\t"); //显示A,B,CIN,COUT中间用8个字符进行分割

repeat(50)begin //重复50次

A = {$random} % 2; //对随机数与2取模,得到的值不为0,就为1,值给到A

B = {$random} % 2; //对随机数与2取模,得到的值不为0,就为1,值给到B

CIN = {$random} % 2; //对随机数与2取模,得到的值不为0,就为1,值给到CIN

#20; //延迟20ns

$display("%b\t%b\t%b\t%b\t%b\t",A,B,CIN,COUT,SUM); //显示A,B,CIN,COUT,SUM的数值

#80; //延迟20ns

end

#1000; //延迟1000ns

$stop; //停止

end

adder_f adder_f_inst(

.A (A ), //将adder_h中的A对应到例化器件块端口A

.B (B ), //将adder_h中的B 对应到例化器件块端口B

.CIN (CIN), //将adder_h中的CIN对应到例化器件块端口CIN

.COUT (COUT), //将adder_h中的COUT对应到例化器件块端口COUT

.SUM (SUM ) //将adder_h中的SUM对应到例化器件块端口SUM

);

endmodule

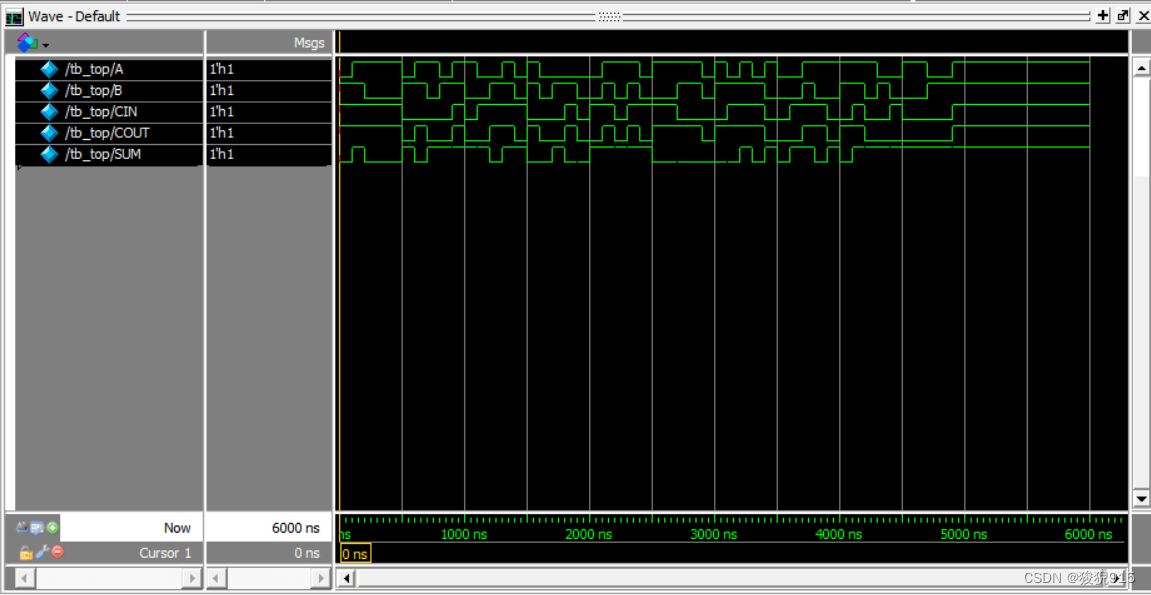

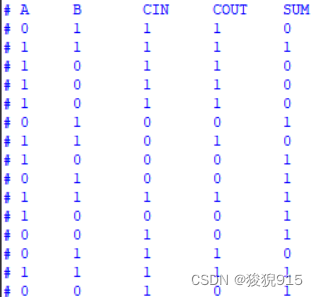

二、仿真效果

对于modelsim的使用方法在前期文章已经讲解,这里不做介绍。

总结

本篇文章主要讲解了全加器的代码部分。

5338

5338

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?