提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

文章目录

前言

本篇内容主要总结UVM实战的第5章内容

一、phase机制

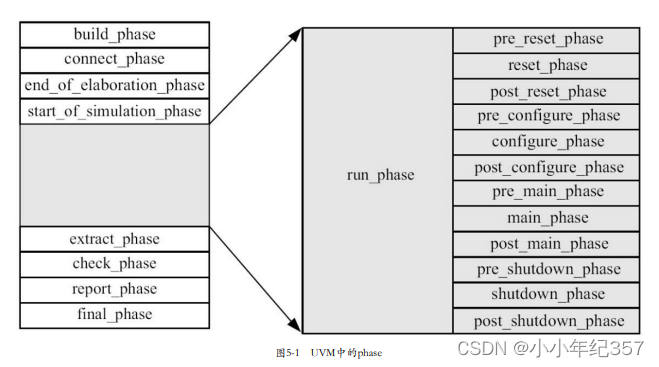

UVM由phase来管理验证平台的运行,这些phase统一以xxxx_phase来命名,且都有一个类型为uvm_phase、名字为phase的参数。

1. task phase与function phase

UVM中的phase按照是否消耗仿真时间,可以分成两大类,一类是function phase, 如build_phase、connect_phase等,这些phase通过函数来实现;另一类是task phase,如run_phase等,消耗仿真时间,通过任务来实现。

如下图所示,灰色背景是task phase,其他为function phase

上述phase使用频率最高的是build_phase、connect_phase和main_phase。

2. phase的执行顺序

- 按时间顺序执行:

上节展示的phase都会按图中的顺序自上而下自动执行,即build_phase->connect_phase->main_phase,这是时间的概念。

注意:

对于function phase来说,在同一时间只有一个phase在执行;

对于task phase来说,run_phase和pre_reset_phase等12个小phase并行运行,如下:

fork

begin

run_phase();

end

begin

pre_reset_phase();

...

main_phase();

...

post_shutdown_phase();

end

join

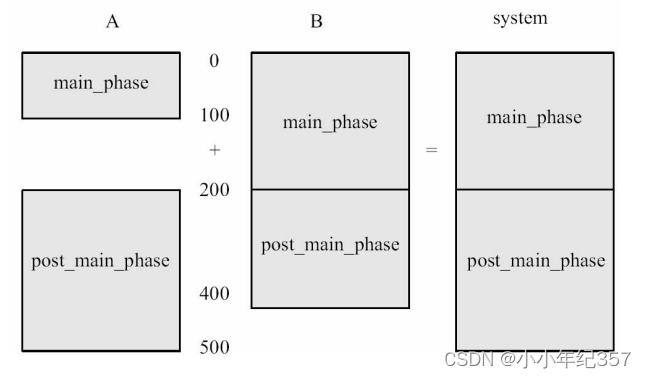

对于这12个小phase是按顺序执行的,同一phase在所有的component内必须全部执行完,才可以进入到下一个phase,效果如下图所示。

还有,run_phase和post_shutdown_phase必须全部执行完,才可以进入到下一个phase:extract_phase

- 按空间顺序执行:

考虑这样的事情,对于build_phase或者connec_phase,是先执行my_case里的build_phase或者connec_phase还是先执行env的呢?

对于build来说,是先从树根到树叶的过程,即my_case -> env -> agt -> drv

对于其他phase,均是先从树叶到树根的过程 ,即drv -> agt -> env -> my_case

注意:对于耗时的phase,并不是等到“下面”的phase(如driver的run_phase)执行完才执行“上面”的phase(如agent的run_phase),而是将这些run_phase通过fork…join_none的形式全部启动。

3. super.phase的内容

看UVM环境会发现,有时候出现super.xxxx_phase,有时候又不会出现。那哪些需要加上super,哪些又可以不加呢?

答案就是除了build_phase或者扩展自用户自定义的类,其他的phase完全可以不必加上super.xxxx_phase

- build_phase是因为设置了super.build_phase可以通过自动获取通过config_db::set设置的参数。

- 自定义的的类,比如base_test类,且在其某个phase,如connect_phase中定义了一些重要内容,那么在具体测试用例的connect_phase中就不应该省略super.connect_phase。

4. phase的跳转

在前面的表述中,各个phase都是顺序执行的,前一个phase执行完才执行后一个。实际上phase之间也可以互相跳来跳去。

举例从main_phase到reset_phase,验证平台检测到reset_n信号为低电平,则马上从main_phase跳转到reset_phase,代码如下:

task my_driver::reset_phase(uvm_phase phase);

phase.raise_objection(this)

本文详细介绍了UVM验证平台的phase机制,包括task phase与function phase的区别、执行顺序、跳转及超时退出。此外,还讲解了objection机制,包括raise_objection和drop_objection的使用、参数phase的必要性,以及set_drain_time的设置,旨在帮助理解UVM验证流程的控制与协调。

本文详细介绍了UVM验证平台的phase机制,包括task phase与function phase的区别、执行顺序、跳转及超时退出。此外,还讲解了objection机制,包括raise_objection和drop_objection的使用、参数phase的必要性,以及set_drain_time的设置,旨在帮助理解UVM验证流程的控制与协调。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

3582

3582

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?