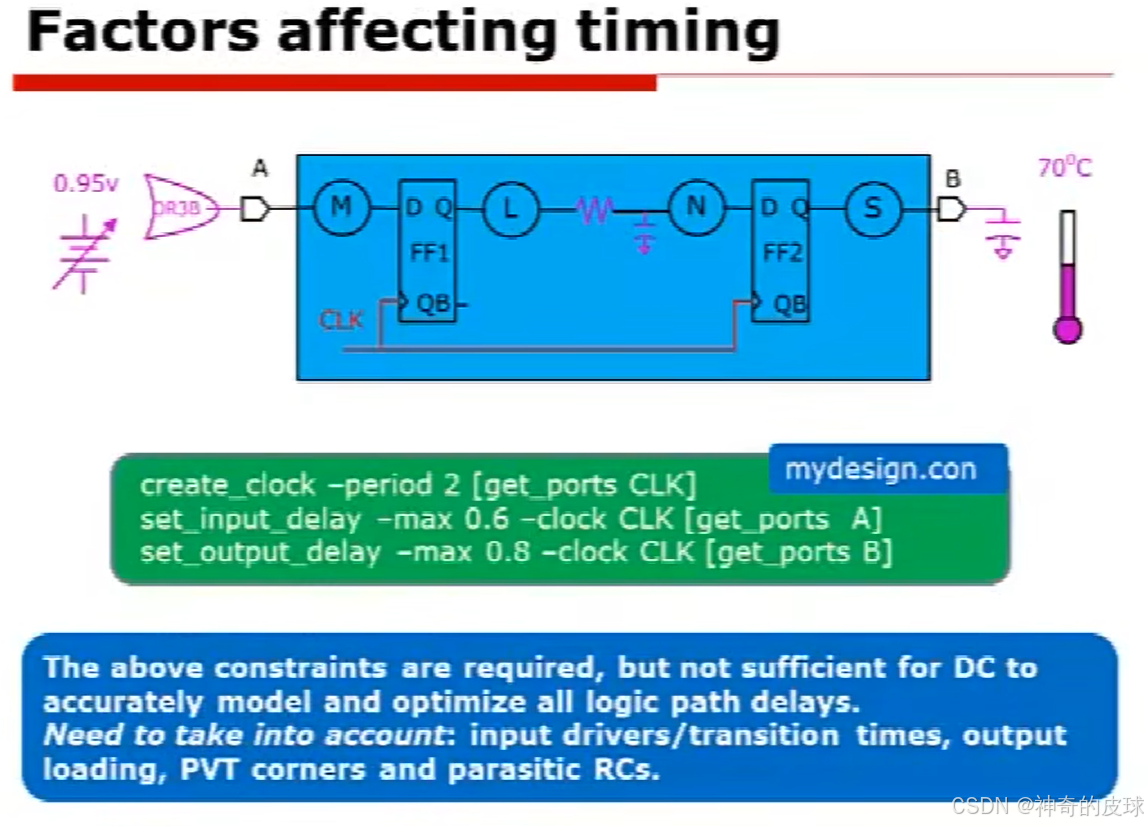

本节主要介绍环境约束,主要有以下几个方面

- Input drivers and transition times

- Capacitive output loads

- PVT operating conditions or ‘corners‘

- Interconnect parasitic RC

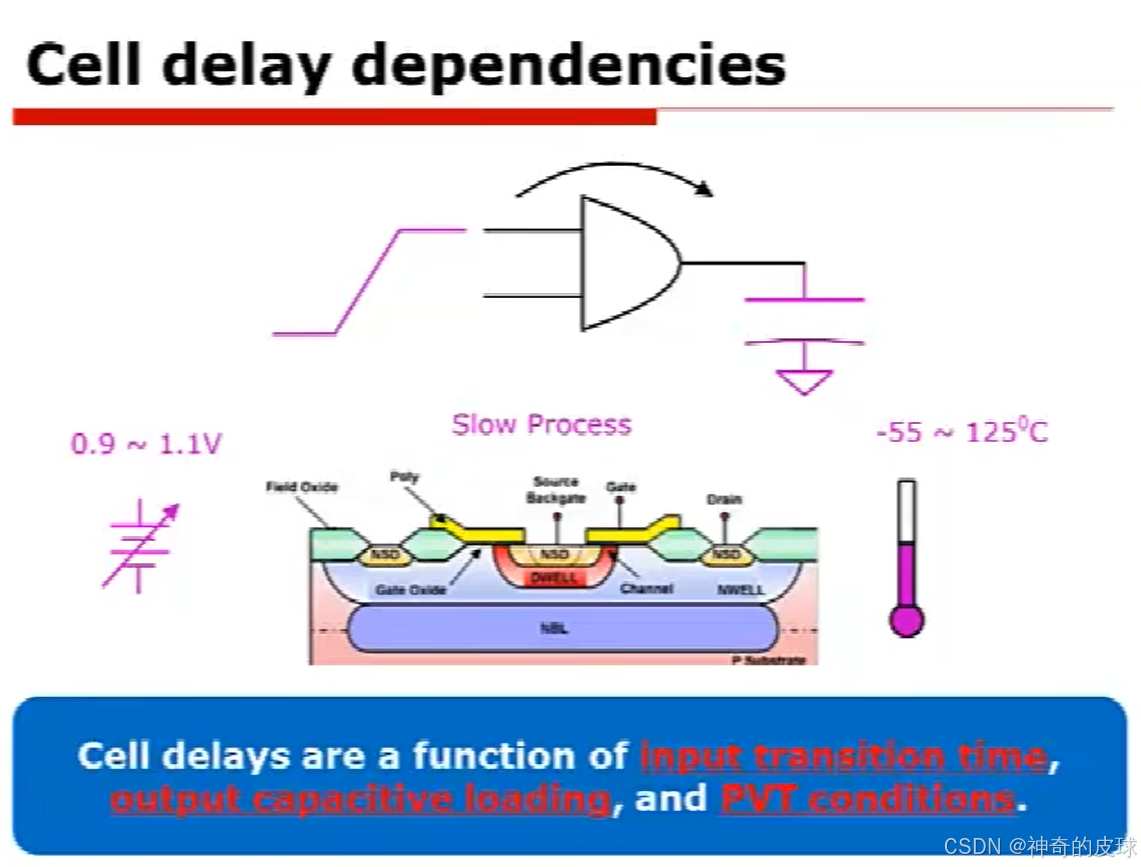

单元延迟(Cell Delay)的依赖因素

- 输入转换时间(Input Transition Time):输入信号的上升/下降时间直接影响单元的延迟。输入信号变化越慢,单元的延迟可能越大。

- 输出电容负载(Output Capacitive Loading):单元驱动的负载电容大小会影响信号传输延迟。较大的负载电容需要更多的驱动能力,从而增加延迟。

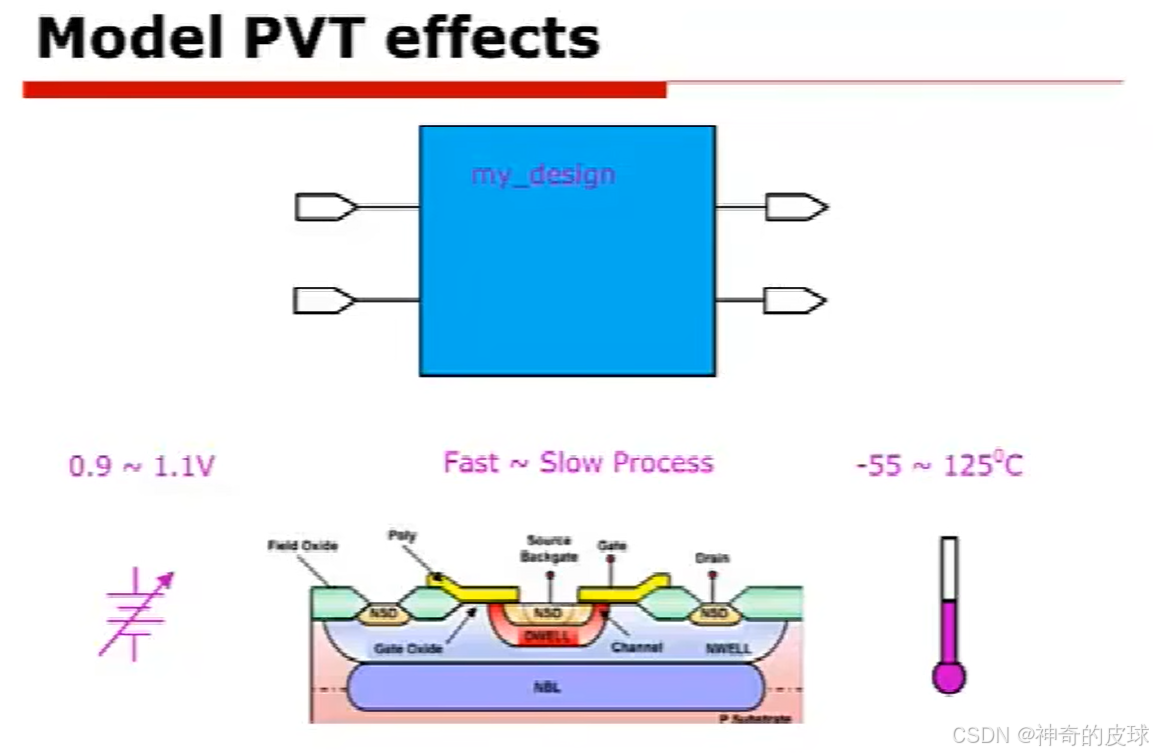

- PVT条件(PVT Conditions):

- 电源电压(Voltage):电源电压范围从0.9V到1.1V,电压越低,单元延迟可能越大(因为驱动能力下降)。

- 工艺变化(Process):慢速工艺(Slow Process)条件下,单元的性能可能下降,延迟增加。

- 温度(Temperature):温度范围从-55°C到125°C。高温通常会导致延迟增加,因为高温会降低晶体管的载流子迁移率。

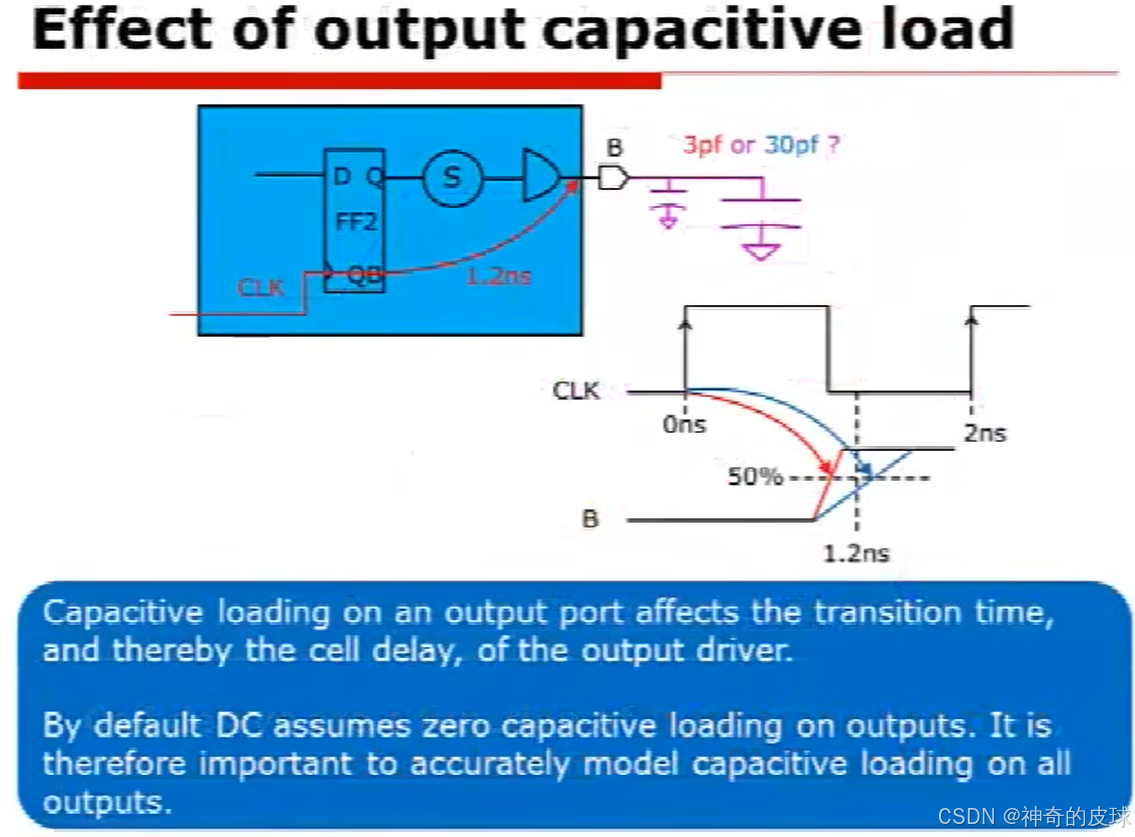

输出电容负载的影响

- 输出端口的电容负载会影响输出驱动器的过渡时间(transition time)以及单元延迟(cell delay)。较大的电容负载(如30pF)增加驱动器的负担,导致信号上升/下降时间更长,从而延迟增加。较小的电容负载(如3pF)驱动更快,信号上升/下降时间较短,延迟较小。

- DC默认情况下,认为输出端口上的电容负载为零(zero capacitive loading)。这种默认假设会导致延迟估算不准确,无法反映实际情况。在时序分析中,应准确地建模输出端口的电容负载,以确保时序优化的正确性。

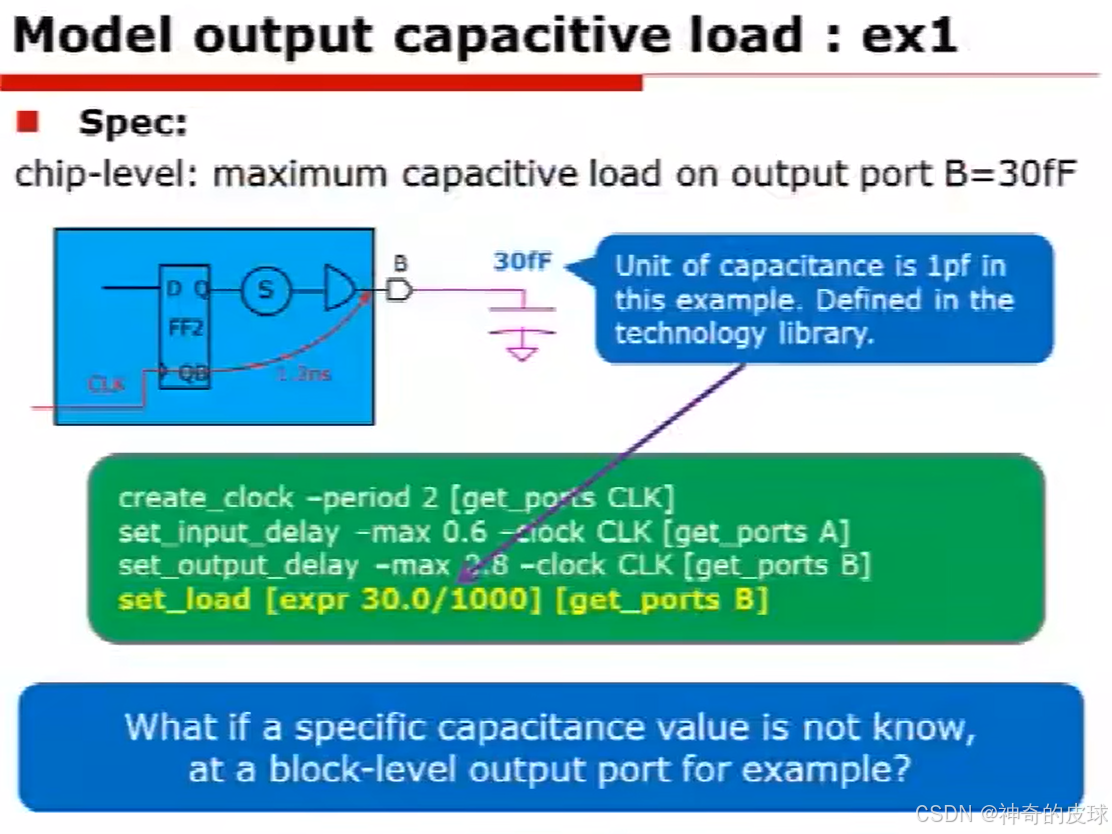

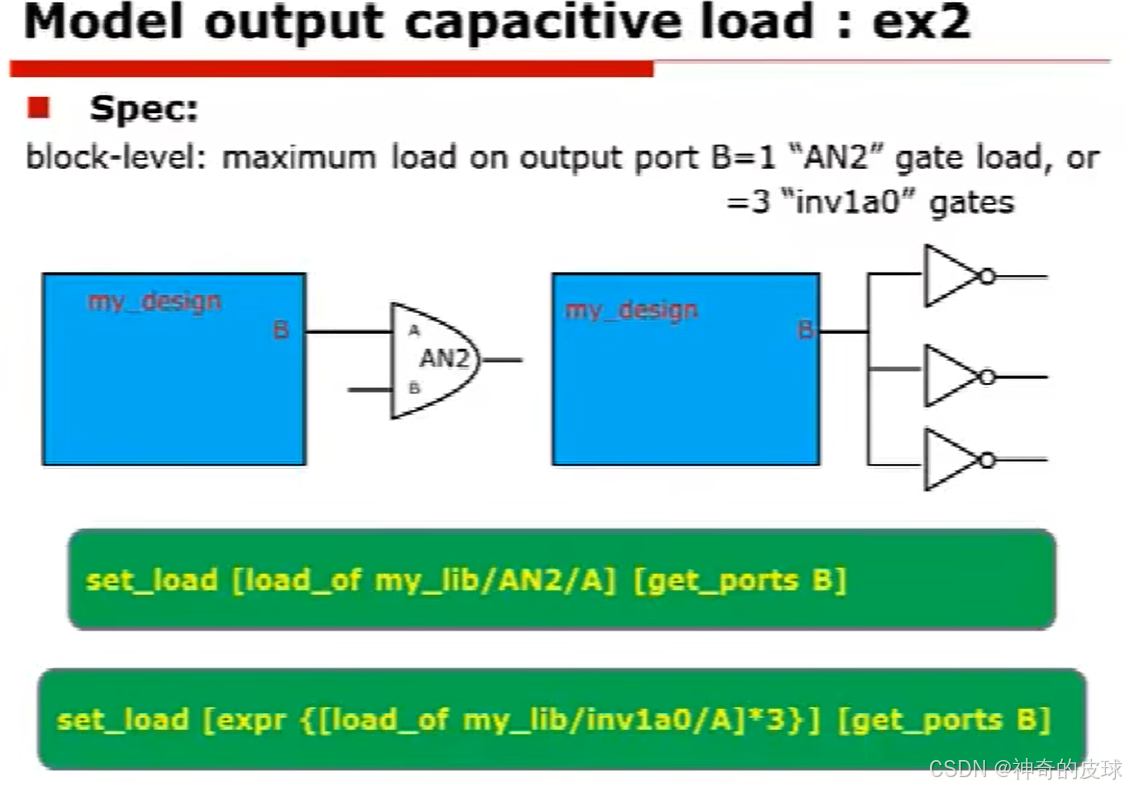

输出端口建模电容负载举例-1

-

时序约束

create_clock -period 2 [get_ports CLK] set_input_delay -max 0.6 -clock CLK [get_ports A] set_output_delay -max 0.8 -clock CLK [get_ports B] -

电容负载设置

set_load [expr 30.0/1000] [get_ports B]为输出端口B设置电容负载,使用了

expr计算,将30fF转换为0.03pF。输出端口建模电容负载举例-2

为单个负载设置:

set_load [load_of my_lib/AN2/A] [get_ports B]

load_of my_lib/AN2/A获取库中 AN2 门 A 引脚的负载值。- 这个命令直接将 AN2 门的负载应用到输出端口 B。

为多个负载设置(计算总负载):

set_load [expr {load_of my_lib/inv1a0/A*3}] [get_ports B]

load_of my_lib/inv1a0/A获取库中单个 INV1A0 门 A 引脚的负载值。- 通过

expr计算总负载为 3 个 INV1A0 门的负载值乘积。 - 结果应用到输出端口 B。

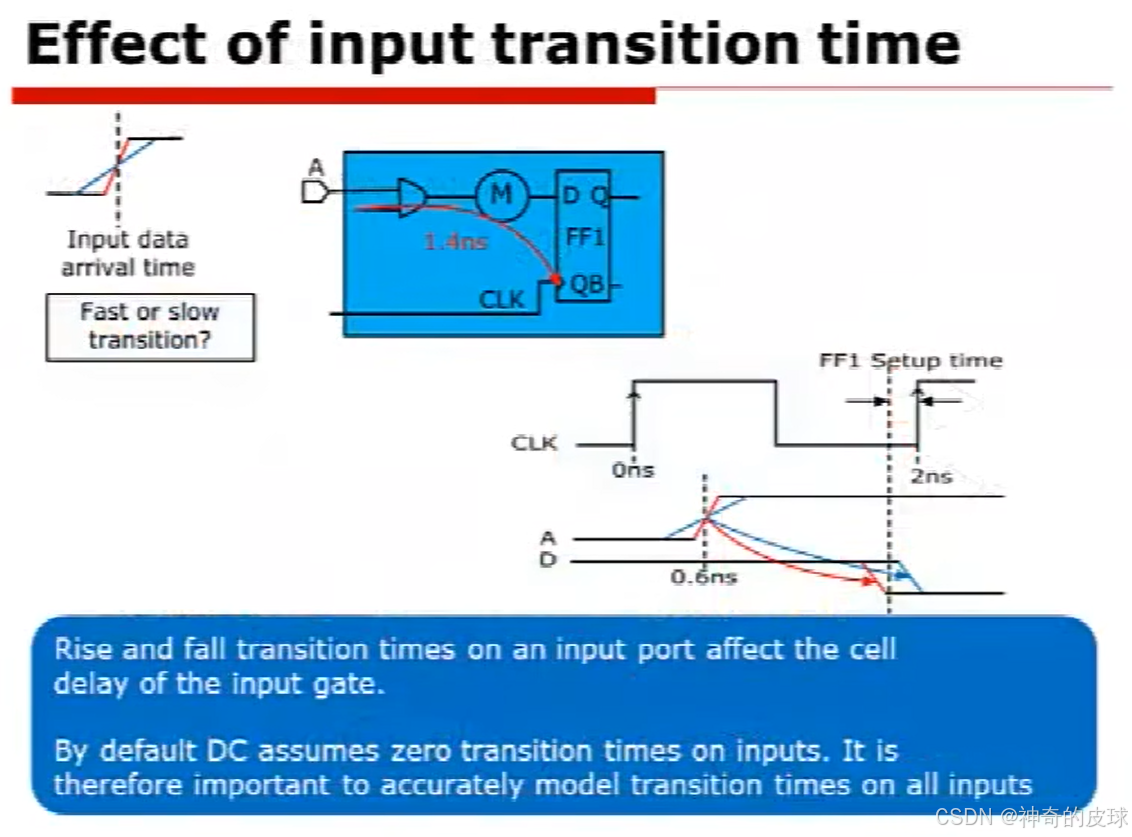

输入信号过渡时间的影响

输入信号的 上升时间(Rise Time) 和 下降时间(Fall Time) 会影响输入门的单元延迟。图中展示了一个 时钟驱动输入门 的例子

数据从输入端口 A 通过逻辑门 M 传输到触发器 FF1,输入信号过渡时间(如图曲线红色和蓝色所示)影响 M 的延迟。如果输入过渡时间较慢,M 的延迟可能增大至 1.4ns 或更高,导致信号在 触发器 FF1 的 Setup 时间 前未能稳定。

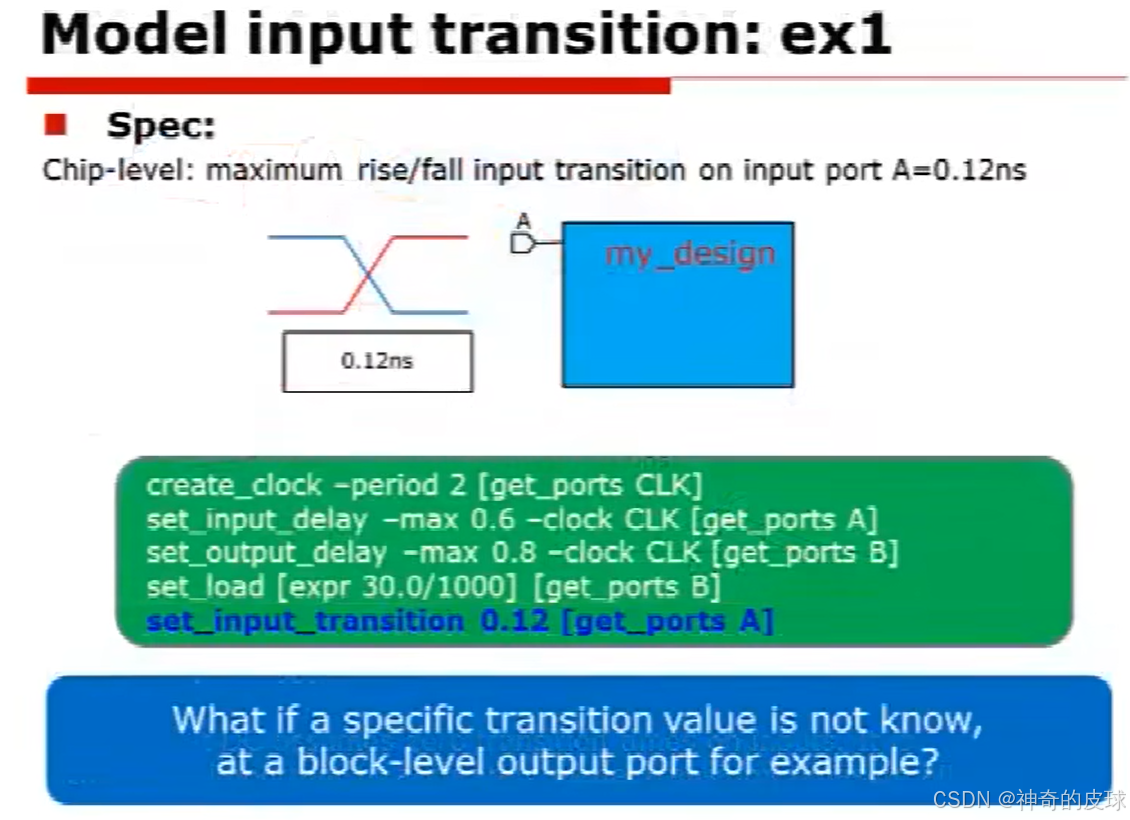

输入信号过渡时间建模举例-1

-

输入端口

A的最大上升/下降过渡时间被定义为 0.12ns。 -

使用

set_input_transition命令,明确指定输入端口A的过渡时间为 0.12ns:set_input_transition 0.12 [get_ports A]

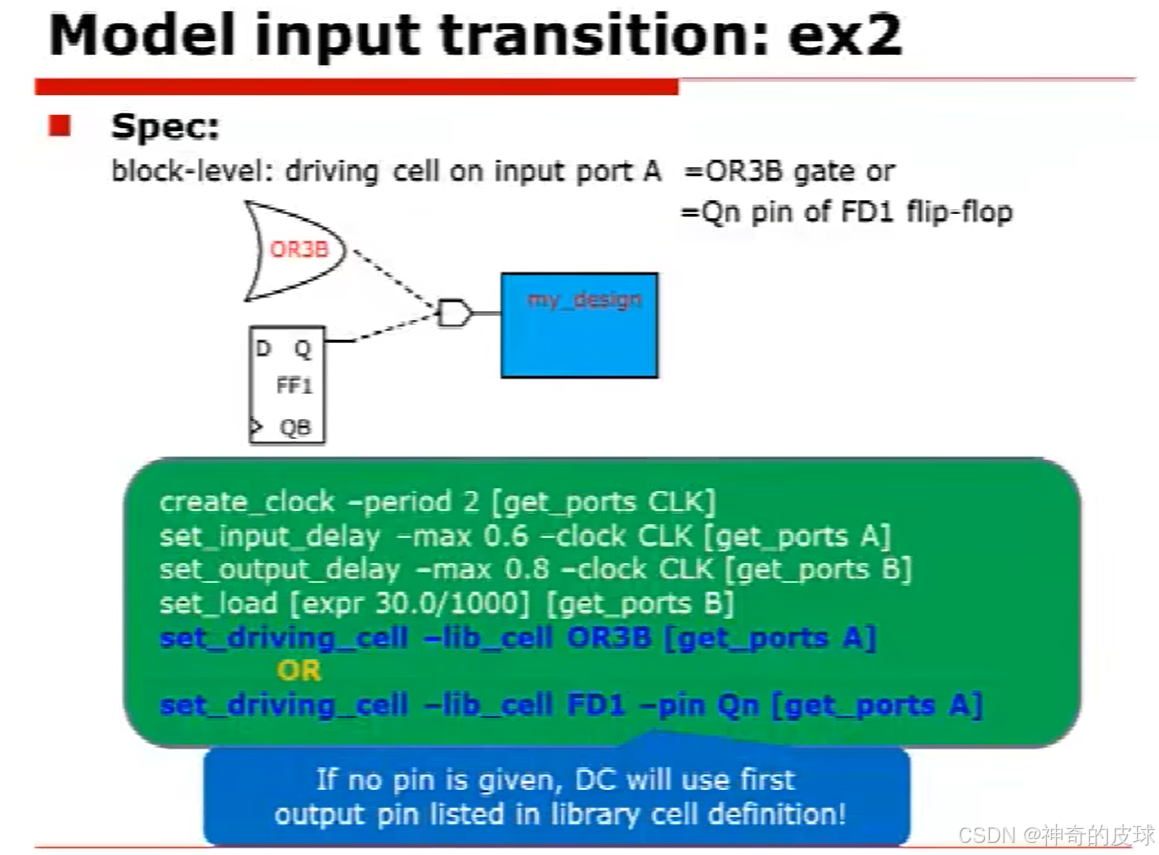

输入信号过渡时间建模举例-2

-

输入端口A由

OR3B门或FF1触发器的Qn引脚驱动 -

设置时序约束和负载

create_clock -period 2 [get_ports CLK] set_input_delay -max 0.6 -clock CLK [get_ports A] set_output_delay -max 0.8 -clock CLK [get_ports B] set_load [expr 30.0/1000] [get_ports B] -

设置驱动单元:

set_driving_cell -lib_cell OR3B [get_ports A]或者

set_driving_cell -lib_cell FD1 -pin Qn [get_ports A]如果没有指定引脚,DC(Design Compiler)将使用库单元定义中的第一个输出引脚作为默认值。

PVT(Process, Voltage, Temperature)的影响

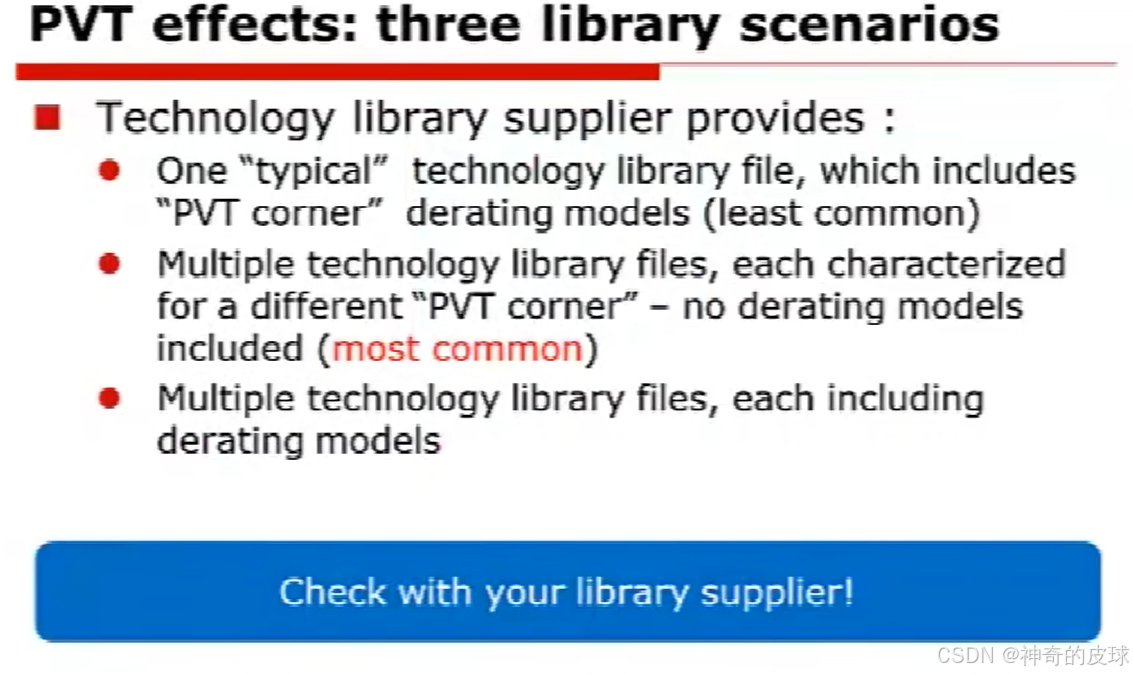

PVT有三种技术库场景

- 典型的技术库文件(最不常见):提供一个“典型”技术库文件,该文件包括与不同 PVT 条件相关的降额(derating)模型。

- 多个技术库文件(最常见):提供多个技术库文件,每个文件针对特定的 PVT 条件进行表征,不包括任何降额模型。

- 多个技术库文件,包含降额模型:提供多个技术库文件,每个文件都包含降额模型,用于不同的 PVT 条件。

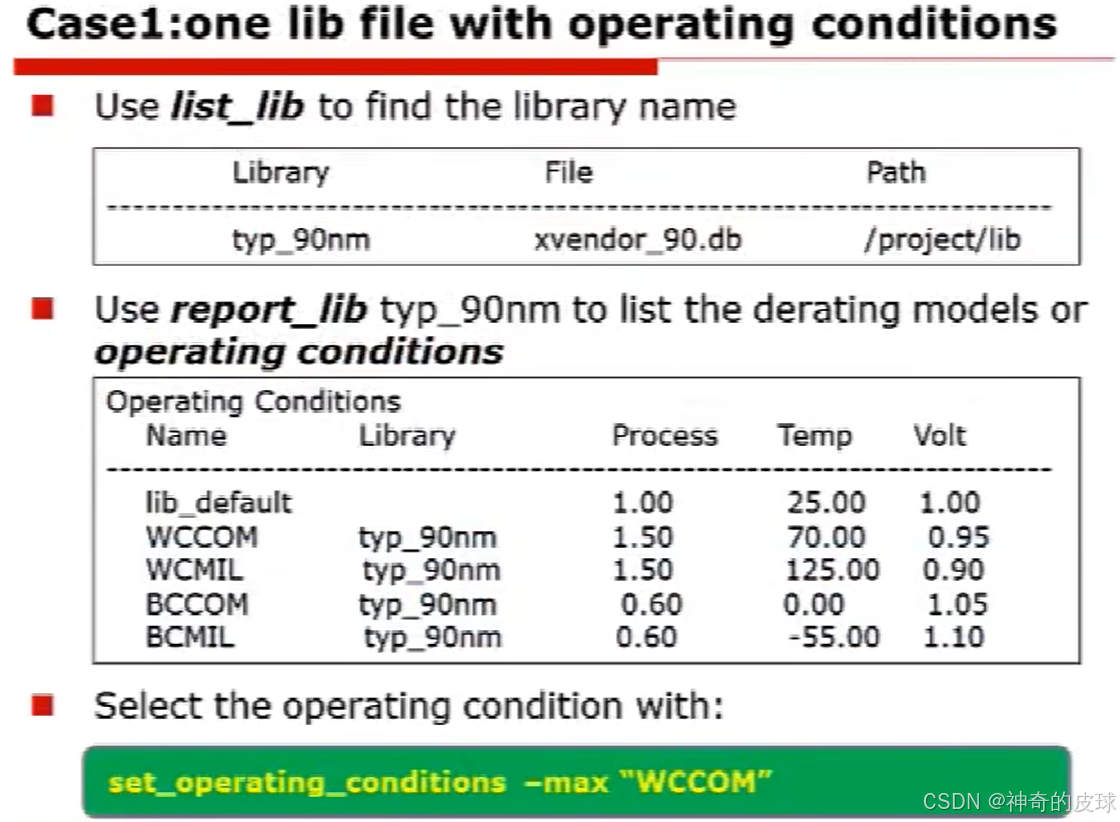

PVT举例-1-单个库文件及其操作条件

-

使用命令

list_lib可以列出库的名称,例如typ_90nm。 -

使用命令

report_lib typ_90nm,可以列出该库的降额模型(derating models)或操作条件(Operating Conditions)。 -

使用命令

set_operating_conditions指定所需的操作条件。例如下面命令将操作条件设置为WCCOM。set_operating_conditions -max "WCCOM"- lib_default:默认操作条件。

- WCCOM(Worst Case Common):最坏情况下的常规条件(高温低压)。

- WCMIL:最坏情况下的极限条件。

- BCCOM(Best Case Common):最佳情况下的常规条件(低温高压)。

- BCMIL:最佳情况下的极限条件。

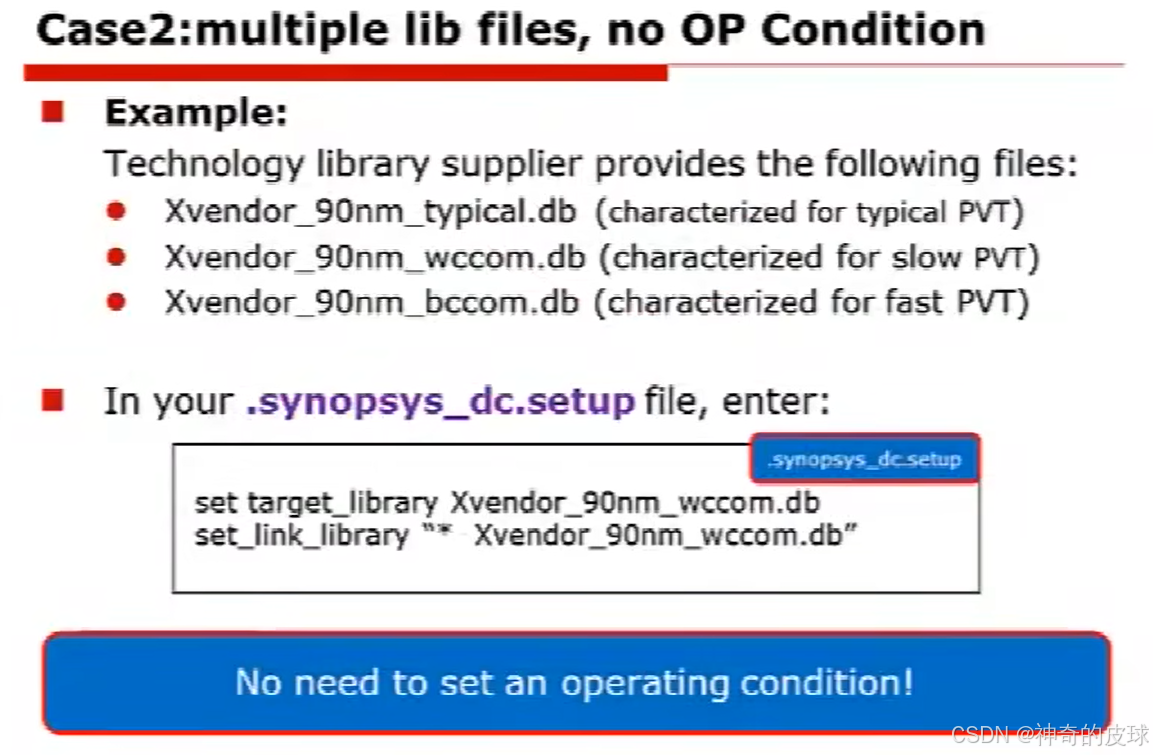

PVT举例-2-多库文件及无操作条件的情况

-

在此场景下,技术库供应商提供了多个库文件,每个库文件被单独表征为不同的 PVT(Process, Voltage, Temperature)条件,例如:

Xvendor_90nm_typical.db:表征典型 PVT 条件。Xvendor_90nm_wccom.db:表征最坏情况下的 PVT 条件(slow)。Xvendor_90nm_bccom.db:表征最佳情况下的 PVT 条件(fast)。

-

在

.synopsys_dc.setup文件中,添加以下内容以指定目标库和链接库:set target_library Xvendor_90nm_wccom.db set link_library "*" Xvendor_90nm_wccom.dbtarget_library:设置当前综合目标的库。link_library:用于指定链接库,用于逻辑操作和综合。

-

与需要通过

set_operating_conditions指定条件的情况不同,这里每个库文件已经单独表征了不同的操作条件,因此无需额外配置操作条件。

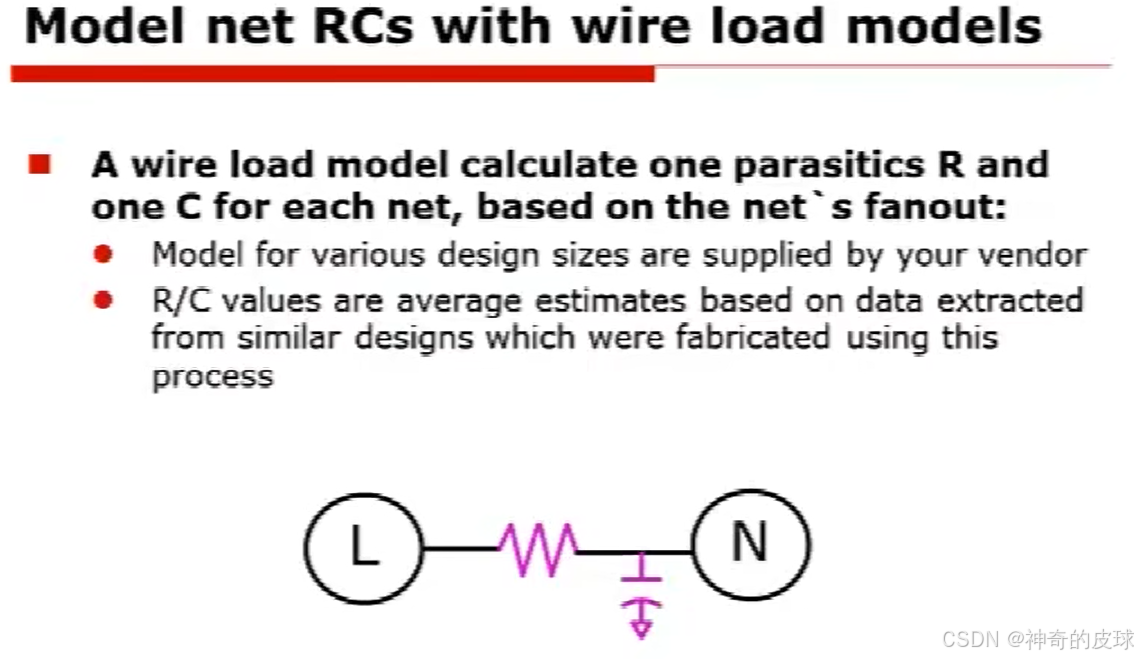

用线负载模型(Wire Load Model)建模网络RC参数

-

线负载模型(Wire Load Model)基于网络的扇出(Fanout),为每个网络计算一个寄生电阻 (R) 和一个寄生电容 (C)。

-

不同设计规模的线负载模型由供应商提供。

-

R 和 C 的值是基于类似设计中提取的数据的平均估算值。

-

这些数据来源于使用相同工艺制造的设计。

-

这些寄生参数会影响信号的传播延迟。

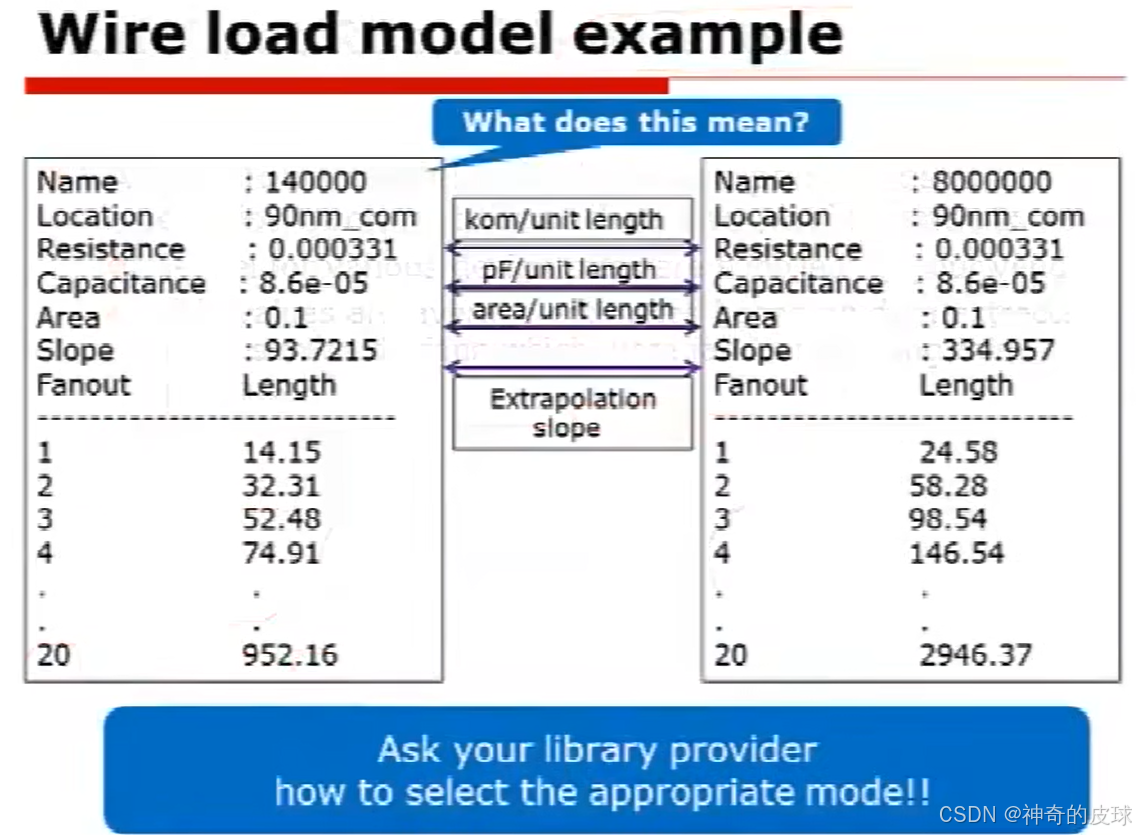

线负载模型举例

- Name: 模型的名称。

- Location: 工艺节点 (如90nm)。

- Resistance/Capacitance: 每单位长度的电阻和电容。

- Area: 布线面积。

- Slope: 用于插值或外推的斜率。

- Fanout vs. Length: 不同扇出数对应的布线长度。

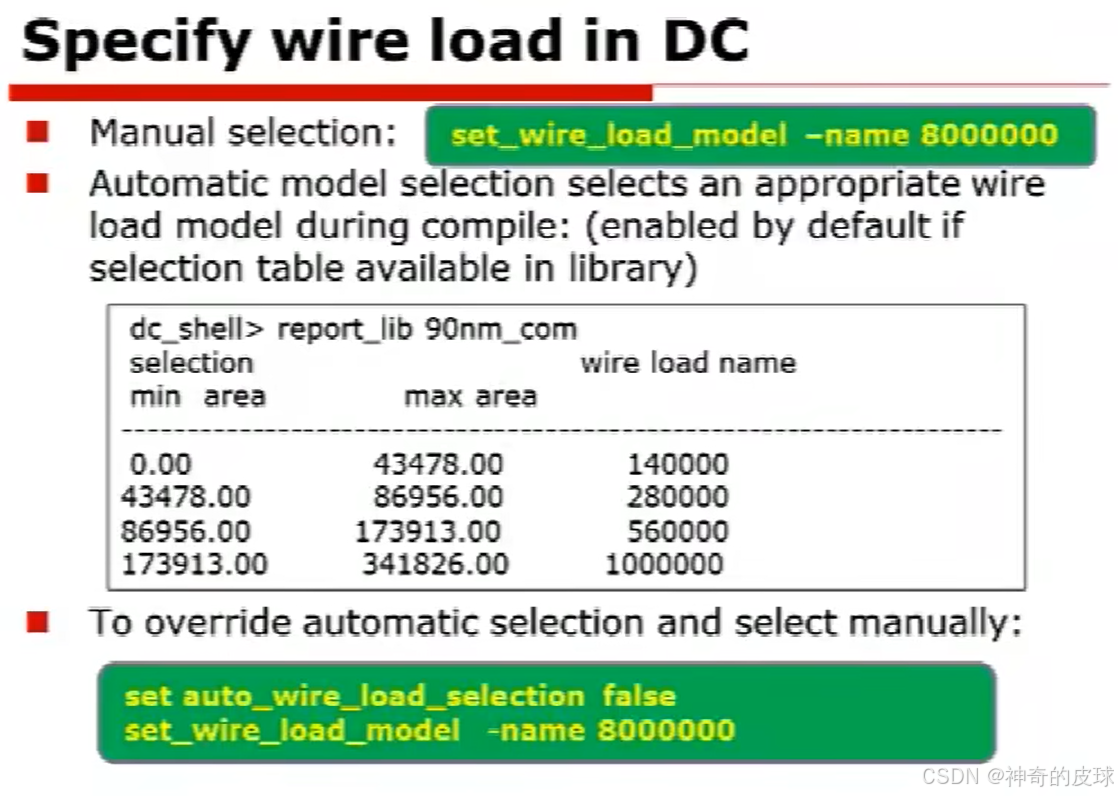

Specify Wire Load in DC

- 手动选择:使用命令

set_wire_load_model -name <model_name>指定具体的 wire load model。例如:set_wire_load_model -name 8000000。 - 自动选择:如果库中提供了选择表,综合工具可以根据面积自动选择合适的模型。默认开启自动选择功能。使用

report_lib查看可用的 wire load model 和对应的面积范围,工具会根据设计面积在范围内选择最接近的模型。 - 如果需要覆盖自动选择功能:

- 禁用自动选择:

set auto_wire_load_selection false - 手动设置模型:

set_wire_load_model -name <model_name>

- 禁用自动选择:

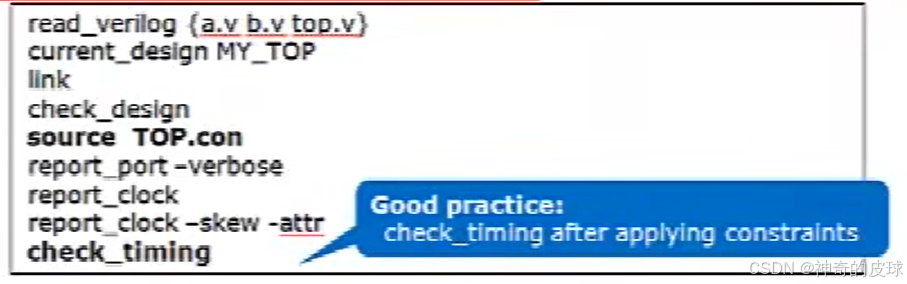

约束文件补充

Sourcing Constraints Files

-

将约束条件集中存放在独立的 Constraints 文件中,可以提高设计综合的效率和可维护性。文件内容可以在 DC-shell 中交互式地加载和执行。

加载约束文件的步骤:

- 读取设计文件:

read_verilog {a.v b.v top.v} - 指定当前设计:

current_design MY_TOP - 连接设计:

link - 检查设计完整性:

check_design - 加载约束文件:

source -echo -verbose TOP.con

加载命令解析:

source -echo -verboseecho: 显示执行命令的内容。verbose: 输出详细的加载信息,便于调试。

Executing run_scripts in Batch Mode

- 通过将运行命令存储在

run script中,可以一次性运行所有设计任务,在设计综合运行时,可以并行处理其他任务。

Batch Mode 命令格式

linux% dc_shell-topo -f RUN.tcl | tee -i dc.log

dc_shell-topo: 运行 Synopsys Design Compiler 的命令。f RUN.tcl: 指定包含运行命令的 Tcl 脚本文件。| tee -i dc.log: 将终端输出同时写入日志文件dc.log,以便后续调试。

脚本示例 (RUN.tcl)

read_verilog {a.v b.v top.v}

current_design MY_TOP

link

check_design

source -cho -verbose TOP.con

Constraints File Recommendation 1/3

- 在

ddc格式设计中,约束会被保存。 - 在应用新约束前,建议清除当前设计中的所有约束以避免冲突。

清理现有约束的命令:

reset_design

create_clock -period 2 [get_ports CLK]

reset_design: 清除设计中的所有约束,确保一个干净的环境。create_clock: 为时钟信号CLK创建新的时钟约束。- 如果使用多个约束脚本,确保只有一个

reset_design命令。 - 避免重复清除约束操作,确保设计流程的效率。

- 推荐在约束脚本的开头放置

reset_design。

Constraints File Recommendation 2/3

-

在编写 TCL 脚本时,建议添加注释以提高脚本的可读性和可维护性。

-

使用

#添加注释:# comments in TCL -

在同一行添加注释时,命令和注释之间必须以分号

;分隔。create_clock -p 5 -n VCLK ; # this is a virtual clock

Constraints File Recommendation 3/3

建议使用标准的扩展名以便于识别和管理,例如:

.tcl: 用于运行脚本,例如RUN.tcl.con: 用于设计约束文件,例如DESIGN.con

避免使用别名和缩写命令,使用完整的选项名称。例如: period 而非 p。

create_clock -period 5 [get_ports CLK] # 推荐使用完整命令

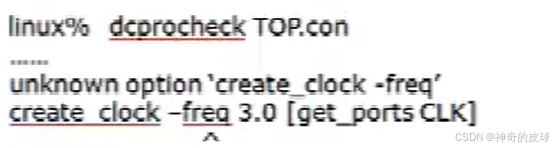

检查约束语法 (Check the Syntax of Constraints)

-

dcprocheck是一种用于约束文件语法检查的实用工具。由 DC提供,可以快速检查约束文件的语法错误。 -

在终端运行以下命令:

dcprocheck TOP.con -

示例输出:工具会显示错误行,并用

^指示出错的位置。错误显示create_clock使用了无效的选项freq。unknown option 'create_clock -freq' create_clock -freq 3.0 [get_ports CLK]

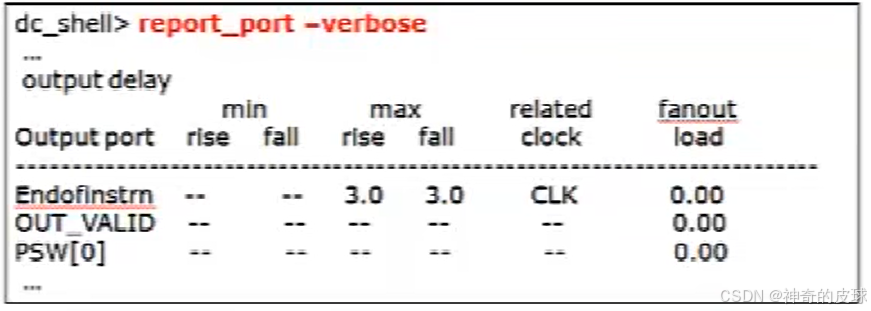

检查约束值或选项 (Check the Values/Options of Constraints)

检查端口约束 (非时钟约束):

report_port -verbose

检查时钟约束:

-

查看时钟波形:

report_clock -

查看时钟树规范:

report_clock -skew

检查缺失/不一致的约束 (Check for Missing/Inconsistent Constraints)

check_timing 命令提供以下问题的警告信息:

- 缺失的端点约束 (Missing Endpoint Constraints): 未定义路径终点的约束条件。

- 时钟问题 (Missing/Overlapping/Multiple Clocks): 检查是否存在缺失、重叠或多余的时钟定义。

- 时钟门控信号 (Clock-Gating Signals): 识别可能干扰时钟信号的门控信号。

- 其他问题 (And More): 包括路径冲突、不合理延迟等。

Redirect Checks and Reports to a File

将运行脚本的检查和报告输出到一个独立文件中,以便后续分析和记录设计流程。

-

使用

read_verilog命令加载 Verilog 文件:read_verilog {A.v B.v TOP.v} -

设置当前设计:

current_design MY_TOP -

使用

redirect命令将所有报告和检查的输出存储到precompile.rpt文件中。 -

格式:

redirect -tee -file precompile.rpt {command} -

示例:

redirect -tee -file precompile.rpt {link} redirect -append -tee -file precompile.rpt {check_design} redirect -append -tee -file precompile.rpt {source -echo -ver TOP.con} redirect -append -tee -file precompile.rpt {report_port -verbose} redirect -append -tee -file precompile.rpt {report_clock} redirect -append -tee -file precompile.rpt {report_clock -skew} redirect -append -tee -file precompile.rpt {check_timing} -

使用

append参数,可以将新的命令输出追加到同一文件中,而不是覆盖先前内容。 -

使用

tee选项,可以在屏幕上实时查看命令输出,同时将其保存到文件中。

1314

1314

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?