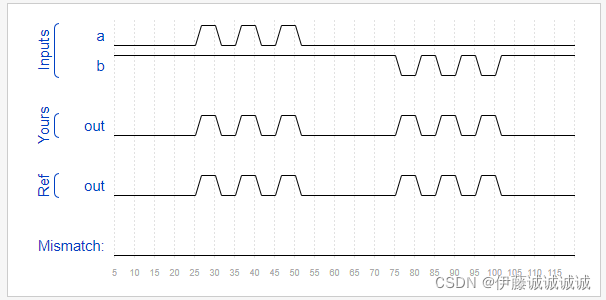

2.3.1、Modules

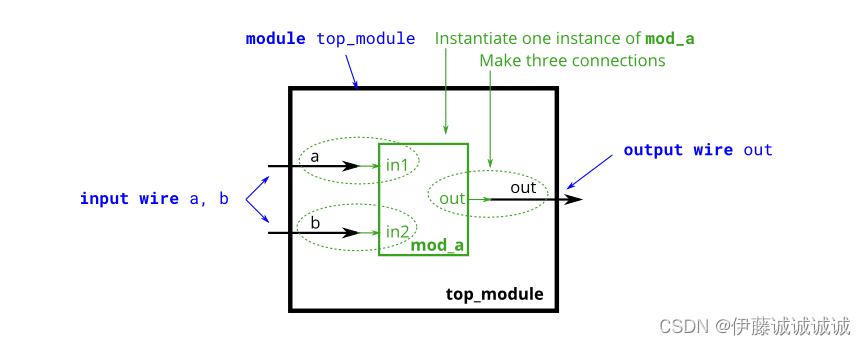

Module

Solution:

module top_module ( input a, input b, output out );

//模块名+例化名 (按顺序写出I/O口)

//mod_a mod (a, b, out);

//模块名+例化名 (.例化名称(例化地址), .(例化名称(例化地址)))

mod_a mod (.in1(a), .in2(b), .out(out));

endmoduleSubmit:

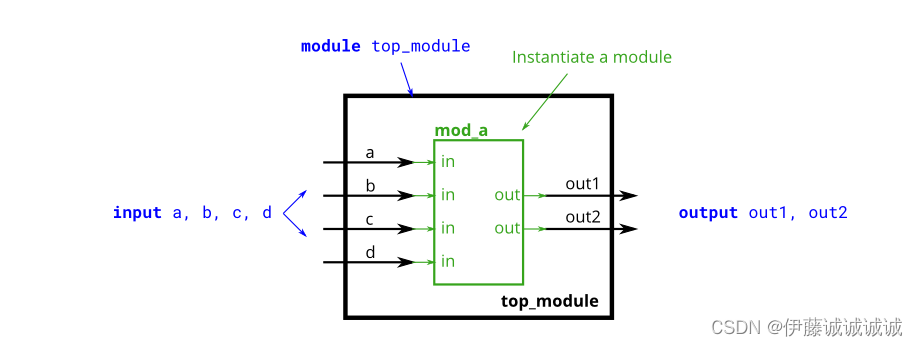

2.3.2、Module pos

This problem is similar to the previous one (module). You are given a module named

mod_athat has 2 outputs and 4 inputs, in that order. You must connect the 6 ports by position to your top-level module's portsout1,out2,a,b,c, andd, in that order.You are given the following module:

module mod_a ( output, output, input, input, input, input );

Solution:

module top_module (

input a

本文介绍了如何在VHDL和SystemVerilog中通过实例化和连接模块实现高级设计,包括按位置、名称和功能连接模块,以及模块级的位移和组合操作。涉及模块`mod_a`、`my_dff`和`add16`的实例与连接示例,展示了在32位加法器和多级shift register的设计中应用这些技术。

本文介绍了如何在VHDL和SystemVerilog中通过实例化和连接模块实现高级设计,包括按位置、名称和功能连接模块,以及模块级的位移和组合操作。涉及模块`mod_a`、`my_dff`和`add16`的实例与连接示例,展示了在32位加法器和多级shift register的设计中应用这些技术。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

696

696

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?