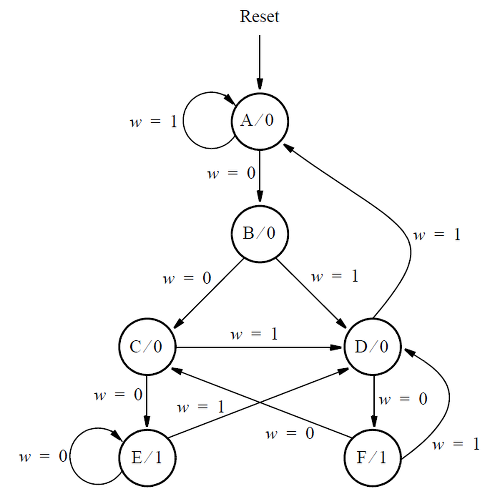

Consider the state machine shown below, which has one input w and one output z.

module top_module (

input clk,

input reset, // synchronous reset

input w,

output z);

//状态编码

parameter

A=0,

B=1,

C=2,

D=3,

E=4,

F=5;

reg[2:0] state ,next_state;

//下一状态的确定

always @(*)begin

case(state)

A:next_state=w?A:B;

B:next_state=w?D:C;

C:next_state=w?D:E;

D:next_state=w?A:F;

E:next_state=w?D:E;

F:next_state=w?D:C;

default:next_state='bx;

endcase

end

//状态转换

always @(posedge clk)begin

if(reset)

state<=A;

else

state<=next_state;

end

//确定输出

always @(*)begin

case(state)

A:z=0;

B:z=0;

C:z=0;

D:z=0;

E:z=1;

F:z=1;

default:z='bx;

endcase

end

endmodule

该模块是一个用Verilog编写的五状态机,有一个输入w和一个输出z。状态机在每个时钟上升沿更新状态,并根据当前状态和输入w决定下一个状态。输出z根据当前状态赋值,当处于状态E和F时,输出为1,其他状态为0。存在同步重置功能,当重置信号有效时,状态复位为A。

该模块是一个用Verilog编写的五状态机,有一个输入w和一个输出z。状态机在每个时钟上升沿更新状态,并根据当前状态和输入w决定下一个状态。输出z根据当前状态赋值,当处于状态E和F时,输出为1,其他状态为0。存在同步重置功能,当重置信号有效时,状态复位为A。

1096

1096

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?