目录

什么是时序电路?我曾写过一篇文章来阐述时序电路的一些概念。其实,简而言之,时序电路就是 “组合逻辑电路 + 锁存器/触发器 ”构成,组合逻辑电路主要完成电路功能,锁存器和触发器对数据进行保存,并且让输出的结果在时钟信号的节奏下有序稳定地输出。

锁存器由于其对电平敏感的特性在时序电路中比较少地使用(毛刺),我们大多数使用的是对触发沿敏感的触发器。

时序参数

要想进行时序分析,必定要先了解时序电路的有关参数。由上面的介绍我们知道,时序参数有关三个部分:

- 时种信号

- 触发器

- 组合逻辑

时钟信号

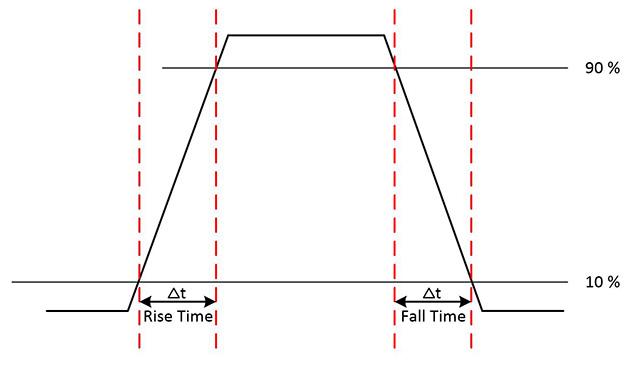

对于实际的物理电路而言,时钟信号的上升和下降都会消耗一定的时间,主要有两个参数:

- 上升时间

:时钟信号从高电平的10%上升到90%所需要的时间

- 下降时间

:时钟信号从高电平的90%下降到10%所需要的时间

并且我们认为只要时钟信号达到高电平的50%以上即为高电平有效,低于高电平50%即为低电平。

触发器

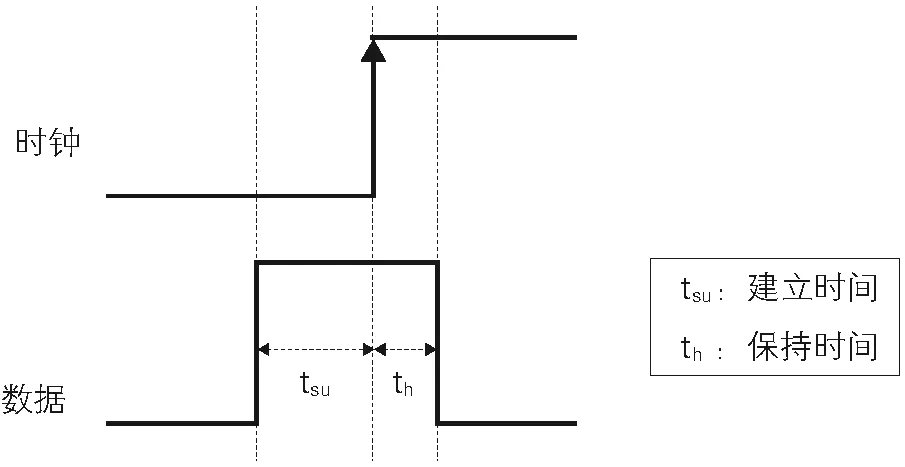

建立时间

时钟上升沿之前,数据输入必须有效的时间。

保持时间

时钟上升沿之后,数据输入必须保持有效的时间。

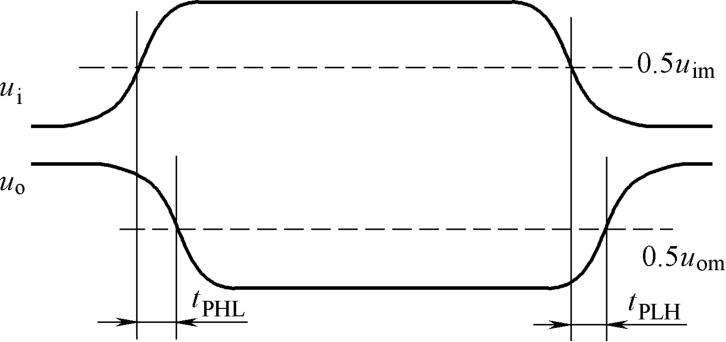

传输延迟

时钟上升沿到数据输出的时间(对于寄存器而言,数据输入有效即时钟触发沿)

即下图中的Tphl

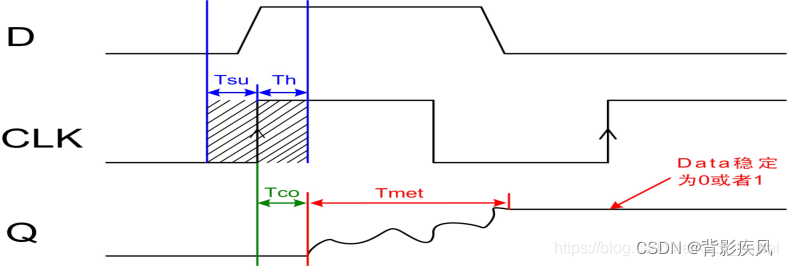

亚稳态时间

在保持时间后电路的输出一般会有一小段不稳定的状态,我们称之为亚稳态。亚稳态到稳定的状态之间的时间,我们称为亚稳态时间。

这里我想说的是,亚稳态理论上都是有的,只是如果不满足建立和保持时间的输入会导致更长的不稳定状态。看下图,虽然产生了亚稳态,但是在下一次触发沿来临前已经保持稳定,我们就可以认为这个亚稳态是正常的。

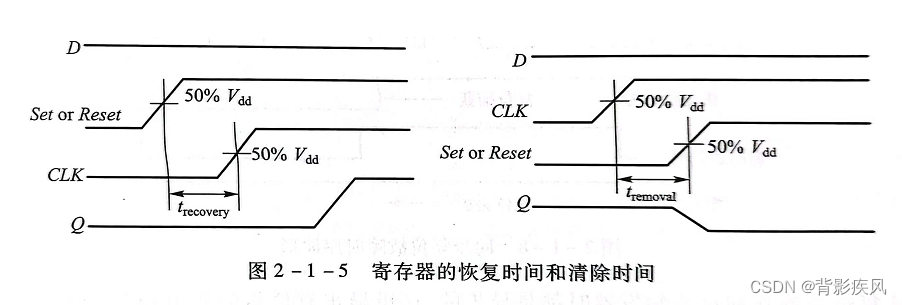

恢复时间

恢复时间是指 复位/置位信号 无效到触发沿来临的时间。也称为复位/置位信号的建立时间。

清除时间

清楚时间是指触发沿之后复位/置位信号仍然保持有效的时间,也称为复位/置位信号的保持时间。

组合逻辑电路

组合逻辑电路的关键时序参数是最小传输延时和最大传输延时

时钟信号的决定因素

对于一个同步时序电路,最小的时钟周期却决于最坏的传输延迟。

根据上面提到的时序参数我们可以得出,第一个时序约束:

最小时钟周期 > 触发器建立时间 + 触发器最大传输延时 + 组合电路最大传输延时

并且对于整体电路而言,总的传输延迟要大于寄存器保持时间。(要不然对与后一级的触发器而言会产生时序冲突)

寄存器保持时间 < 触发器最大传输延时 + 组合电路最大传输延时

本文详细介绍了时序电路中的核心参数,包括时钟信号的上升时间和下降时间、触发器的建立时间、保持时间及传输延迟等。同时,还探讨了组合逻辑电路的关键时序参数及其对整体电路性能的影响。

本文详细介绍了时序电路中的核心参数,包括时钟信号的上升时间和下降时间、触发器的建立时间、保持时间及传输延迟等。同时,还探讨了组合逻辑电路的关键时序参数及其对整体电路性能的影响。

8060

8060

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?