关于GICv3

GICv3体系结构设计为ARMv8-A和ARMv8-R设计。

GICv3支持:

- The ARMv8 architecture.

- Locality-specific Peripheral Interrupts(LPIs).

- Private Peripheral Interrupts (PPIs).

- Software Generated Interrupts (SGIs).

- Shared Peripheral Interrupts (SPIs).

- Interrupt masking and prioritization.

- Uniprocessor and multiprocessor systems.

- Wakeup events in power management environments.

对于每个PE,GIC架构描述了如何从系统内不同类型的中断生成IRQ和FIQ中断。ARMv8-A异常模型随后描述了PE如何处理这些IRQ和FIQ中断。

- GICv3体系结构支持与两种安全状态(Secure state和Non-secure state)相关的v3中断的路由和处理。

- GICv3架构支持用于处理与虚拟机相关联的虚拟中断。

GICv3相对于 GICv2的修改

GIC scalability

GICv2体系结构最多只支持八个PE,因此具有无法扩展到大型系统的功能。GICv3通过改变中断路由的机制(称为关联路由)和在中断分布中引入一个新组件(称为Redistributor)来解决这一问题。

Interrupt grouping

- Group 0的物理中断(physical interrupts)处理在最高的异常等级(Exception level-EL3)处理。

- Secure Group 1的物理中断(physical interrupts)预计将在Secure EL1处理。

- Non-secure Group 1的物理中断physical interrupts,在使用虚拟化的系统中,在Non-secure EL2处处理。或在不使用虚拟化系统的Non-secure EL1处处理。

在GICv3中,中断分组支持:

- 将每个中断配置为Group 0,、Secure Group 1或Non-secure Group 1。

- 使用FIQ异常请求向目标PE发送Group 0物理中断信号。

- 安全模式下,Group 1的物理中断可以使用IRQ。

- 用于处理Group 0和Group 1中断优先级的统一方案。

Interrupt Translation Service (ITS)

中断翻译服务,

提供功能允许软件控制转发到ITS的中断如何转换为:

- GICv3和GICv4中的物理中断。

- 虚拟中断,仅在GICv4中。

ITS还允许软件确定转换中断的目标Redistributor。软件可以通过命令接口和存储器中相关的基于表的结构来控制ITS。中断翻译服务(ITS)的输出总是LPI,这是一种基于消息的中断形式。

Locality-specific Peripheral Interrupts (LPIs)

LPI是一种新的中断类型,它大大扩展了GIC可以处理的中断ID空间。LPI是可选的,如果实现,则可以由中断翻译服务ITS生成和支持。

Software Generated Interrupts (SGIs)

由于GICv3支持大规模系统,SGI的上下文被修改,不再包含源PE的身份。

Shared Peripheral Interrupts (SPIs)

在Distributor中添加了一组新的寄存器,以支持基于消息的SPI的设置和清除。

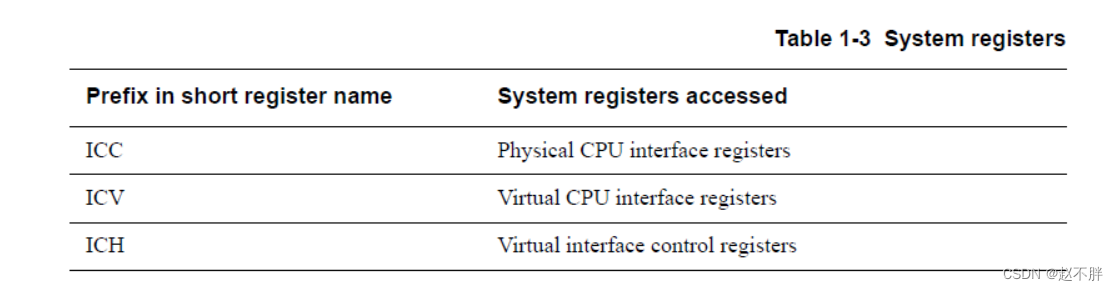

System register interface

该接口使用ARMv8-A或ARMv8-R PE中的系统寄存器指令为CPU interface寄存器提供紧密耦合的接口。

该接口用于与中断处理和优先级屏蔽直接相关的寄存器。

对于虚拟化,以这种方式访问的寄存器既包括由VM中断处理程序访问的寄存器,也包括将虚拟中断从管理程序转发到VM的寄存器。

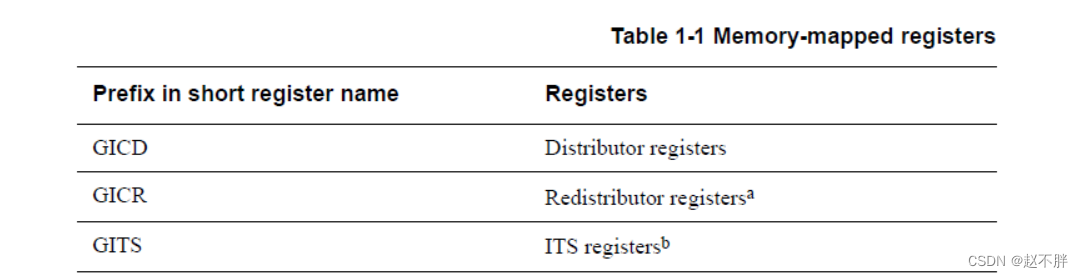

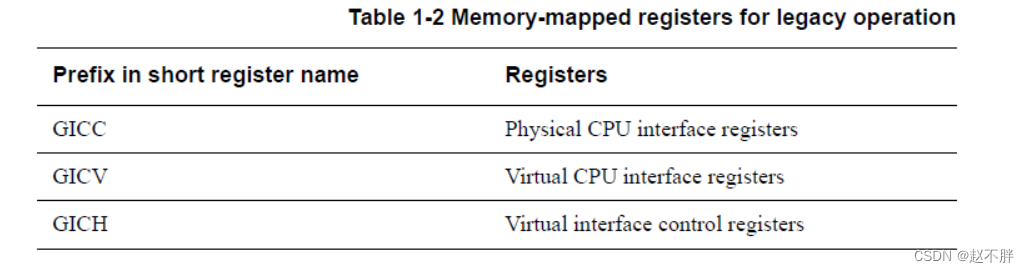

所有其他寄存器都是内存映射的。

对于AArch64状态,通过以下设置启用对系统寄存器接口的访问:

- ICC_SRE_EL1.SRE == 1.

- ICC_SRE_EL2.SRE == 1.

- ICC_SRE_EL3.SRE == 1.

…

Changes specific to GICv4

GICv4增加了对虚拟中断直接注入VM的支持,而不涉及虚拟机管理程序。只有实现至少一个将中断转换为LPI的ITS的系统才支持直接注入。

Terminology

Interrupt types

Locality-specific Peripheral Interrupt (LPI)

LPI是一个目标外围中断,它被路由到关联层次结构中的特定PE:

- 在启用了两种安全状态的系统中,LPI始终是非安全group 1中断。

- LPI具有边缘触发行为。 可使用ITS路由LPI。

- LPI没有激活状态,因此不需要显式停用。

- LPI始终是基于消息的中断。

Private Peripheral Interrupt (PPI)

这是一个以单个特定PE为目标的外围中断,不同PE可以使用相同的中断号来指示不同的事件:

- PPI可以是group 0中断、group 1安全中断或group 1非安全中断。

- PPI可以支持边缘触发或水平触发。

- PPI从不使用ITS路由。

- PPI处于激活状态,因此需要明确停用。

Shared Peripheral Interrupt (SPI)

这是一个外围中断,分发服务器可以将其路由到可以处理该中断的指定PE,或者路由到系统中已配置为接受此类中断的一组PE之一的PE:

- SPI可以是group 0中断、安全group1中断或非安全group1。

- SPIs可以支持边缘触发或水平触发。

- SPIs从不使用ITS路由。

- SPIs具有活动状态,因此需要显式停用。

Software Generated Interrupt (SGI)

SGI通常用于处理器间通信,并通过写入GIC中的SGI寄存器生成:

- SGI可以是group 0中断、group 1安全中断或group 1非安全中断。

- SGI具有边缘触发行为。

- SGI从不使用ITS路由。

- SGI处于激活状态,因此需要显式停用。

Interrupt states

Inactive : not active 或者pending的中断。

Pending: 由于硬件或者软件生成,并等待由目标PE处理的中断状态。

Active: 一种已被PE确认并正在处理的中断,且该时间段没有同样的中断给PE。

LPI没有活动状态,并在PE确认后转换到非活动状态。

Active and pending:同一个中断,从中断的一个断言开始处于活动状态,从后续断言开始处于挂起状态。

LPI不具有活动和挂起状态,并且在PE确认后转换到非活动状态。

Models for handling interrupts

在多处理器实现中,存在以下用于处理中断的模型:

Targeted distribution model

该模型适用于所有PPI和所有LPI。软件指定的目标PE接收中断。

Targeted list model

此模型仅适用于SGI。多个PE独立地接收中断。当PE确认中断时,仅为该PE清除中断挂起状态。在PE确认中断之前,每个PE的中断保持独立挂起。

1 of N model

此模型仅适用于SPIs。中断以指定的PE集合为目标,并且仅在该集合中的一个PE上执行。该体系结构对可选择PE施加限制。

其他项

Idle priority

在GICv3中,空闲优先级是在CPU interface 上没有中断活动时从ICC_RPR_EL1读取的运行优先级。

Interrupt Identifier (INTID)

唯一标识具有关联事件及其源的中断的数字空间。然后将中断路由到一个或多个PE进行处理。PPI和SGI中断号对每个PE都是本地的。SPI和LPI具有物理域的全局中断号

Interrupt Routing Infrastructure (IRI)

Distributor, Redistributors 以及 ITSs

Message-based interrupt

基于消息的中断是由于对指定地址的内存写入访问而被断言的中断。物理中断可以转换为基于消息的中断。

GICv3支持两种基于消息的中断机制:

- 一种SPI通信机制,其中分配的地址保存在Distributor中。

- 一种传送LPI的机制,其中分配的地址保存在ITS中(如果实施了ITS),或保存在Redistributor中。

Physical interrupt

以物理PE为目标的中断是物理中断。它由PE所连接的物理CPU interface向PE发出信号。

Running priority

在任何给定时间,CPU interface的运行优先级为:

- 活动中断的组优先级,该接口上没有优先级下降。

- 如果接口上没有优先级下降的活动中断,则运行优先级为空闲优先级

Sufficient priority

GIC CPU interface将启用的未决中断的优先级与以下所有值进行比较,以确定中断是否具有足够的优先级:

- 优先级掩码寄存器ICC_PMR_EL1。

- 接口的抢占设置,如ICC_BPR0_EL1和ICC_BPR1_EL1所示。

- CPU接口的当前运行优先级,如ICC_RPR_EL1所示。

如果中断具有足够的优先级,则向连接的PE发出信号。

Virtual interrupt

以VM为目标的中断是虚拟中断。它由关联的virtual CPU interface发出信号。

Maintenance interrupt

一种物理中断,用信号通知与VM上的中断处理相关的关键事件,以允许管理程序跟踪这些事件。这些事件由管理程序处理,包括启用和禁用一组特定的中断。

Supported configurations and compatibility

在ARMv8-A中,EL2和EL3是可选的,PE可以支持其中一个、两个或两个异常级别。

- PE要求EL3同时支持安全和非安全状态。

- PE需要EL2来支持虚拟化。

- 如果未实现EL3,则只有一个安全状态。此安全状态为安全状态或 非安全状态。

Affinity routing configuration

- 非对称配置,其中非安全状态启用关联路由,安全状态禁用关联路由。这为安全的传统环境提供了支持。

- 在legacy-only环境中,安全状态和非安全状态都禁用了关联路由。

System register configuration

当在两种安全状态下都启用了关联路由以执行时,GIC必须配置为使用系统寄存器访问以处理物理中断。

GIC control and configuration

许多GIC寄存器提供不同的形式,以允许有效的中断处理:

- For two Security states.

- For different interrupt groups.

- Using System register access for GICv3 or memory-mapped access for legacy

operation.

加粗样式

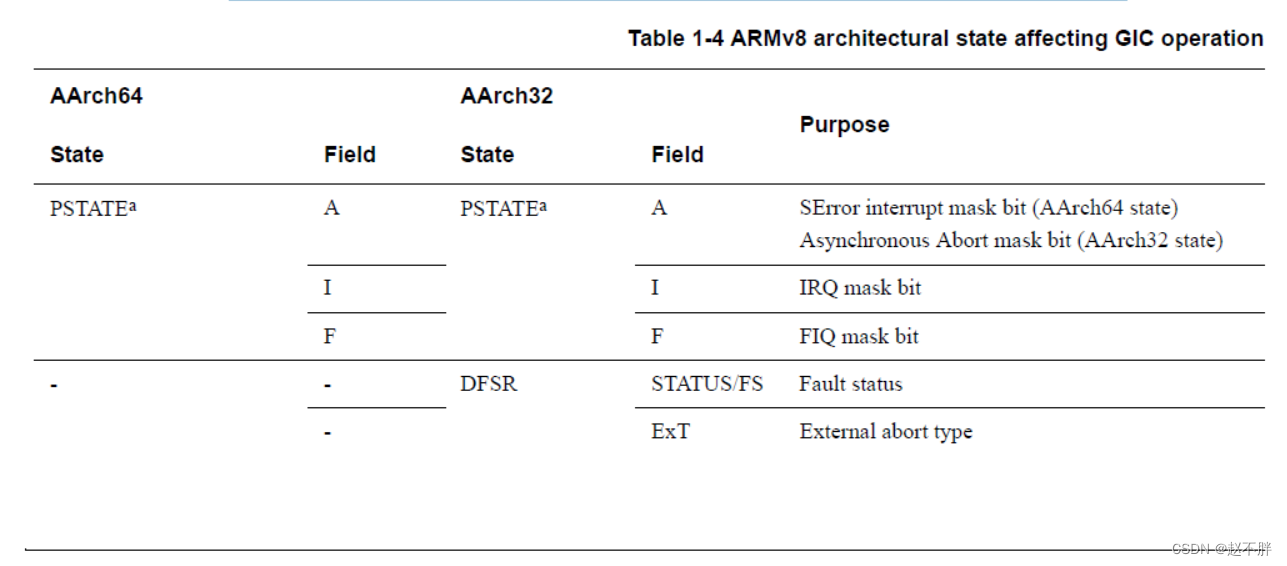

ARMv8对虚拟化的支持和PE运行的异常级别决定了physical CPU interface 寄存器还是virtual CPU interface 寄存器被访问。

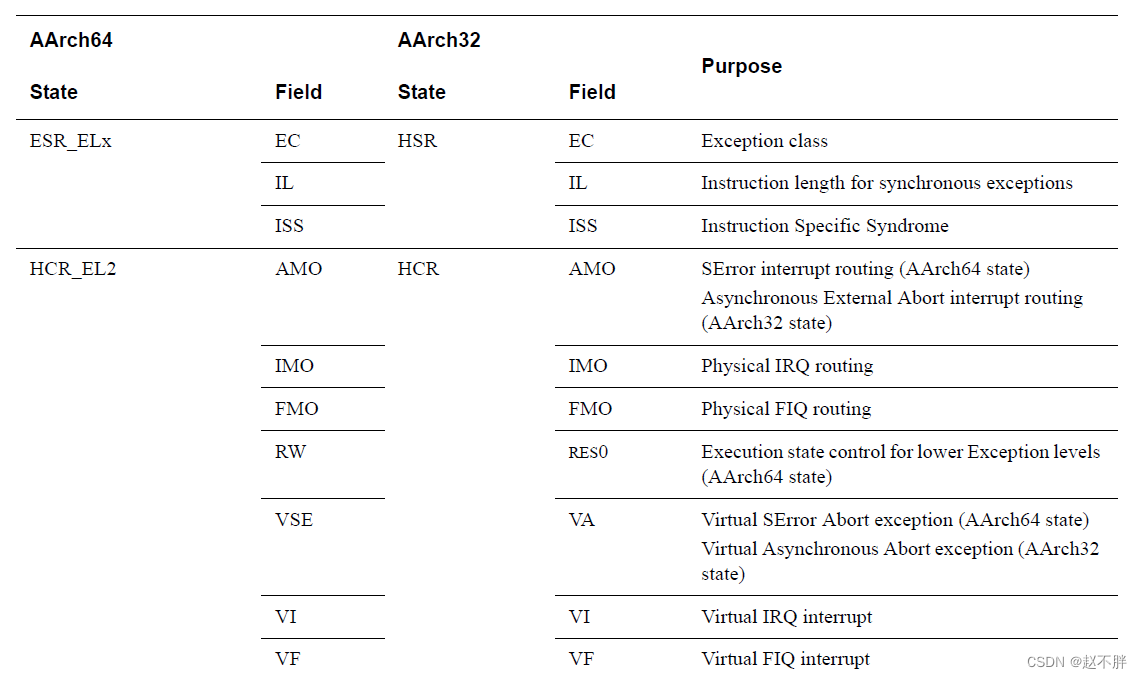

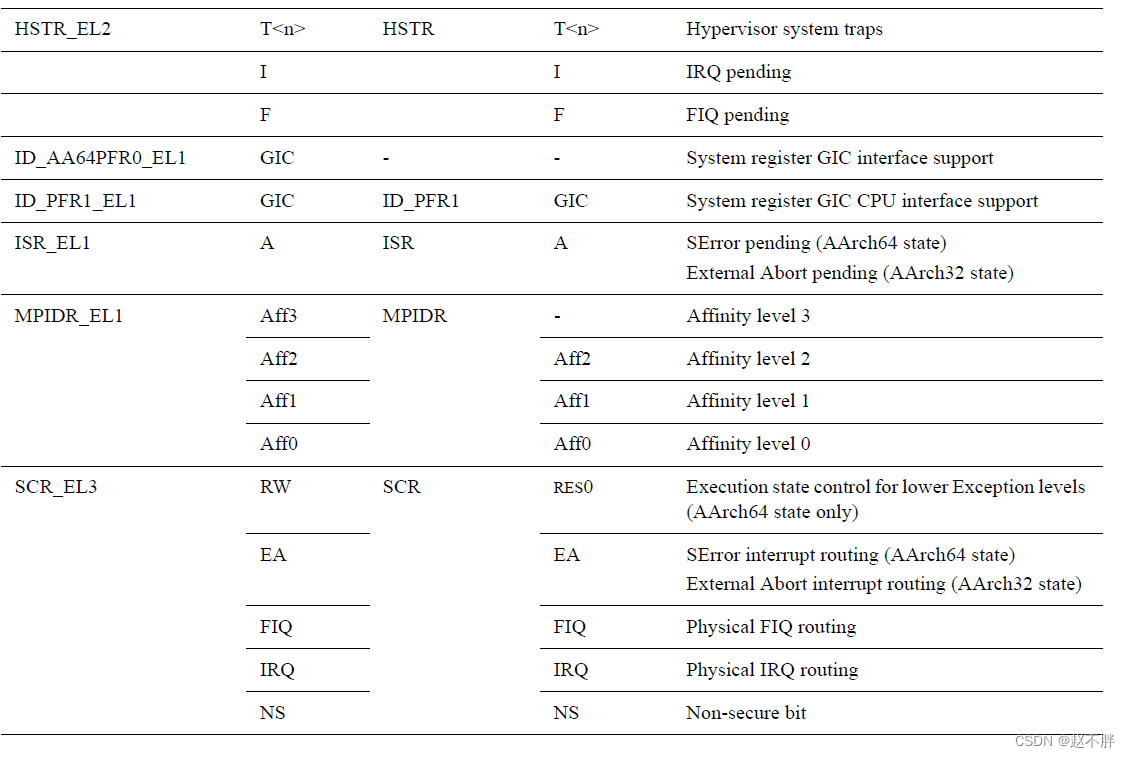

下表显示了与GIC一起使用或影响GIC运行的ARMv8体系结构状态。

566

566

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?