传送门:

规则90 - HDL数据 (01xz.net) https://hdlbits.01xz.net/wiki/Rule90题目:

https://hdlbits.01xz.net/wiki/Rule90题目:

Rule90 需要按照表中规则来生成一维序列。

规则很简单。一维序列中元素有 1开/0 关两种状态

在每个时钟边沿到来时刻,元素的下一个状态为元素相邻两个元素的异或。

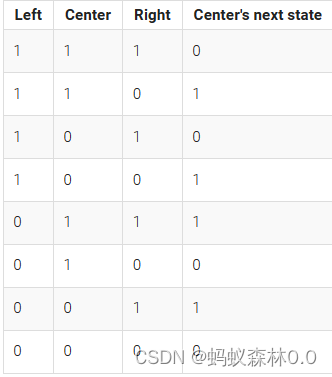

下表更详细地给出规则,元素下一个状态可以视作输出,输入为元素本身(中)与左右的状态。

负载输入指示系统的状态应加载数据[511:0]。假设边界 (q[-1] 和 q[512]) 均为零 (off)。

以下为本人提供的代码,有更好的代码欢迎评论区提供:

module top_module(

input clk,

input load,

input [511:0] data,

output [511:0] q );

always@(posedge clk)

begin

if(load)

q <= data;

else

q <= (q<<1)^(q>>1);

end

endmodule

本文介绍了Rule90算法在电路设计中的应用,通过Verilog代码实现了一维序列的生成,规则基于相邻元素的异或操作。代码展示了如何在时钟边沿触发下,根据给定数据或自动生成状态更新。

本文介绍了Rule90算法在电路设计中的应用,通过Verilog代码实现了一维序列的生成,规则基于相邻元素的异或操作。代码展示了如何在时钟边沿触发下,根据给定数据或自动生成状态更新。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

261

261

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?