文章目录

学习不能稀里糊涂,要学会多思考,发散式学习以及总结:

FPGA作为一种器件,只是实现目的的一种方法,过度追求实现的技术细节(用hdl还是hls,用啥芯片,用啥接口)容易只见树木不见森林。工具软件的用法也好,器件的架构也好,语言孰优孰劣的争论也罢。工程应用里大概更多应该去考虑适合的实现方式,现在software define network/flash/xxx,已然大势所趋,算法是纲,纲举目张。是因为在实现上需要有流水线,多路并行,快速部署的目的所以考虑使用FPGA,而不是为了使用而使用。

不管实现目的的方法是FPGA还是DSP甚至是GPU,这些都是工具,工程师的核心竞争力除了在于熟练地掌握开发的技巧。更重要的在于信号与系统、数字信号处理、图像处理之类的让你了解算法、优化算法的基石;以及数字电路、微机原理、处理器体系结构这些让你了解为什么这些工具要这样设计,要这样发展的课程(系统学习一点体系结构,那么这些数据级并行、指令级并行、线程级并行的处理器就不再陌生了)工程师应该顶天(了解应用,了解算法)也应该立地(了解工具,掌握技巧)。

——引用某个大佬的话,作为学习共勉

简单来说就是:FPGA是工具用来搬砖,更多的知识在FPGA之外

一、 IP核接口介绍

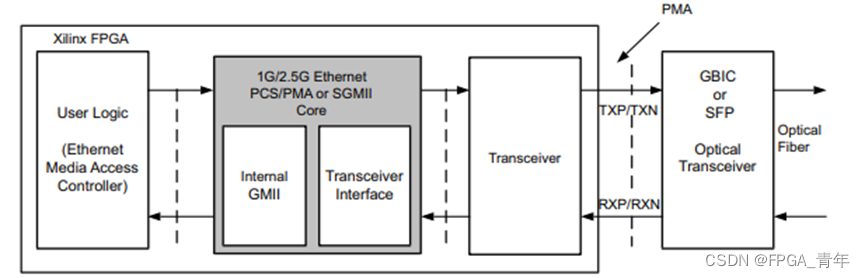

根据此系列的文章(一)以太网知识补给和文章(二)IP核配置,本次设计的逻辑框架如下,User Logic是需要我们编写代码,1G/2.5G Ethernet是我们配置的IP核,它们之间通过GMII接口通信;Transceiver也是IP核内部用来并转串的连接方式,最后GBIC or SFP为FPGA外部连接的PHY芯片,它们之间通过GT收发器接口通信(高速接口)。

FPGA程序是我们着重编写的是User Logic这一块,IP核会用接口就行,本章将先讲一下我们在(二)中配置的IP核后生成的接口。

文章介绍了FPGA设计中的IP核接口,强调了工程师应关注算法和工具的结合。重点讨论了一款1G/2.5GEthernetIP核,它通过GMII接口与UserLogic交互,并通过GT收发器进行高速串行通信。在框架搭建中,提到了回环模式用于仿真,并说明了FIFO在异步时钟和数据转换中的作用。文章还提及了以太网IP核在MAC层与PHY层之间的通信功能。

文章介绍了FPGA设计中的IP核接口,强调了工程师应关注算法和工具的结合。重点讨论了一款1G/2.5GEthernetIP核,它通过GMII接口与UserLogic交互,并通过GT收发器进行高速串行通信。在框架搭建中,提到了回环模式用于仿真,并说明了FIFO在异步时钟和数据转换中的作用。文章还提及了以太网IP核在MAC层与PHY层之间的通信功能。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

7625

7625