摘要

- 在使用case语句且多输出时,每个case分支语句都要给出所有输出的赋值,否则电路会综合出锁存器。

- 在下面例子中,通过变量sel来选择四个输出up、down、left、right哪一个被赋值为1,给出了两种代码实现方式。

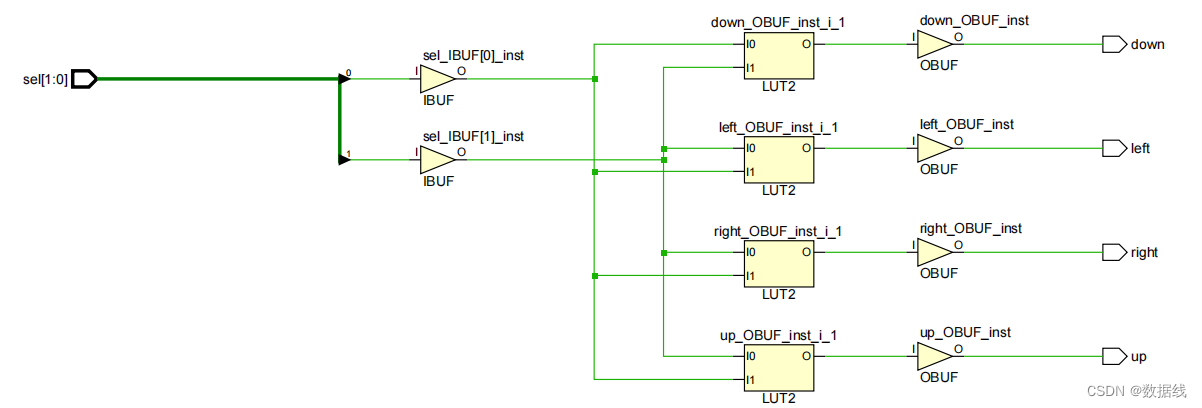

- 第一种实现方式中,每个case的分支语句给出了所有输出的值。

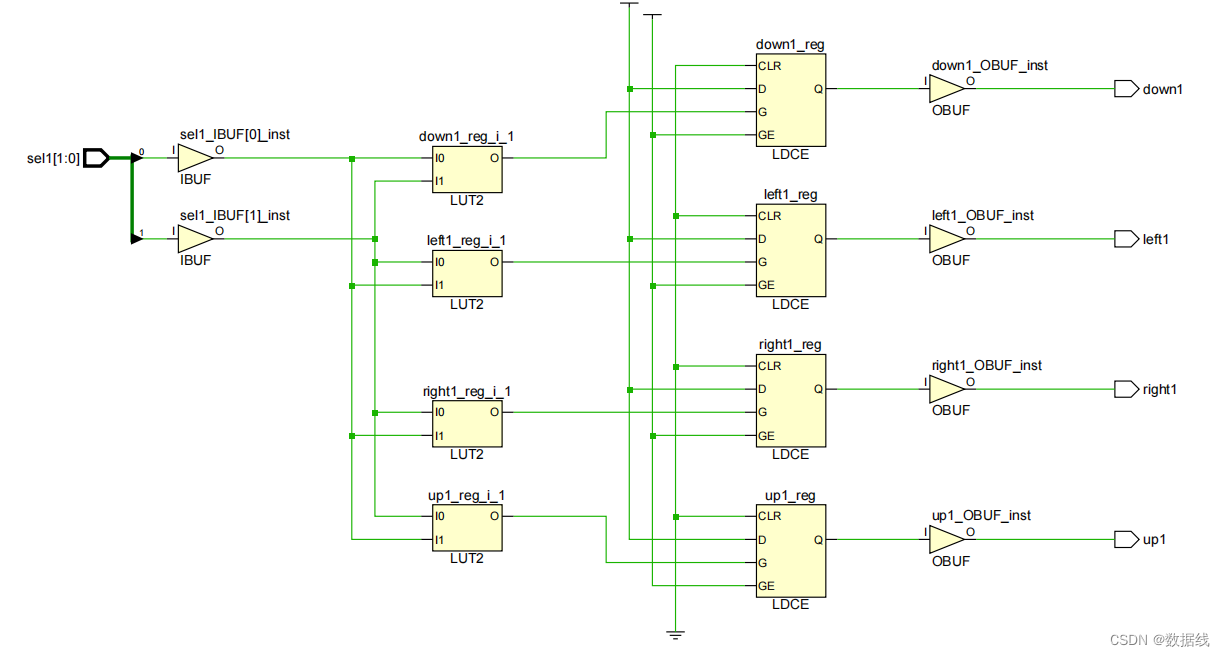

- 第二种实现方式中,虽然指定了变量的初始值,但每个case语句中并未对所有变量赋值。

代码

`timescale 1ns / 1ps

module top(

input [1:0] sel,

input [1:0] sel1,

output reg up,

output reg down,

output reg left,

output reg right,

output reg up1=0,

output reg down1=0,

output reg left1=0,

output reg right1=0

);

always@(*)begin

up=0;down=0;right=0;left=0;

case(sel)

2'b00:up=1'b1;

2'b01:down=1'b1;

2'b10:right=1'b1;

2'b11:left=1'b1;

default:up=1'b1;

endcase

end

always@(*)begin

case(sel1)

2'b00:up1=1'b1;

2'b01:down1=1'b1;

2'b10:right1=1'b1;

2'b11:left1=1'b1;

default:up1=1'b1;

endcase

end

endmodule

综合后的电路

由综合后的原理图可以看出,第二种代码实现方式产生了LDCE(异步清零的latch)

本文揭示了在Verilog设计中,使用case语句时,若不为所有输出赋值可能导致的LDCE问题。通过实例对比两种代码实现,解释了为何第二种方法导致异步清零 latch。理解并避免这种陷阱有助于提高电路设计的正确性和效率。

本文揭示了在Verilog设计中,使用case语句时,若不为所有输出赋值可能导致的LDCE问题。通过实例对比两种代码实现,解释了为何第二种方法导致异步清零 latch。理解并避免这种陷阱有助于提高电路设计的正确性和效率。

9032

9032

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?