Vivado下按键实验

实验原理

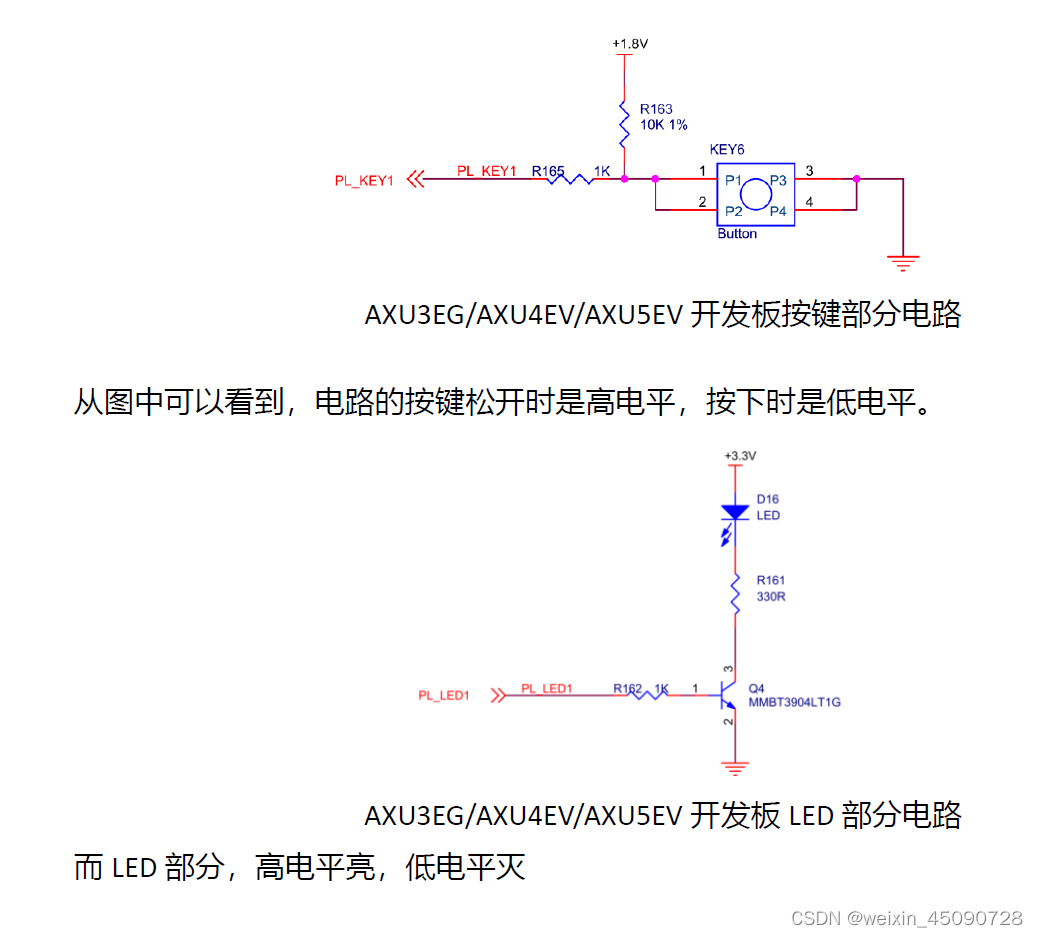

PL通过按键的开关状态控制led的亮灭,按键按下的时候灯亮,按键未按下的时候灯灭。

PL_LED1为高的时候,三极管处于导通状态,灯亮。

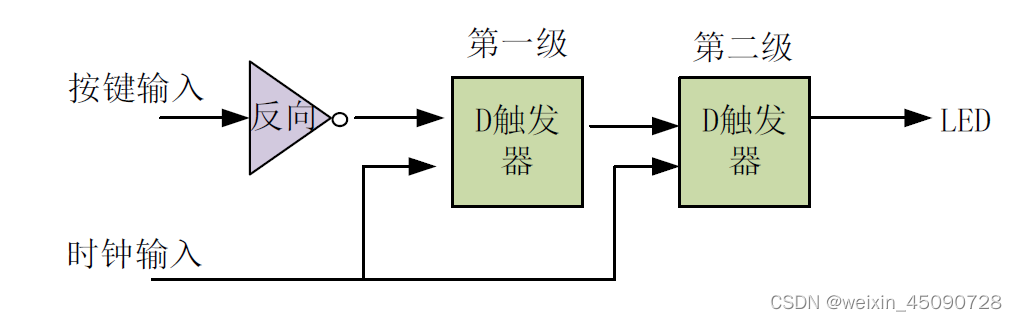

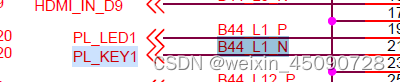

由于按键按下时是低电平,需要取个反将其送给led灯,所以硬件设计如下图:

实验步骤

- 确定硬件设计,管脚对应关系

- 用verilog实现实验原理硬件的设计

- 添加管脚和时序约束

- 本地仿真查看按键输入和输出的关系

- 板上验证是否和预期一致

实验记录

- 确认硬件关系

| 管脚 | 硬件 |

|---|---|

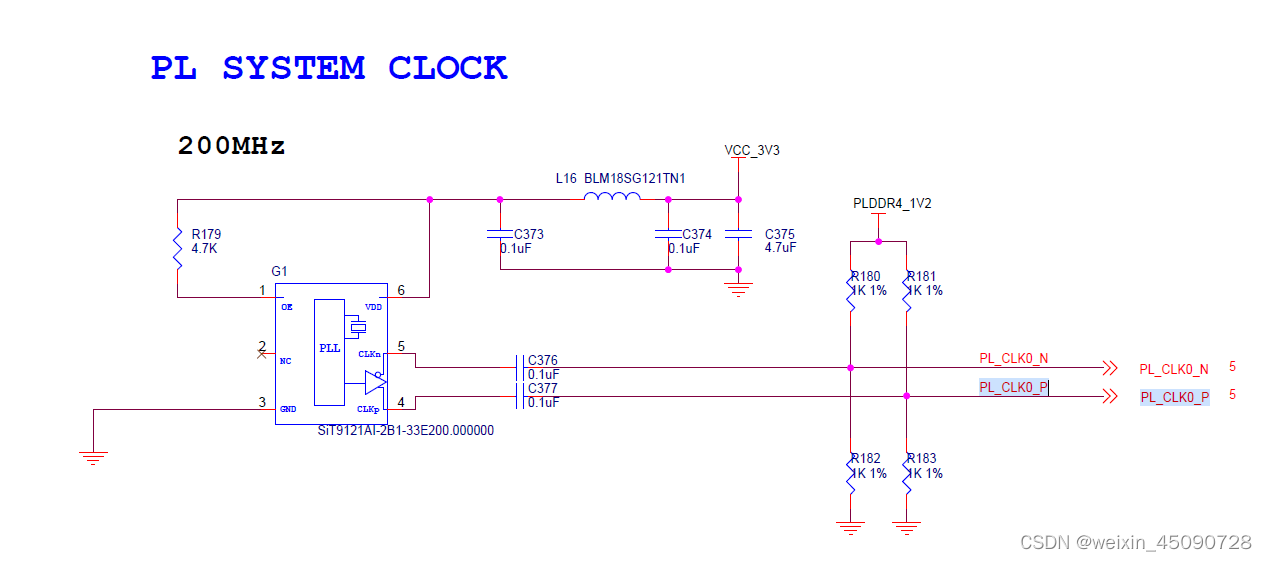

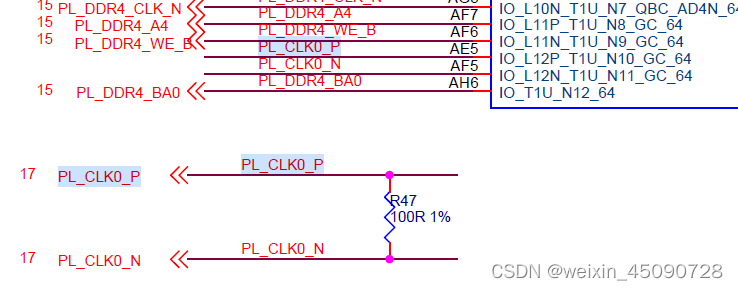

| 时钟 |   |

| 按键 |   |

| LED | 见按键 |

- verilog实现硬件设计

`timescale 1ns / 1ps

module key_test(

input sys_clk_p,

input sys_clk_n,

input key,

output led

);

reg led_r;

reg led_r1;

IBUFDS IBUFDS_inst(

.O(clk),

.I(sys_clk_p),

.IB(sys_clk_n)

);

always@(posedge clk)

begin

led_r <= ~key;

end

always@(posedge clk)

begin

led_r1 <= led_r;

end

assign led = led_r1;

endmodule

-

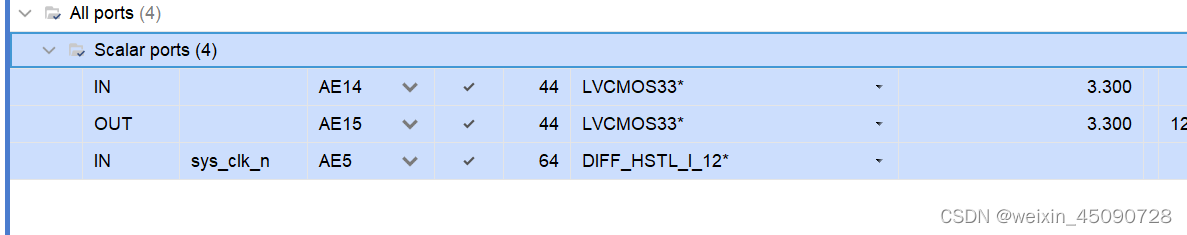

添加管脚约束和时序约束,均使用图像界面进行添加

管脚约束先点击“Open Elaborated Design”中,再在菜单中选择“Window --> I/O Ports”,进行管脚设置,设置完成后选择保存。

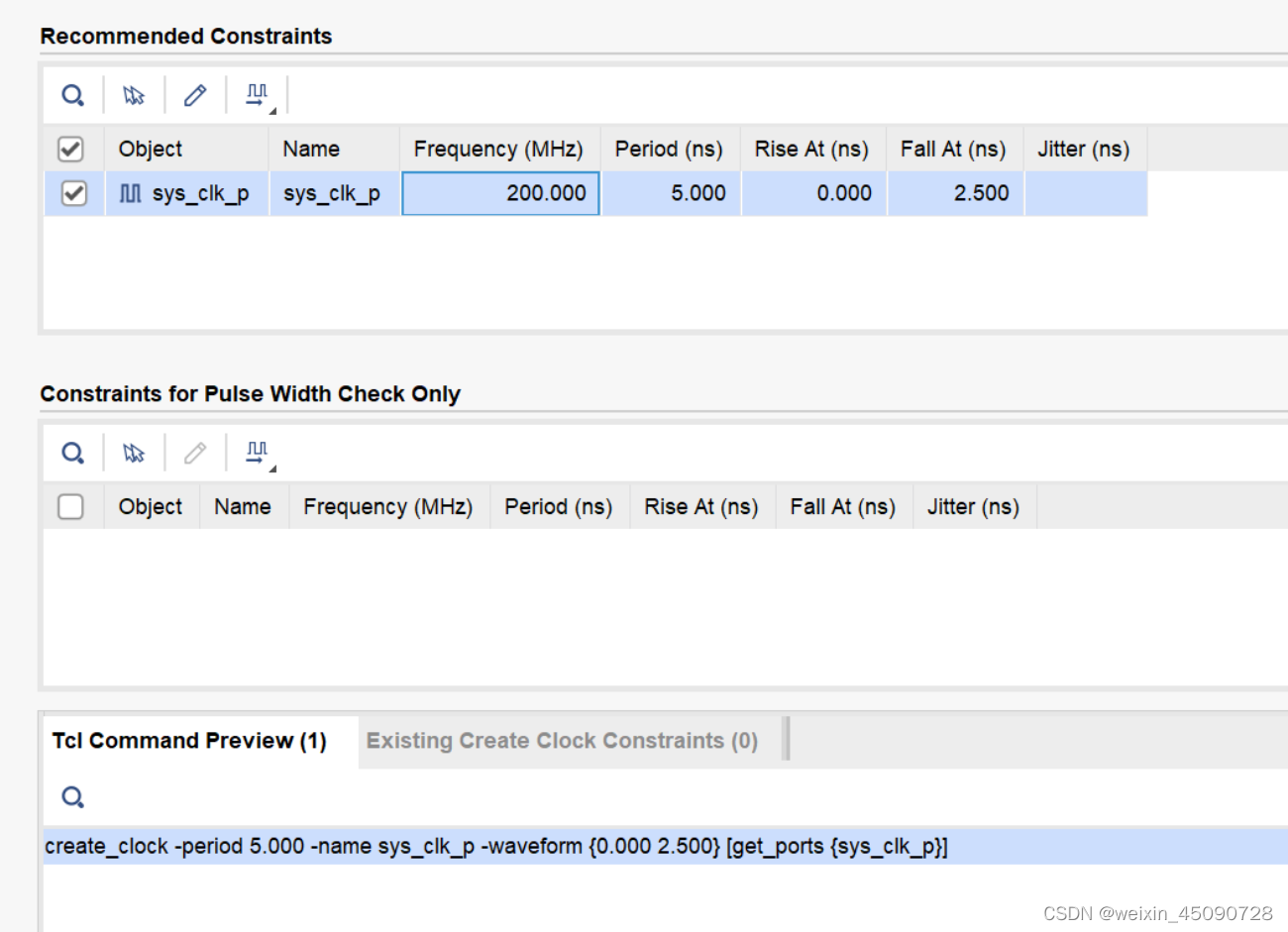

时序约束需要先综合“synthesis”,点击约束向导“Constraint s Wizard”,设置相关约束即可,这里只需要设置时钟。

-

在线仿真

编写test_bench,这里直接用资料里的代码。

`timescale 1ns/1ns

module key_test_tb;

reg sys_clk_p;

wire sys_clk_n;

reg[3:0] key;

wire[3:0] led;

initial

begin

sys_clk_p = 1'b0;

key = 4'b1111;

#12 key = 4'b0101;

#25 key = 4'b1010;

#8 key[0] = 1'b1;

#16 key[0] = 1'b0;

#100

$stop;

end

always #2.5 sys_clk_p = ~ sys_clk_p; //5ns涓�涓懆鏈燂紝浜х敓200MHz鏃堕挓婧�

assign sys_clk_n = ~ sys_clk_p;

key_test dut

(

.sys_clk_p(sys_clk_p),

.sys_clk_n(sys_clk_n),

.key (key), //4浣嶆寜閿緭鍏ワ紝鎸変笅鏄�0锛屽脊璧锋槸1

.led (led) //4浣峀ED鏄剧ず锛�0涓轰寒锛�1涓虹伃

);

endmodule

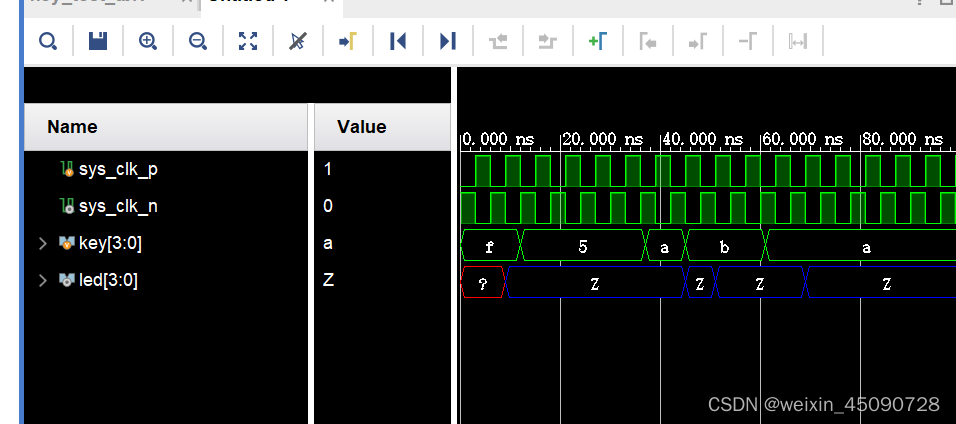

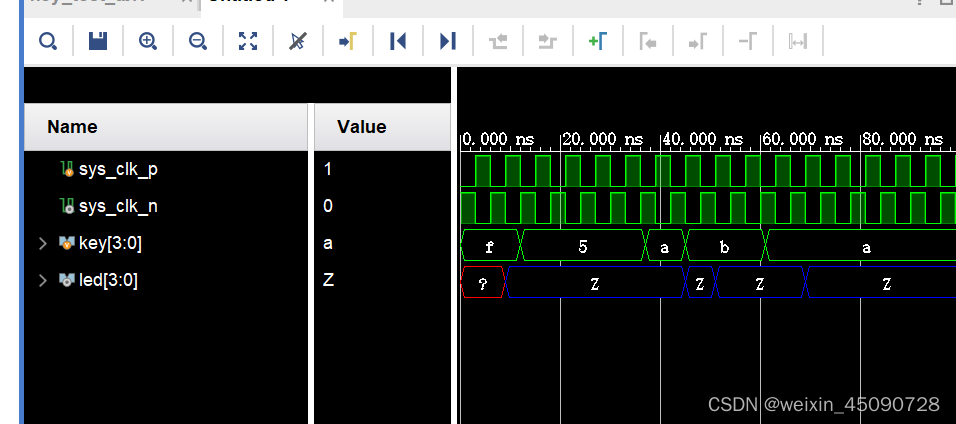

仿真结果:

- 板上验证

加载完bit后灯是亮的,按键按下灯会灭,松开按键灯会亮。

实验总结

本实验先进行硬件设计,再使用verilog语言完成所描述的硬件设置,实现了接收按键输入控制LED亮灭的功能(或者说设计了一个简单的硬件单元)。

实验问题及解决

- 生成bit失败,原因是一个管脚忘记约束

报错信息

[DRC UCIO-1] Unconstrained Logical Port: 2 out of 4 logical ports have no user assigned specific location constraint (LOC). This may cause I/O contention or incompatibility with the board power or connectivity affecting performance, signal integrity or in extreme cases cause damage to the device or the components to which it is connected. To correct this violation, specify all pin locations. This design will fail to generate a bitstream unless all logical ports have a user specified site LOC constraint defined. To allow bitstream creation with unspecified pin locations (not recommended), use this command: set_property SEVERITY {Warning} [get_drc_checks UCIO-1]. NOTE: When using the Vivado Runs infrastructure (e.g. launch_runs Tcl command), add this command to a .tcl file and add that file as a pre-hook for write_bitstream step for the implementation run. Problem ports: sys_clk_n, and sys_clk_p.

大概意思是有管脚没有进行约束,最后检查发现时钟输入管脚未绑定,重新设置后可以正常生成bit。

2. (未解决)仿真led输出一直是个Z,和预期不符暂时未找到原因

另外仿真点击restart后vivado会重启。

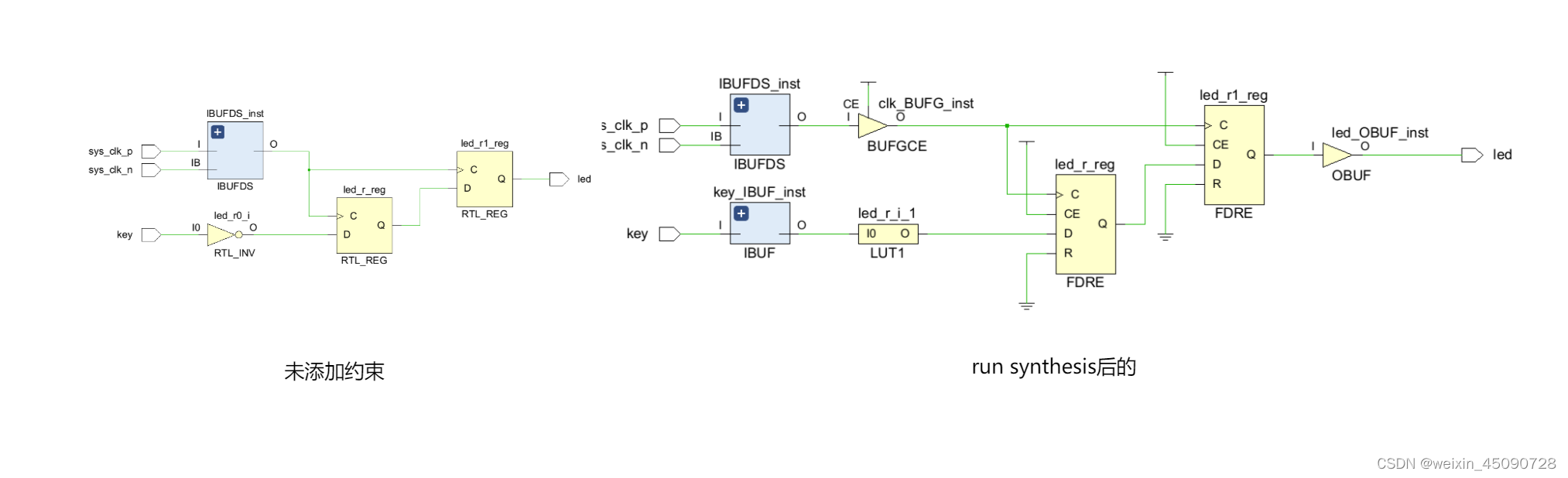

3. (未解决)查看RTL图,发现综合后会发生变化,含义还有些不清楚

4. 上板验证发现按键按下时灯才不亮。

该文介绍了使用Vivado进行按键控制LED亮灭的实验,通过Verilog编程实现硬件逻辑,包括按键的低电平检测、反相器设计以及添加管脚和时序约束。实验中遇到了生成bit文件失败、仿真LED输出为Z和综合后RTL图变化等问题,部分问题已解决。

该文介绍了使用Vivado进行按键控制LED亮灭的实验,通过Verilog编程实现硬件逻辑,包括按键的低电平检测、反相器设计以及添加管脚和时序约束。实验中遇到了生成bit文件失败、仿真LED输出为Z和综合后RTL图变化等问题,部分问题已解决。

1793

1793

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?