A.8 宏定义

`define 定义全局参数

`define DATA_WIDTH 8

module

reg[`DATA_WIDTH-1:0] data; //这相当于定义 reg[7:0] data;

...

endmodule

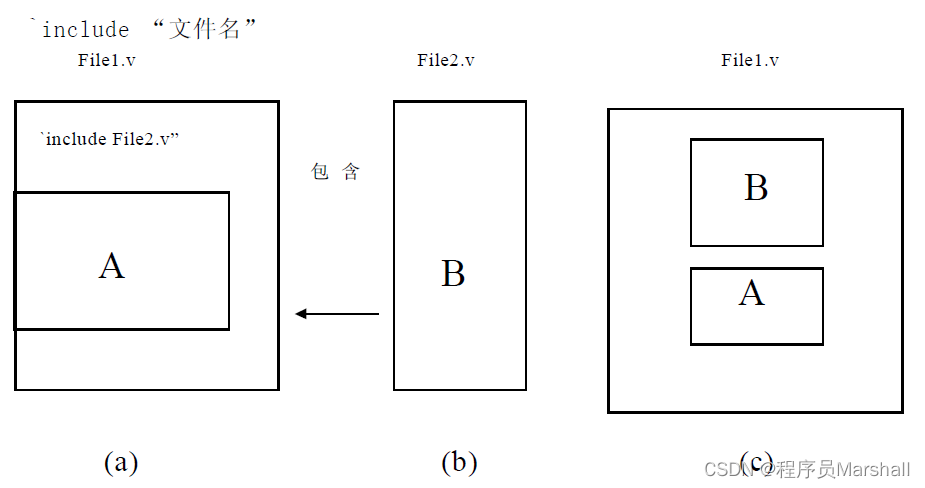

`include 文件包含

示例:

//文件aaa.v

module aaa(a,b,out);

input a, b;

output out;

wire out;

assign out = a^b;

endmodule

//文件 bbb.v

`include "aaa.v"

module bbb(c,d,e,out);

input c,d,e;

output out;

wire out_a;

wire out;

aaa aaa(.a(c),.b(d),.out(out_a));

assign out=e&out_a;

endmodule

`timescale 定义仿真时间单位和精度

上一节课我们讲到过

`timescale 10ns/1ns

这里置了时间单位是10ns,时间精度是1ns&

本文介绍了Verilog中的宏定义,包括`define用于定义全局参数,`include用于文件包含,`timescale用于设置仿真时间单位和精度,以及`ifdef进行条件编译,帮助在FPGA开发中实现灵活的代码组织和编译选择。

本文介绍了Verilog中的宏定义,包括`define用于定义全局参数,`include用于文件包含,`timescale用于设置仿真时间单位和精度,以及`ifdef进行条件编译,帮助在FPGA开发中实现灵活的代码组织和编译选择。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1238

1238

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?