在可测性设计(DFT)技术中,扫描测试(scan)技术可以说是最重要的一部分,其目的在于增强电路的可控制性和可观测性。

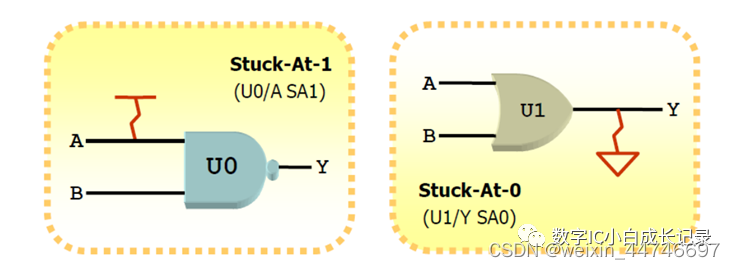

在介绍扫描测试技术之前,首先要介绍一下缺陷和故障模型。我们知道DFT技术就是为了检测芯片生产制造过程中的缺陷的,CMOS工艺中常见的制造缺陷就是对电源或地的短路。制造缺陷会引发故障,如果芯片内部一个器件的引脚和电源短路了,那么这个引脚的电平就始终被强制拉高了,在数字电路中就是始终表现为逻辑1,此种故障称为固定为1的故障(stuck-at 1);同理,如果芯片内部一个器件的引脚和地短路了,那么这个引脚的电平就始终被强制拉低了,在数字电路中就是始终表现为逻辑0,此种故障称为固定为0的故障(stuck-at 0)。上述两种故障统称固定型故障模型(stuck-at fault model),也是最常见的故障模型。

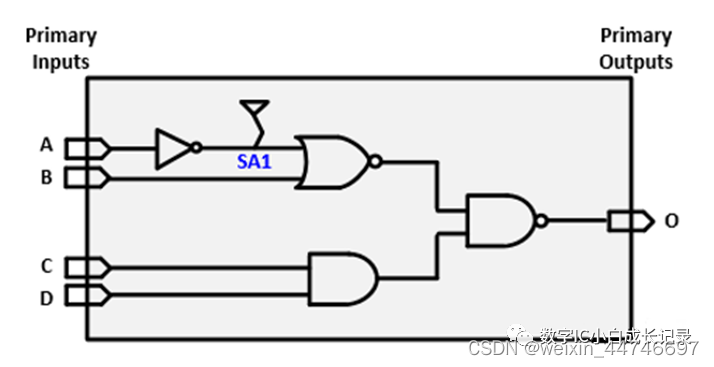

现在假设在下图中SA1所示位置发生了固定为1的故障,或非门的一个输入引脚与VDD短接,导致其始终为1,那么我们该如何进行测试呢?

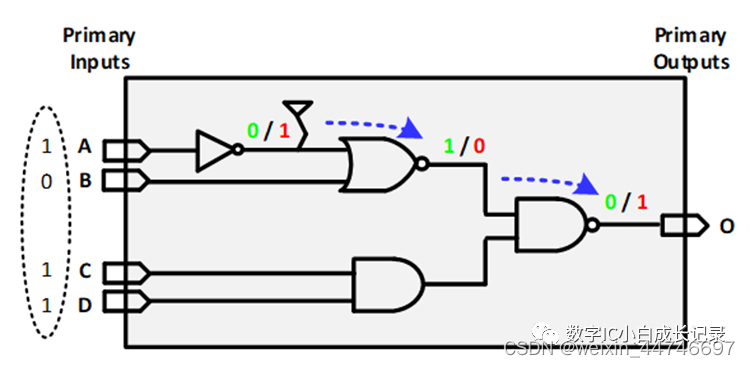

首先需要在故障点产生与之相反的值,也就是故障激活,因此需要A端口的输入为1,这样才能使故障点的值为0。接下来需要使故障点的值能够顺利传到输出端口O,也就是路径敏化,此时需要B、C、D都是特定的值才可以将故障点的值顺利传出。如下图所示,绿色数字表示芯片制造无缺陷时各节点的逻辑值,红色数字表示存在上述的固定为1的故障时各节点的逻辑值,因此当输入端口ABCD的值依次为“1011”时,输出端口O处检测到的值为1表示芯片制造存在缺陷。

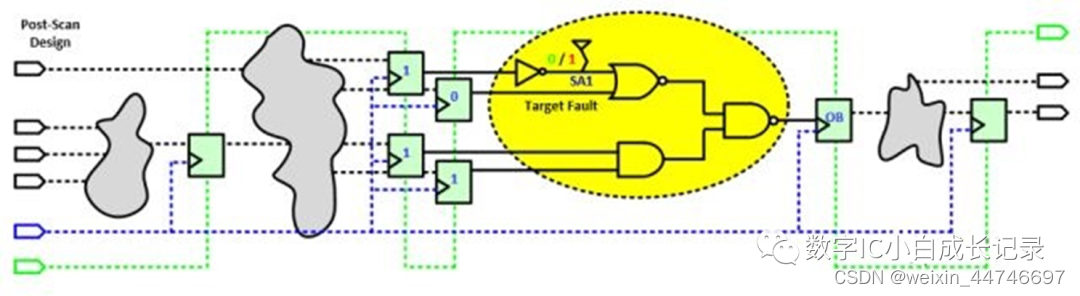

但在实际芯片中,上述的逻辑电路只是很小的一部分(如下图黄色区域所示),此时ABCD四个端口没有直接和外部相连,我们也就不能随意地控制这四个端口的输入值。同样,输出端口O也没有直接和外部相连,我们也不能方便地观测到端口O的输出值。没有良好的可控制性和可观测性,给黄色区域的测试带来极大的不便。

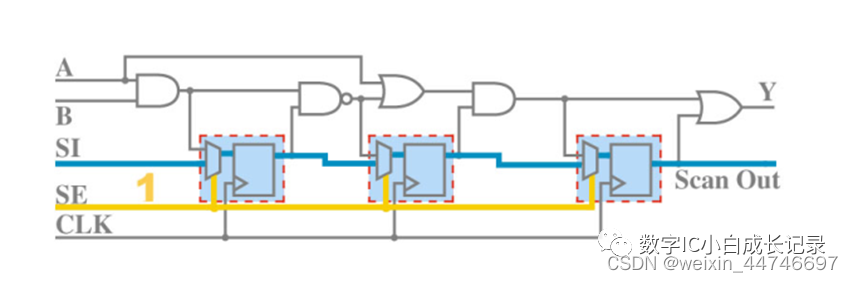

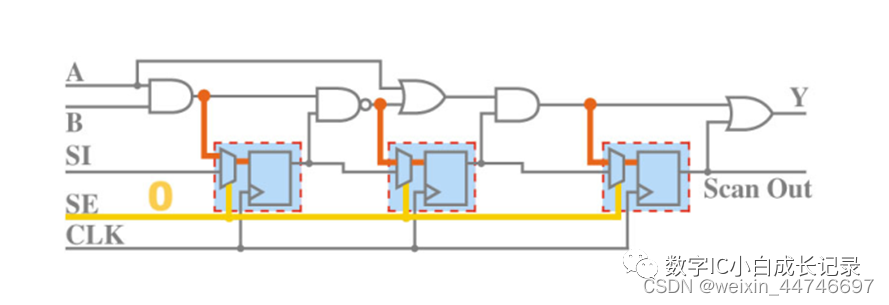

这时候就要用到扫描测试技术了,图中绿线部分就是一条扫描链(scan chain),可以简单的理解为一组移位寄存器,通过控制移位可以将需要的测试数据“1011”移位到对应的端口,同时还可以将O端口的值移除进行观测。达到了良好的可控制性和可观测性。

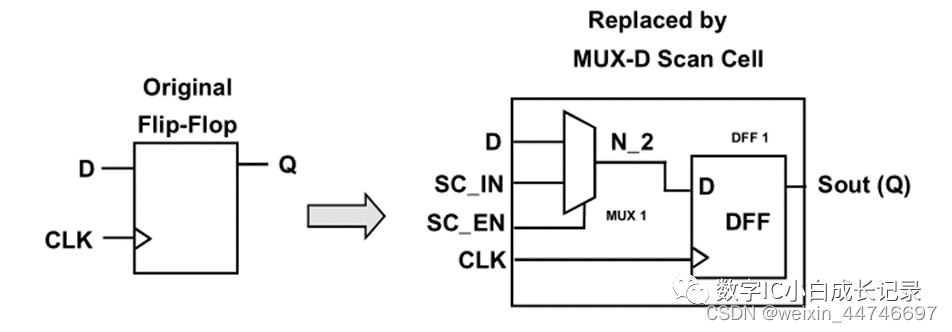

scan chain是由一个个的scan cell首尾相接串起来的,scan cell和普通的DFF不同,相当于在原有的基础上多增加了一个MUX。当SC_EN(scan_enable)使能时,数据由SC_IN(scan_in)端进入,此时进入扫描测试模式;当SC_EN(scan_enable)不使能时,数据由D端进入,和原有功能一致。

也就是说,扫描测试技术在不影响电路原有功能的情况下,通过scan chain实现了对电路良好的可控制性和可观测性,为测试带来了极大的便利。

欢迎大家关注微信公众号:数字IC小白成长记录~

1733

1733

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?