现代集成电路的制造工艺越来越先进,但是在生产过程中的制造缺陷也越来越难以控制,甚至一颗小小的 PM2.5 就可能导致芯片报废,为了能有效的检测出生产中出现的废片,需要用到扫描链测试(scan chain),由此产生了可测性设计即 DFT flow。

注意scan test 只能检测出制造瑕疵,无法检测芯片功能瑕疵。

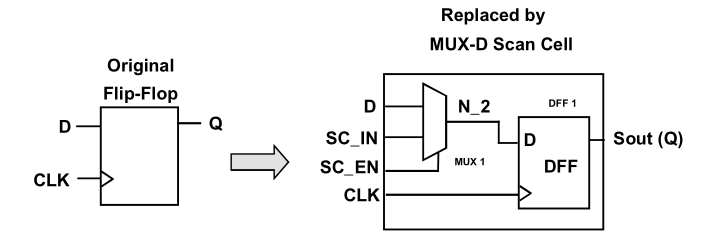

DFT 第一步是做 scan chain,首先将电路中的普通 DFF 换成 scan DFF:

scan DFF 是在原DFF 的输入端增加了一个 MUX,于是多了几个 pin :scan_in,scan_enable,scan_out

换完之后将所有的 scan DFF 首尾依次串接起来,就构成了一条 scan chain :

文章介绍了集成电路的可测性设计DFT中的扫描链(scan chain)概念,阐述了如何通过scan chain检测制造缺陷,以及scan chain的工作流程,包括load、capture和unload步骤,用于判断电路是否正常工作。

文章介绍了集成电路的可测性设计DFT中的扫描链(scan chain)概念,阐述了如何通过scan chain检测制造缺陷,以及scan chain的工作流程,包括load、capture和unload步骤,用于判断电路是否正常工作。

最低0.47元/天 解锁文章

最低0.47元/天 解锁文章

1666

1666

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?