0、经验

1、即使通过的是同一个LUT6,或者是LUT4,延迟都不会一样。

2、

1、学习进度

04:如何科学设计FPGA:时序约束基础,了解时序分析模型_哔哩哔哩_bilibili 21:14s

需要归纳一下,建立时间和保持时间的计算。

2、相关资料

参考视频

基础篇:

05如何科学设计FPGA:VIVADO中的时序约束和分析以及进阶技巧_哔哩哔哩_bilibili

升级篇:

05如何科学设计FPGA:VIVADO中的时序约束和分析以及进阶技巧_哔哩哔哩_bilibili

参考文章

菜鸟教程的:

csdn写的很好的文章目录:

《时序分析、时序约束和时序收敛》专栏的说明与导航_fpga时序约束与分析目录-优快云博客

第一章:

时序分析、时序约束和时序收敛(1)--时序分析、时序约束和时序收敛分别都是什么?-优快云博客

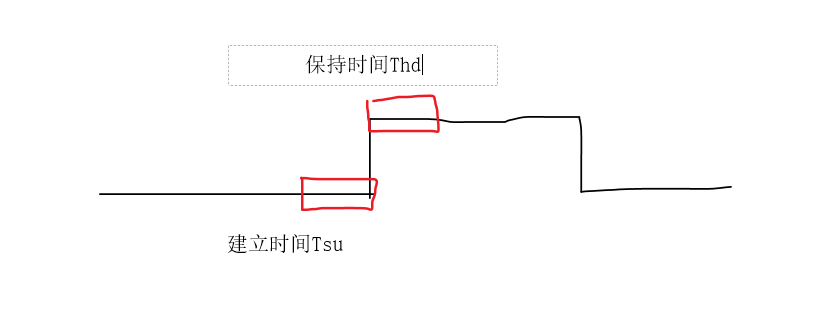

3、D触发器的建立时间

建立时间(setup time)和保持时间(hold time):

建立时间就是时钟触发事件来临之前,数据需要保持稳定的最小时间,以便数据能够被时钟正确的采样。

保持时间就是时钟触发事件来临之后,数据需要保持稳定的最小时间,以便数据能够被电路准确的传输。

slack,松弛的,在这里是是余量的意思。

Tslack=要求到达的时间-实际到达的时间

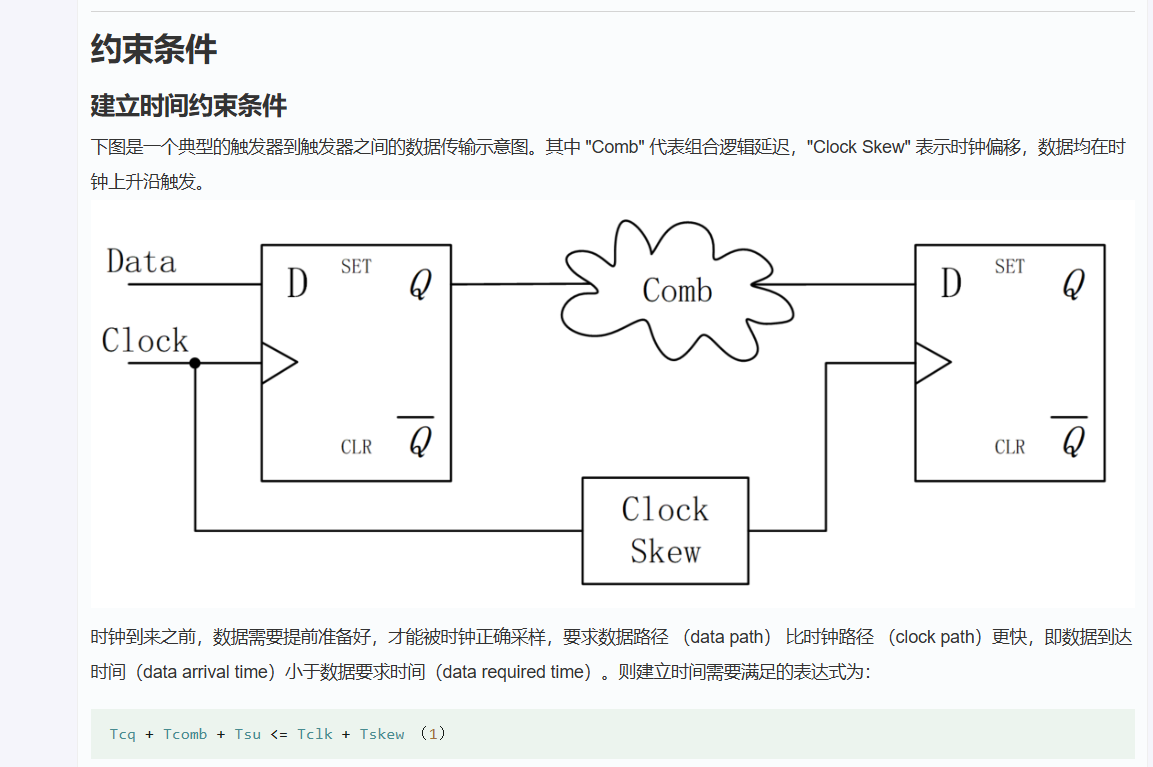

菜鸟教程这一段写的很好,得到公式如下

Tcq + Tcomb + Tsu <= Tclk + Tskew (1)

如果使用Tslack来做表达,那么就是

Tslack + Tcq + Tcomb + Tsu = Tclk + Tskew

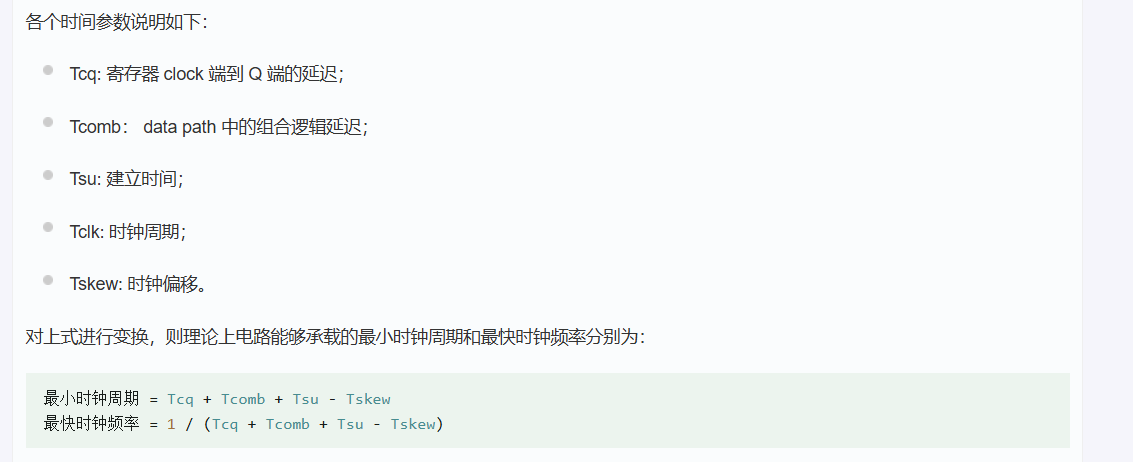

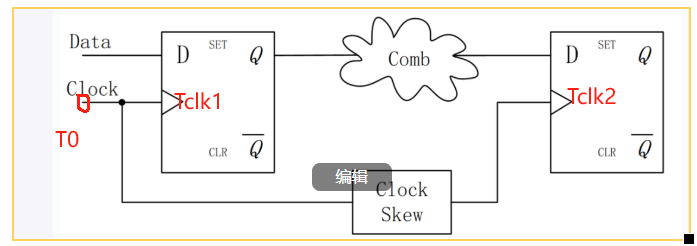

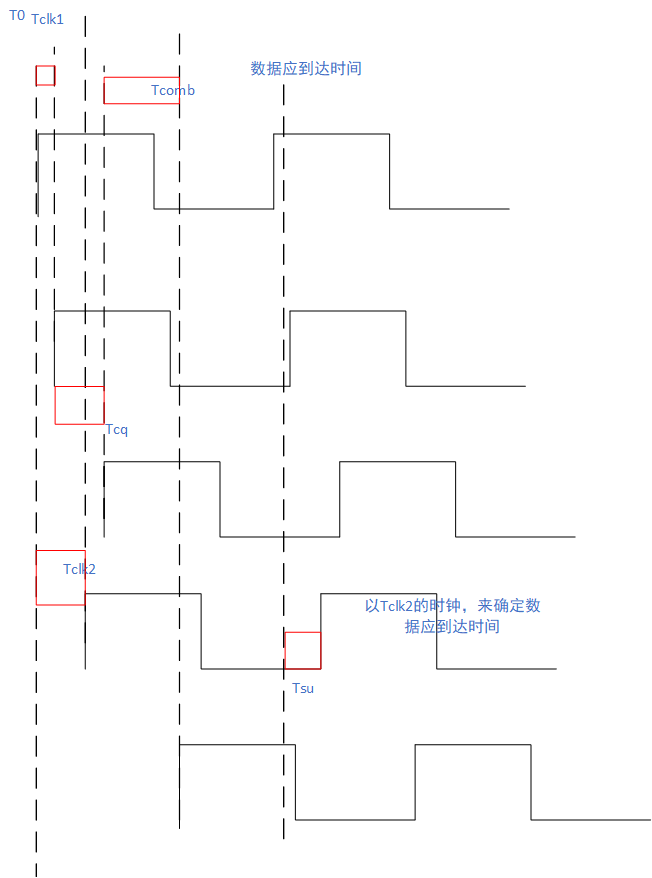

更基础推导

详见视频:04:如何科学设计FPGA:时序约束基础,了解时序分析模型_哔哩哔哩_bilibili

如果这个还是不太好理解,可以从基础一点去推导这个公式:

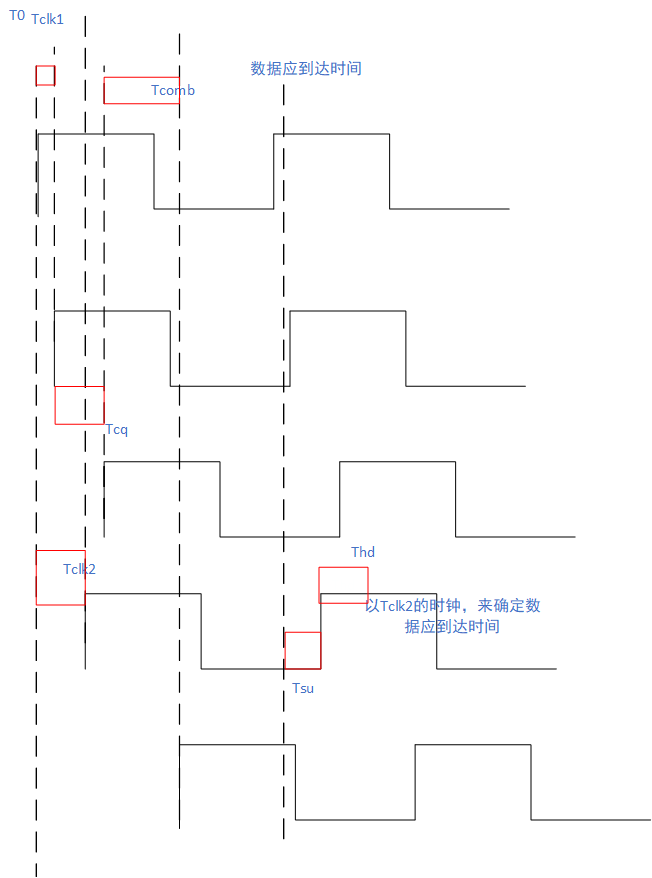

数据到达时间=Tclk1+Tcq+Tcomb

数据要求时间=Tclk2+Tclk-Tsu

又因为数据到达时间<= 数据要求时间

Tclk1+Tcq+Tcomb <= Tclk2+Tclk-Tsu

推得Tcq+Tcomb +Tsu<= Tclk2+Tclk-Tclk1

有因为时钟偏移Tskew=Tclk2- Tclk1

最后得到公式 Tcq+Tcomb +Tsu <=Tclk + Tskew

Tclk 是时钟周期。

强行理解这个公式就是:

寄存器Tcq+组合逻辑延迟Tcomb+建立时间Tsu 要在一个时钟周期内完成,由于有时钟偏移,就是要在一个时钟周期+时钟偏移内完成。

4、D触发器的保持时间

保持时间余量Tslack,保持时间应满足:

数据到达时间 >= 要求到达时间

Tclk1 + Tcq + Tcomb + T >= Tclk2 + T + Thd

推得 Tcq + Tcomb >= Tskew + Thd

强行理解就是,因为时钟周期大T消掉了,数据路径上的Tcq和组合逻辑延迟Tcomb 应该大于 时钟周期相关的Tskew和Thd,这样数据才能维持到保持时间之后。

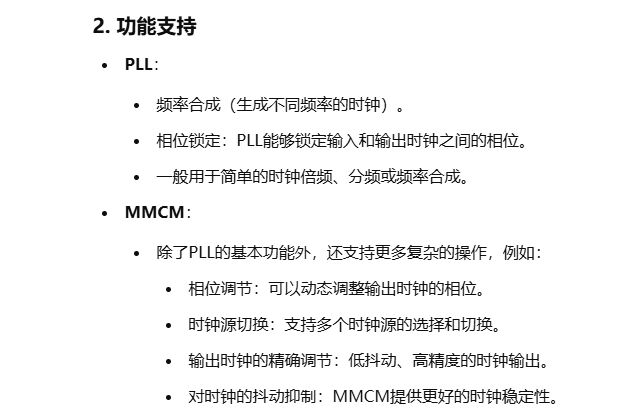

5、同步时钟和异步时钟

是同一个时钟的倍频或者别的关系,或者说是一个MMCM一个PLL出来的,一个源头的,都是同步时钟。

否则为异步时钟。

我看到评论区有个说法我觉得是对的,同步时钟就是知道其中的一个时钟什么时候上升沿,我就能知道另一个什么时候上升沿,这样就能做时序分析。异步时钟,哪怕两个时钟的频率和相位都相等,你也不知道它什么时候上升沿。

UP主说,MMCM(Mixed-Mode Clock Manager)和PLL(Phase-Locked Loop)都是时钟管理单元,MMCM的调频能力强,PLL的调相能力强。

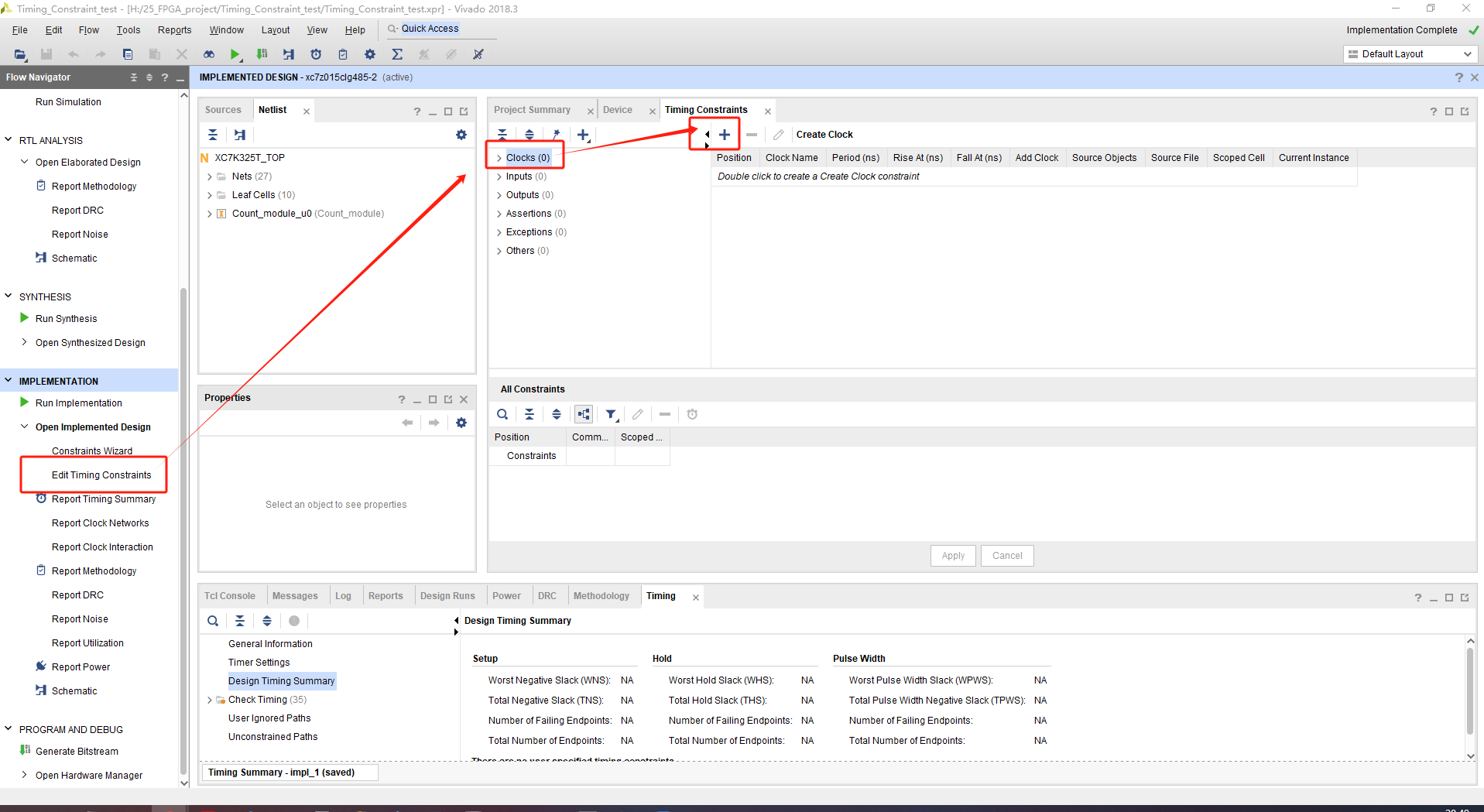

6、vivado时序进入时序约束界面

理论

1、vivado中,默认所有的时钟都是有关系的,都做时钟约束

2、如果有异步时钟,需要进行异步时钟约束,

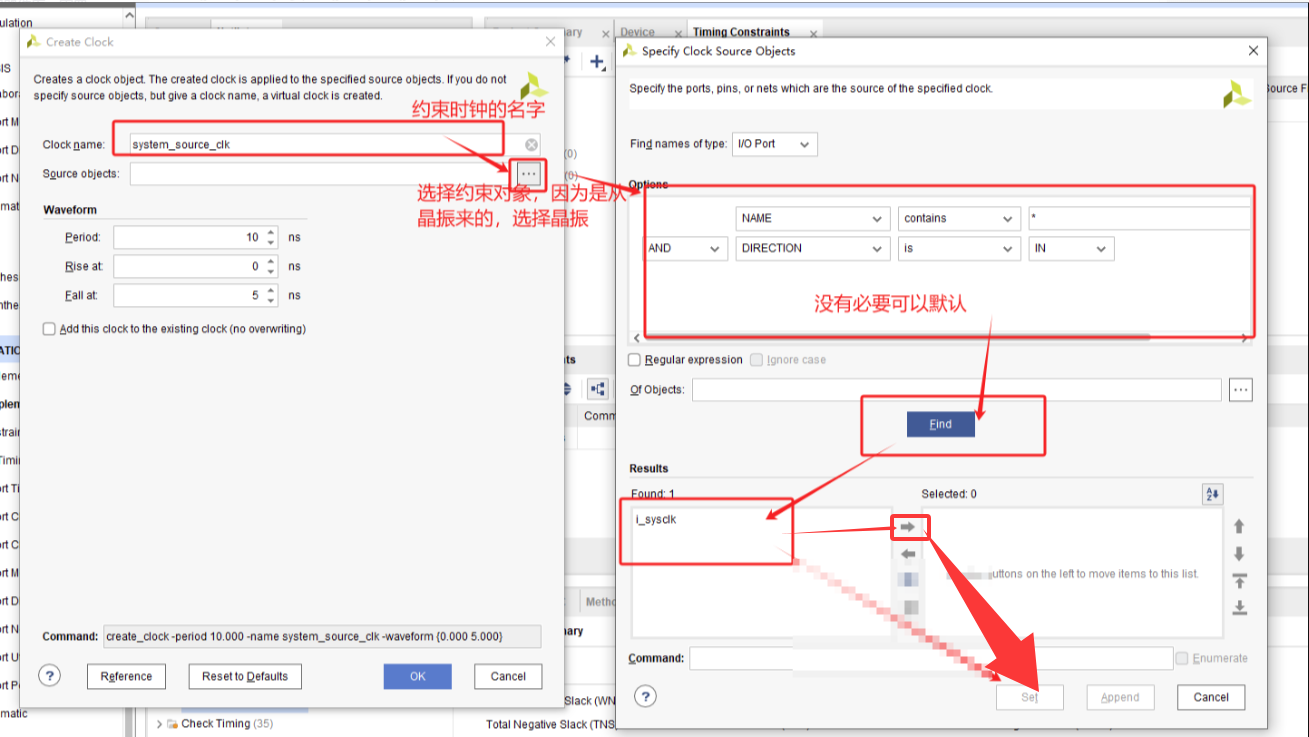

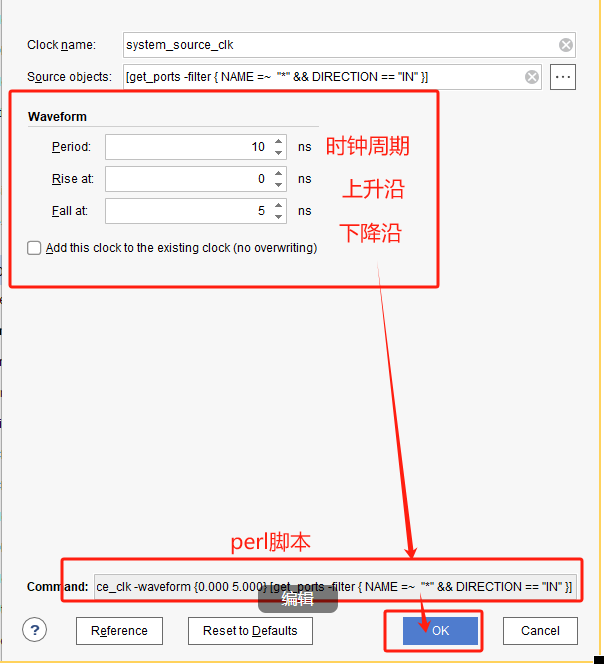

设置源时钟

建立源时钟

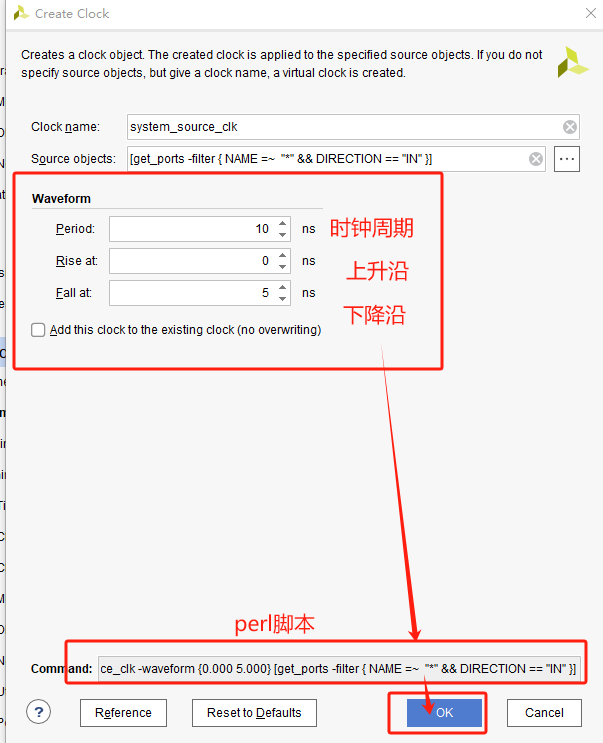

输入时钟的参数

输入时钟的参数

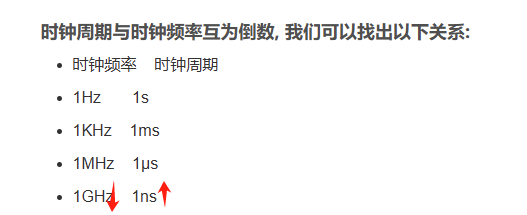

时钟周期

时钟周期和频率互为反比,一个增加,一个就减少,1Ghz对应1ns,那么时钟周期增加10倍,变成10ns,时钟频率就会减少10倍,变成0.1Ghz。

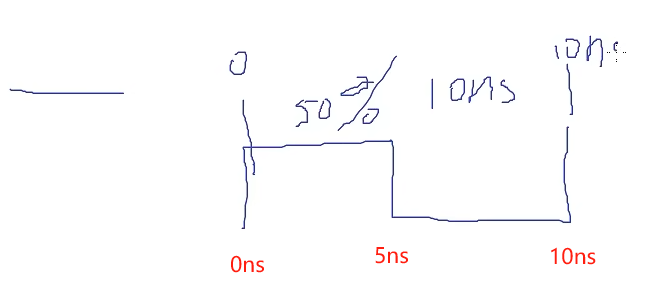

上升沿和下降沿

一般按照占空比50%。

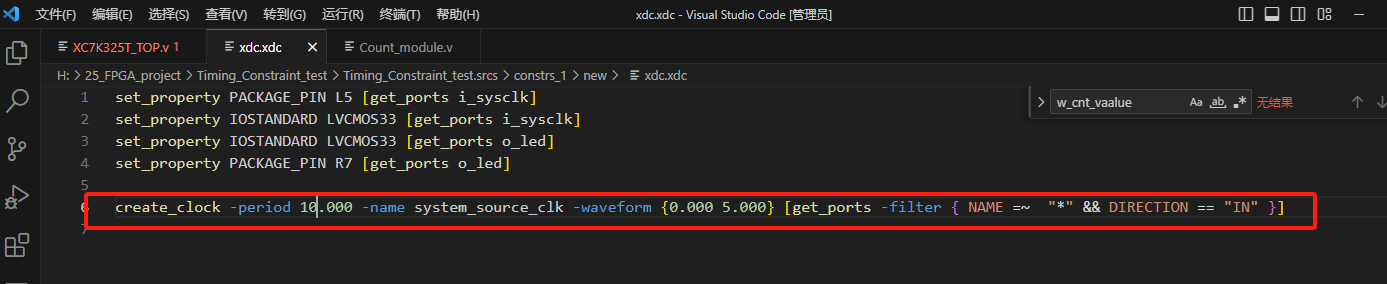

然后下图点击OK后,摁住ctrl+s保存即可。

随后会生成约束文件,如果要修改约束的时钟频率,修改约束文件里面的tcl脚本即可。

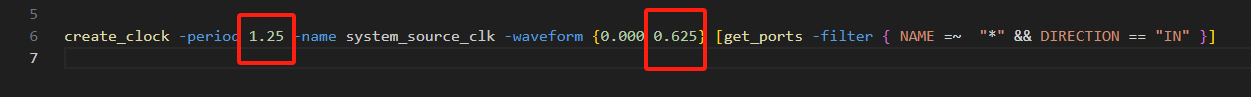

如果我想修改时钟周期为800Mhz,只需要按照下图进行操作,要修改时钟频率,要改变时钟的下降沿。

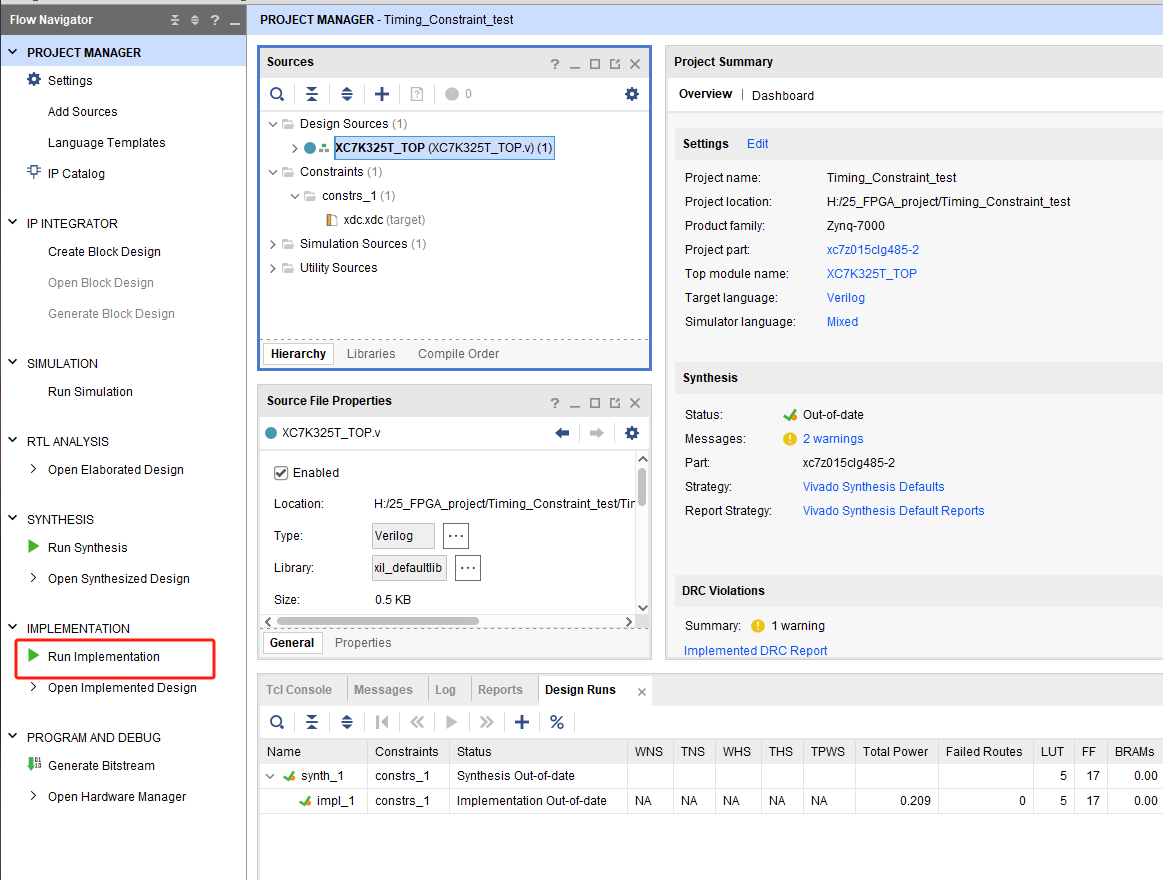

重新布局布线

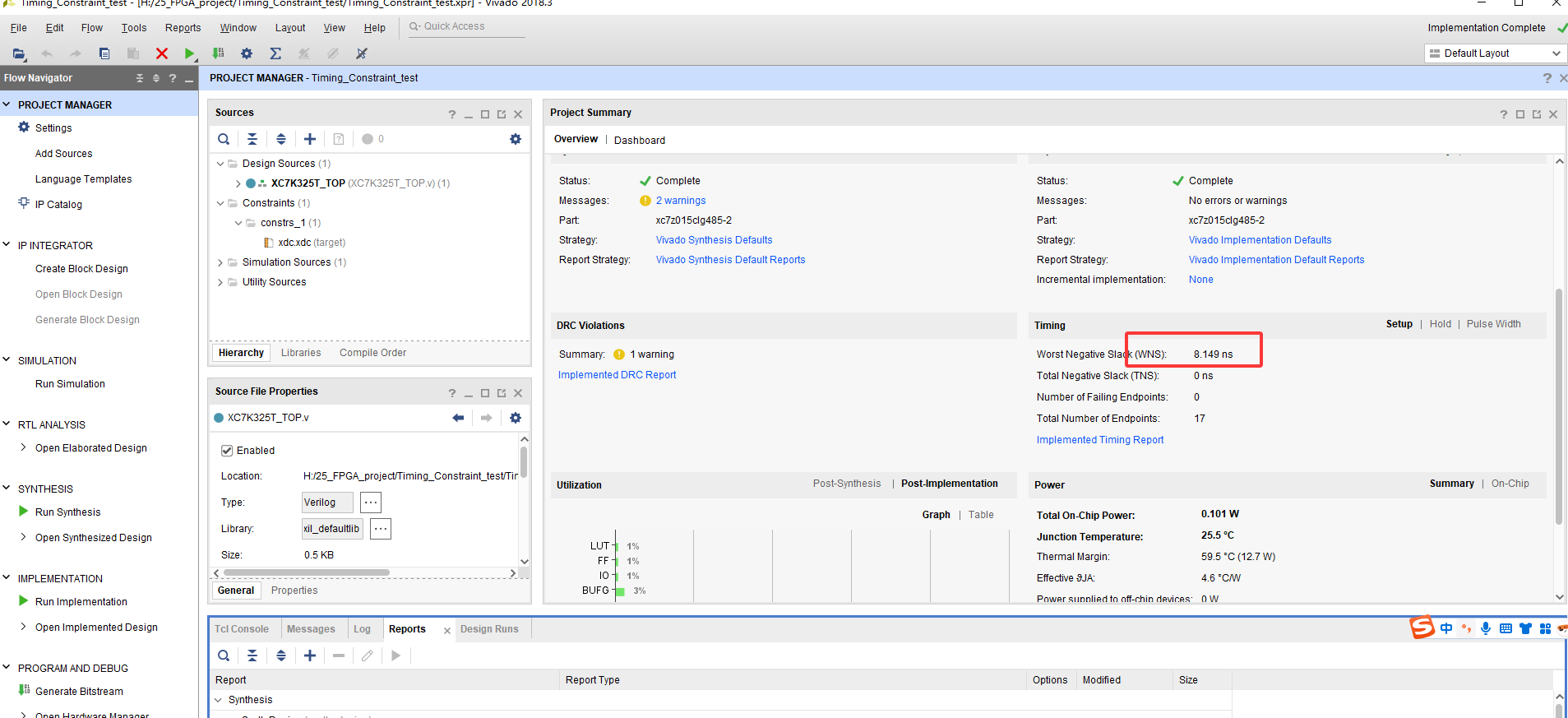

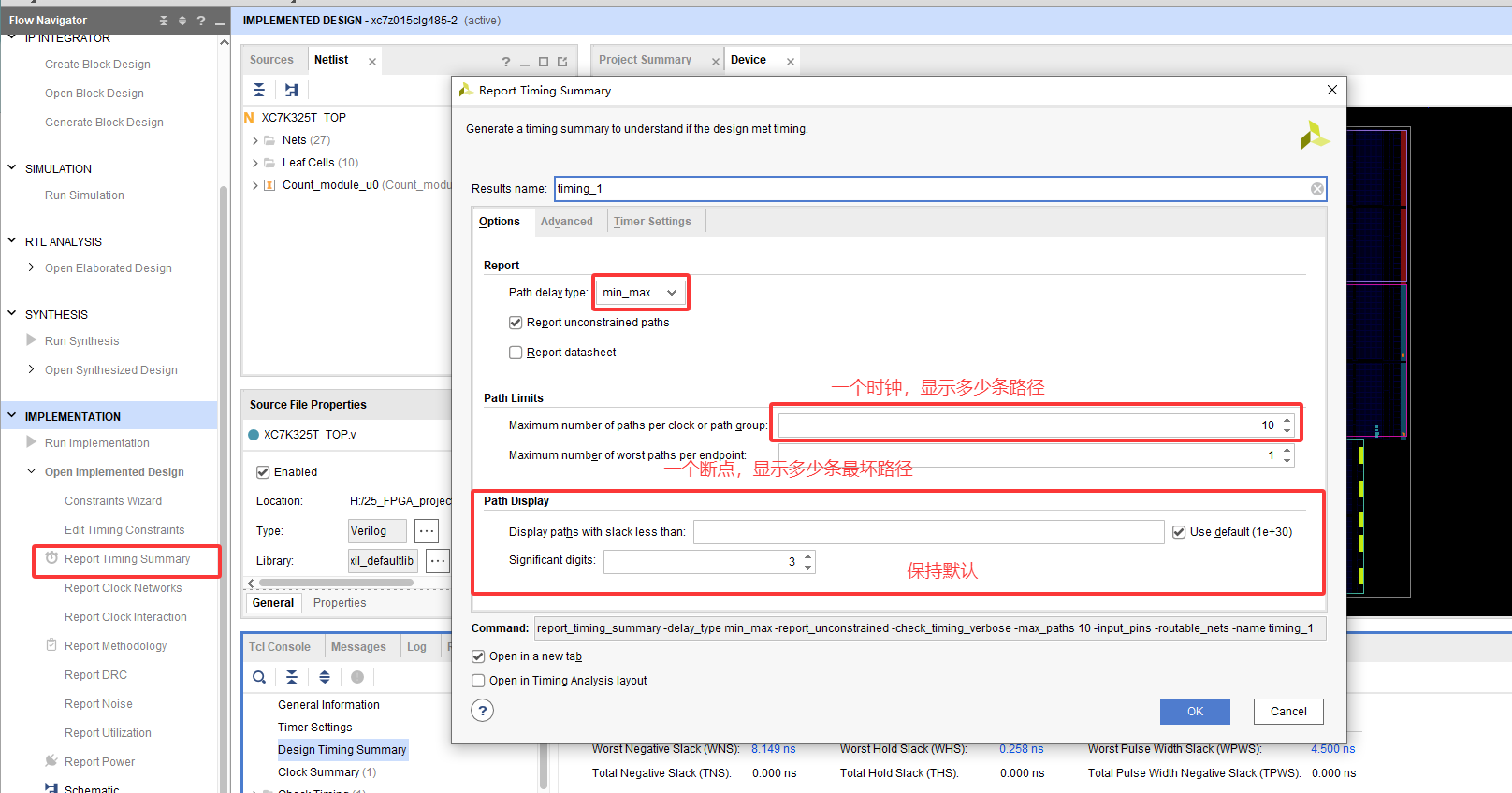

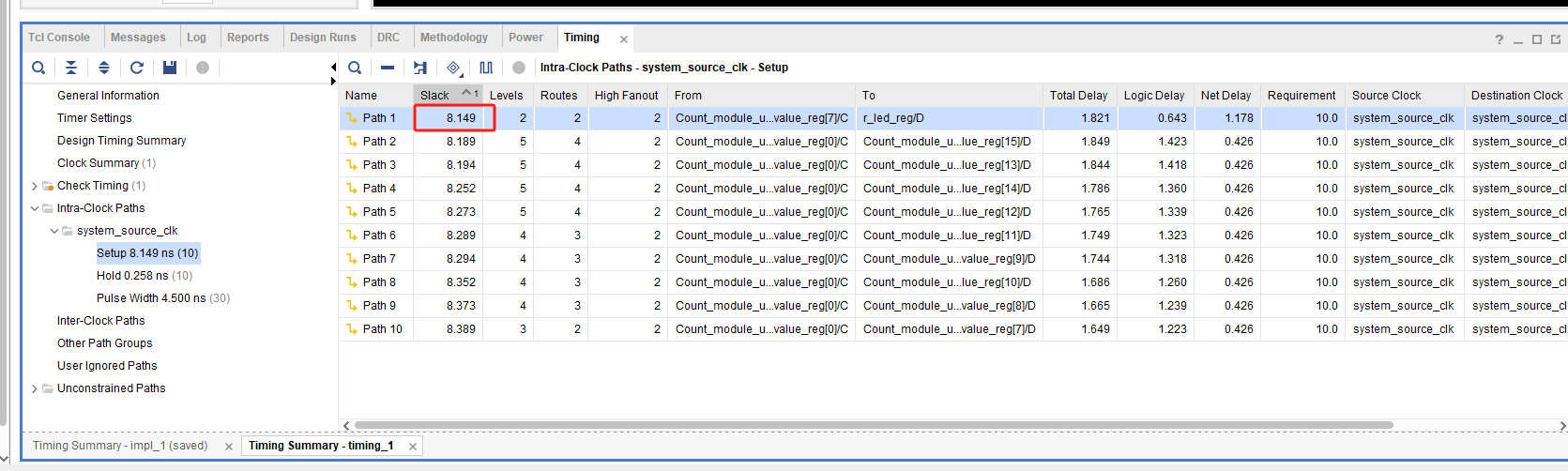

查看建立时间余量

最小min是分析建立时间,最大max是分析保持时间。min_max默认两个都分析。其余项保持默认,然后点击OK即可。

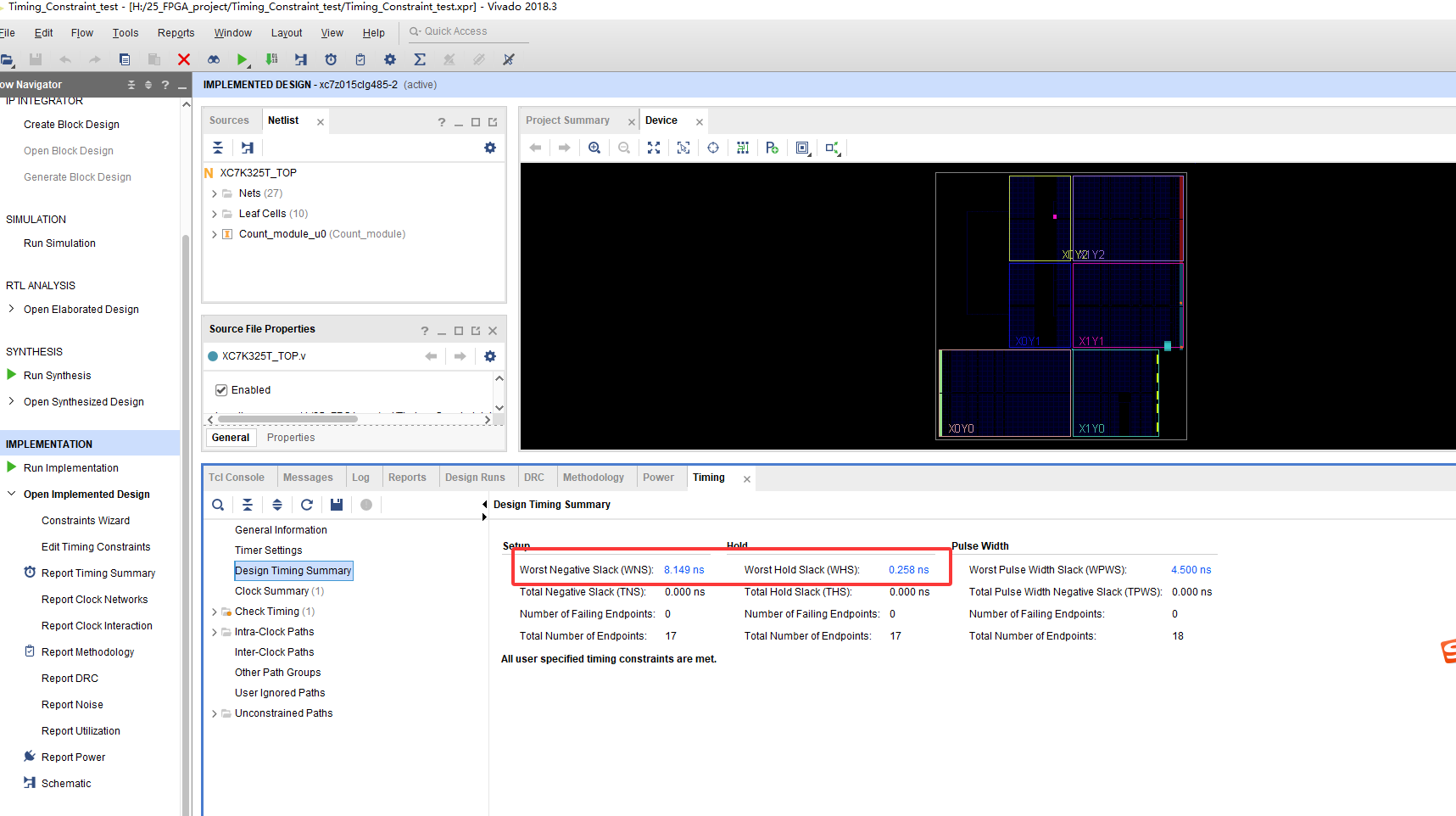

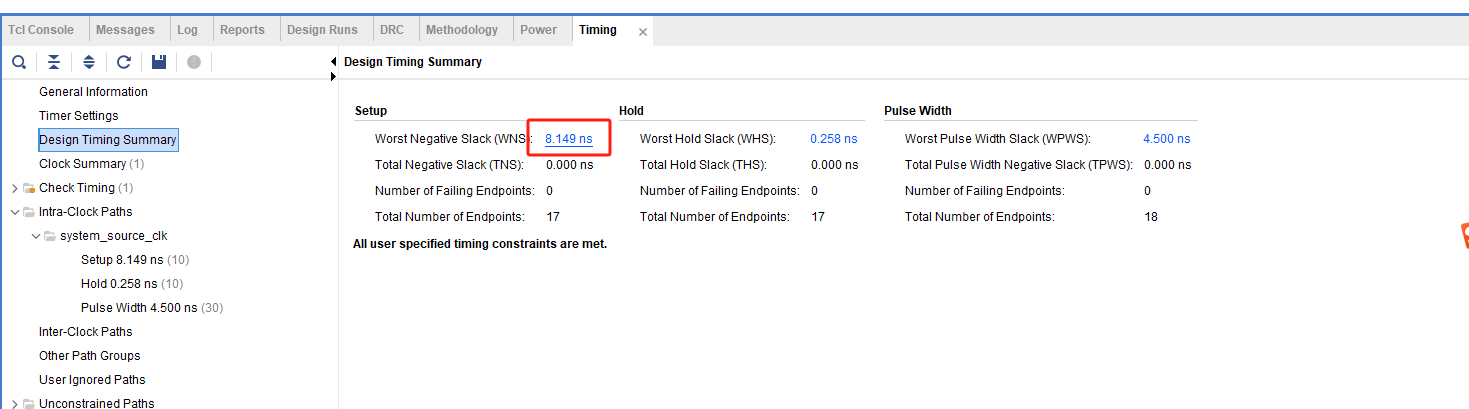

一般图中两项都是正数即可,说明都是满足情况的

点击即可查看最坏的时序,也就是建立时间余量最少的情况。

参数的解释

1. Name (路径名称):

-

解释:这列显示时序路径的名称,用于标识具体的时序路径。在设计中,每条路径都会有一个唯一的名称。

-

举例:

-

Path 1,Path 2等。 -

假设有一个时序路径是从寄存器

reg1到寄存器reg2,则可能命名为Path 1。这样便于开发人员或工具对时序进行分析和查看。

-

2. Slack (时序裕度):

-

解释:时序裕度是指路径的实际延迟与设计所要求的时序之间的差距。它表示时序是否满足要求。如果时序裕度为负,表示时序违例,即信号传输的时间超出了时钟周期。

-

举例:

-

假设某路径的实际延迟为 8.5ns,而要求的时序为 10ns,那么时序裕度为

10ns - 8.5ns = 1.5ns,此时时序满足,裕度为正。 -

如果实际延迟为 12ns,时序裕度为

10ns - 12ns = -2ns,这表示时序违例。

-

3. Levels (应该指的是逻辑门的级数):

-

解释:级别表示路径中涉及的寄存器或逻辑单元的层数。路径中级别越高,表示信号从源寄存器到目标寄存器的传播过程中经过了更多的逻辑门或触发器。

-

举例:

-

如果路径从寄存器

reg1直接连接到寄存器reg2,则该路径的级别为 2,因为有两个寄存器。 -

如果路径从

reg1到logic_gate1,再到reg2,则该路径的级别为 3,因为路径经过了一个逻辑门。

-

4. Routes (布线数量):

-

解释:该列显示信号从源到目的的布线数量,通常表示信号传播路径的复杂度。布线数量高通常意味着路径复杂,可能影响时序延迟。

-

举例:

-

假设路径

Path 1涉及两段布线连接reg1到reg2,则布线数量为 2。 -

如果路径经过多次逻辑单元,涉及多个布线段,则布线数量可能会增加,如布线数量为 5。

-

5. High Fanout (高扇出,应该是1个信号被分成了几个):

-

解释:表示一个信号源连接到多个接收端的情况。高扇出意味着一个信号源驱动多个寄存器或逻辑单元。扇出较高的路径可能会引起较大的时序延迟,因为信号需要传播到多个地方。

-

举例:

-

如果一个信号源

signal_A驱动了 3 个寄存器reg1、reg2和reg3,那么该路径的高扇出为 3。 -

如果信号源驱动了 5 个寄存器,则高扇出为 5。

-

6. From (路径来源):

-

解释:表示时序路径的起始点。通常是一个寄存器或逻辑单元,表示信号从哪里开始传播。

-

举例:

-

假设信号从寄存器

reg1开始传播,那么From列会显示reg1。 -

如果路径的起始点是组合逻辑门

logic_gate1,那么From列显示logic_gate1。

-

7. To (路径目的地):

-

解释:表示时序路径的终点,通常是另一个寄存器或逻辑单元,表示信号最终传播到哪里。

-

举例:

-

假设信号传播到寄存器

reg2,那么To列会显示reg2。 -

如果信号最终到达逻辑单元

logic_gate2,那么To列显示logic_gate2。

-

8、寄存器的C端和D端

在图中的某些路径中,你可能会看到类似以下的情况:

Count_module_u0/cnt_value_reg[7]/C(C端),表示这是寄存器的时钟输入。Count_module_u0/cnt_value_reg[7]/D(D端),表示这是寄存器的数据输入端。

综合举例:

假设有一条时序路径,路径名称为 Path 1,其从 Count_module_u0/cnt_value_reg[7](寄存器 reg7)开始,到 r_led_reg(寄存器 r_led)结束。假设这条路径的时序裕度为 1.5ns,路径级别为 2,布线数量为 3,扇出为 4,信号从 reg7 到 r_led,其路径的各个字段将是:

-

Name: Path 1

-

Slack: 1.5ns

-

Levels: 2

-

Routes: 3

-

High Fanout: 4

-

From:

Count_module_u0/cnt_value_reg[7] -

To:

r_led_reg

通过这些字段,Vivado能够帮助你了解每条路径的时序信息,识别潜在的时序问题,并进行优化。

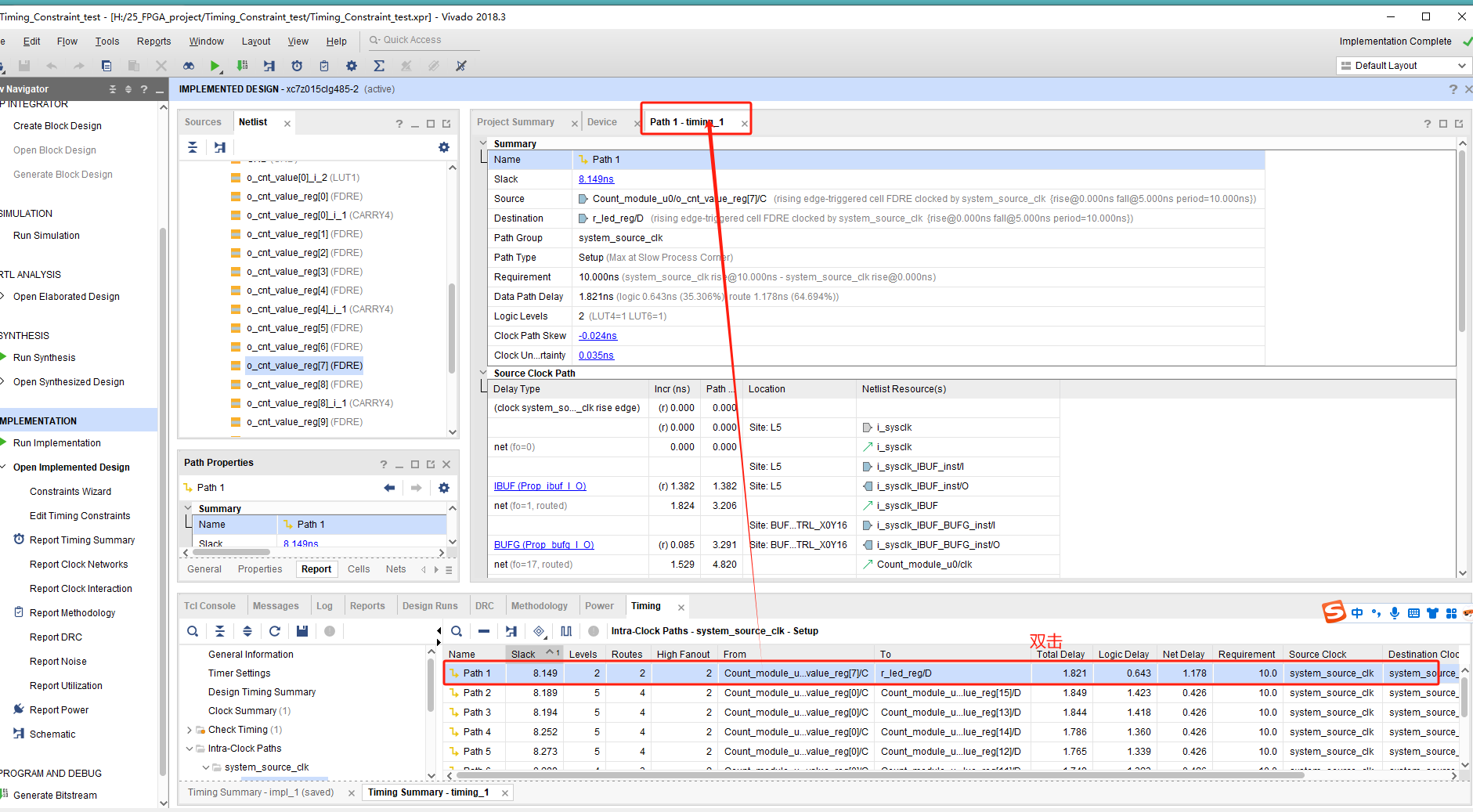

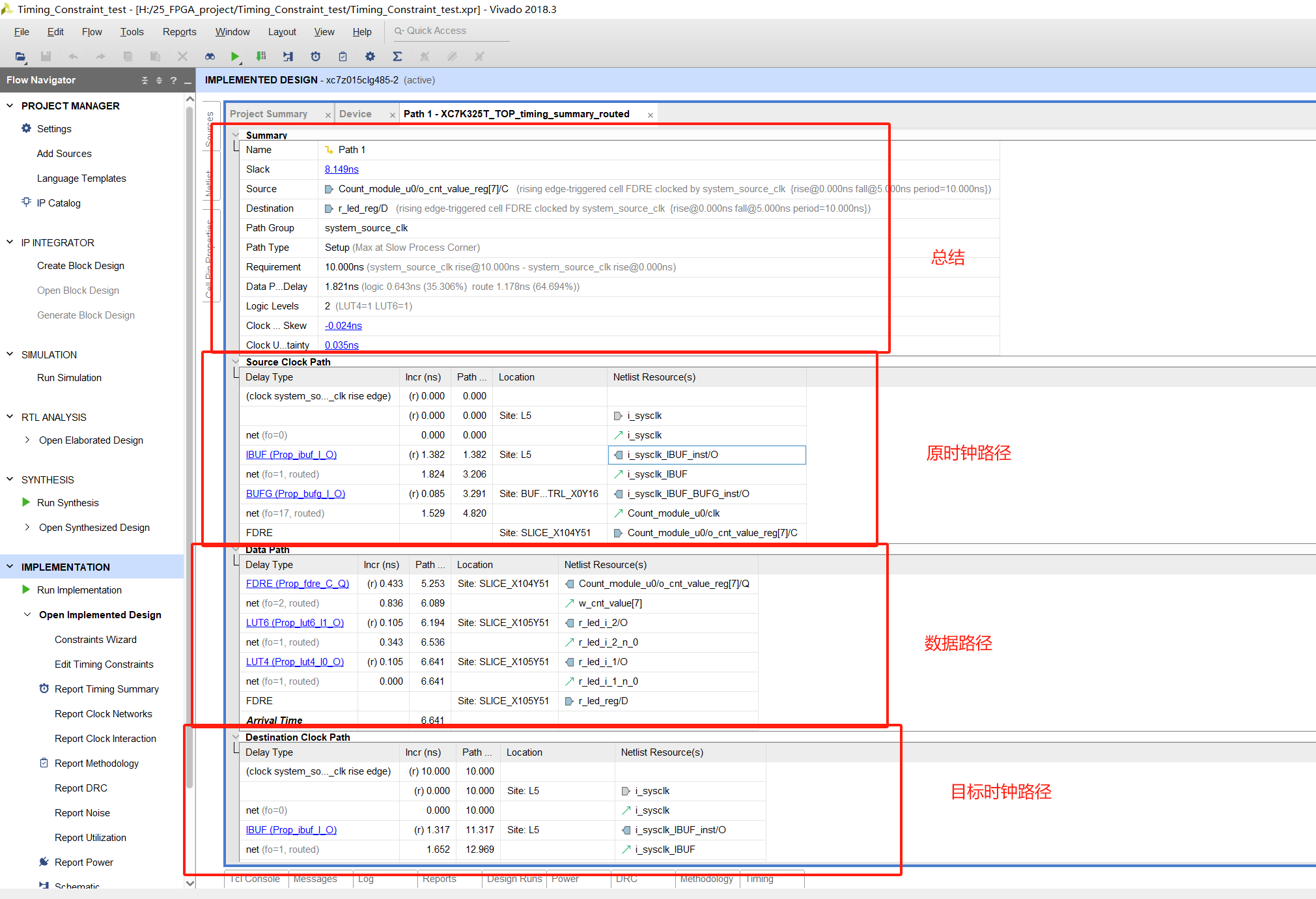

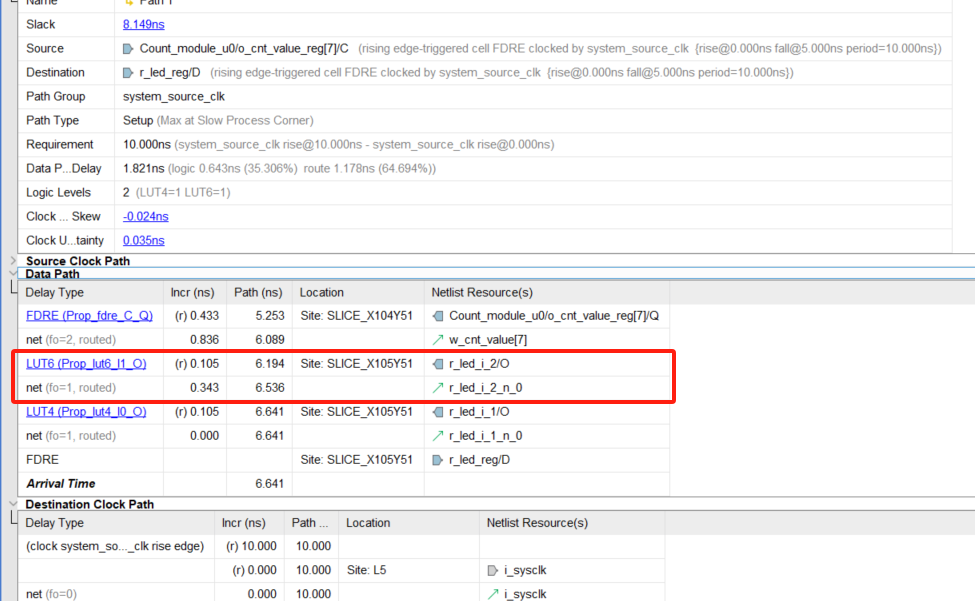

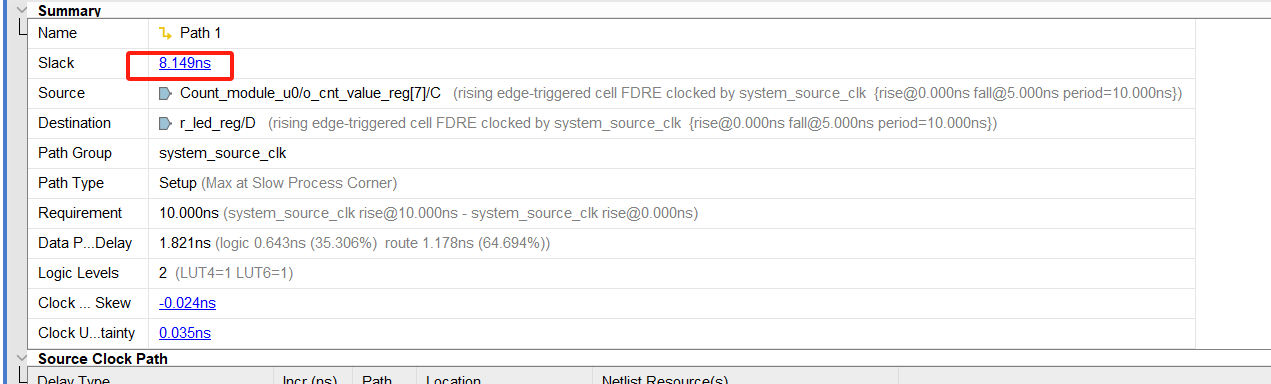

7、细看查看报告

双击查看时序路径详细情况

这个报告展开如下。

查看每一个阶段增加的时延

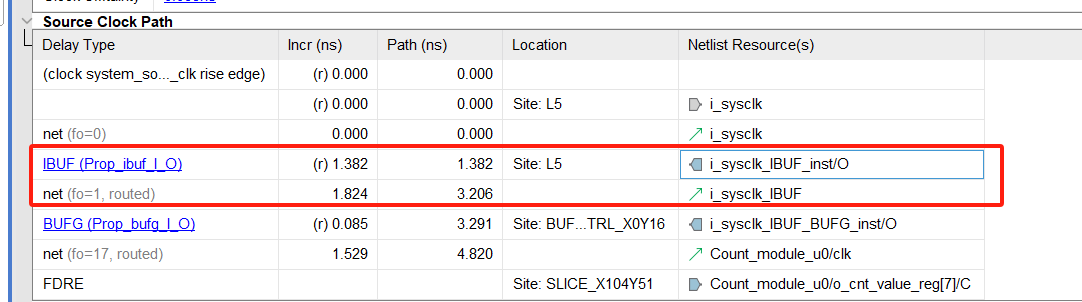

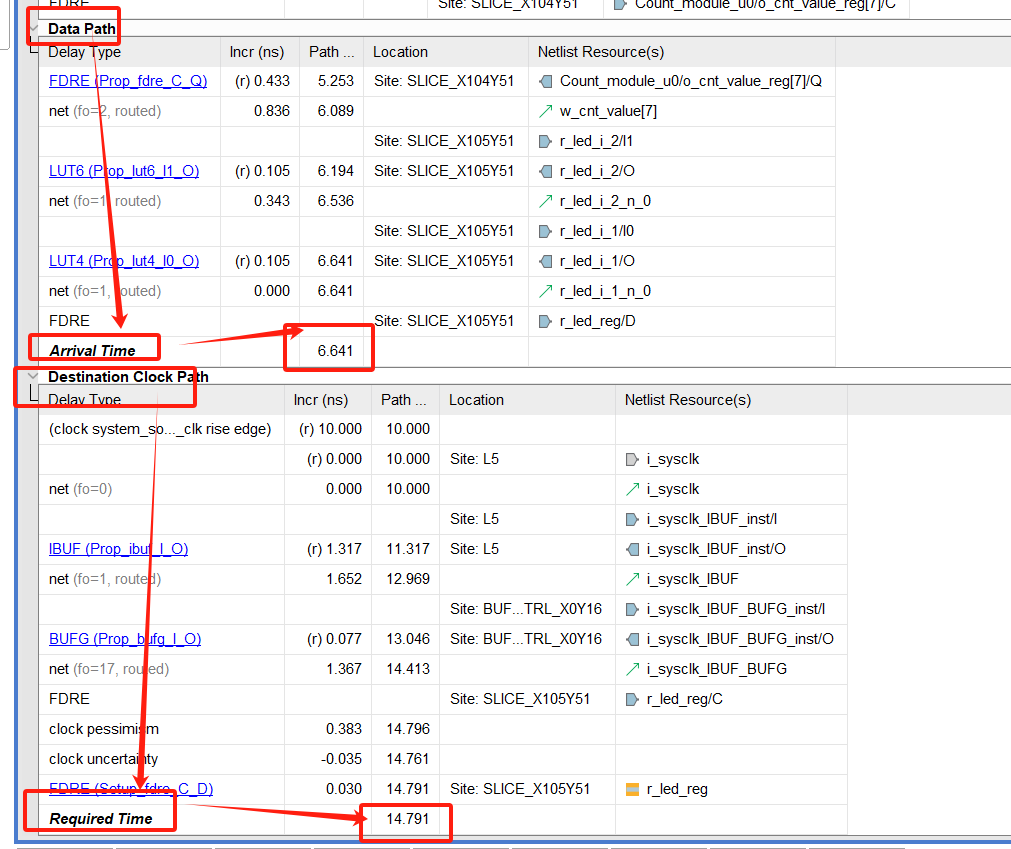

源时钟路径

以下图为例,时钟进入IBUF内部之后,偏移增加了1.382ns,这个时候,整个路径时延为0+1.382

时钟在IBF内部经过了一连串逻辑之后,输出时,偏移增加了1.824ns,这个时候,整个路径时延为0+1.382+1.824=3.206ns

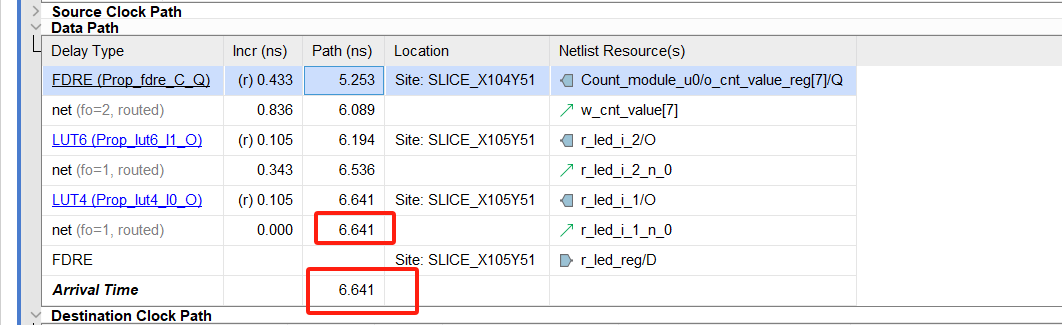

数据路径

FDRE 是Xilinx FPGA器件中的一种基础触发器类型,全称为:

Flip-flop, D-type, synchronous Reset, clock Enable,即:带同步复位和时钟使能的D触发器。

LUT4,LUT6是组合逻辑综合出来的查找表。

net是线网连接逻辑的时延。

数据路径(Data Path)通常指的是信号从一个寄存器(Flip-Flop或触发器)的 Q端(输出端) 出发,经过组合逻辑电路,最终到达下一级寄存器的 D端(输入端) 的传播路径。

前面的Incr,对于FDRE来说,是C到D端的延迟,如下图的0.443。如下图的对于LUT来说,是固有延迟,物理特性,如下图的0.105.

由于线路是并行的,所以我们其实只需要关心延时最大的,如下图的6.641ns的线路,然后如果需要优化,对其进行优化即可。

目的时钟路径

总结

根据报告,能够看出路径的时间裕度8.149ns

往下,能看到数据路径的数据实际到达目标寄存器的时间,是6.641ns,此时时钟到达目标寄存器的时间是14.791ns,两者相减也能得到时间裕度8.149ns

8、约束衍生时钟和异步时钟

需要再去看视频:05如何科学设计FPGA:VIVADO中的时序约束和分析以及进阶技巧_哔哩哔哩_bilibili

从大概1小时的时候开始

1688

1688

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?