视频链接:11_GPIO_EMIO原理与应用_哔哩哔哩_bilibili

小梅哥的官网笔记:

【zynq课程笔记】【裸机】【第11课 】【GPIO_EMIO原理与应用】 - ACZ702开发板 - 芯路恒电子技术论坛 - Powered by Discuz!

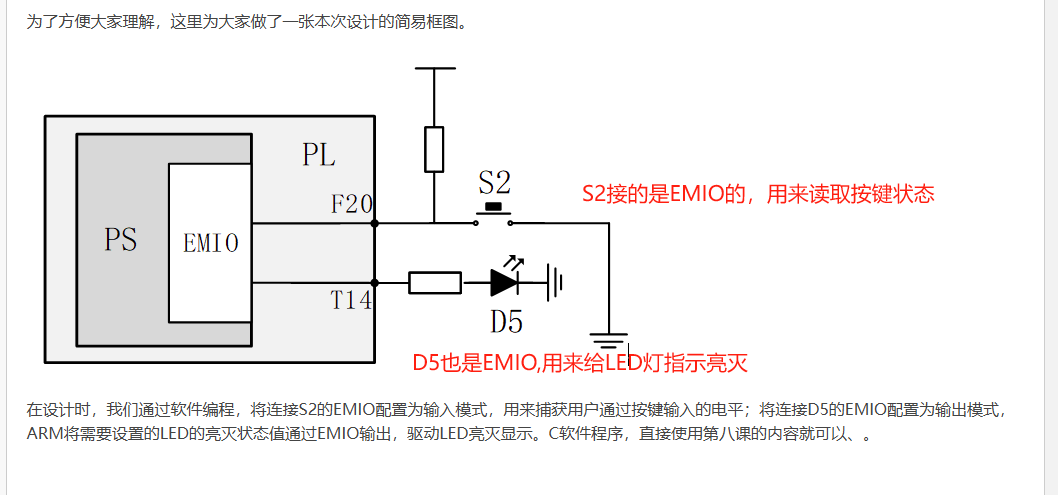

CPU、MIO和EMIO的关系

实验的内容

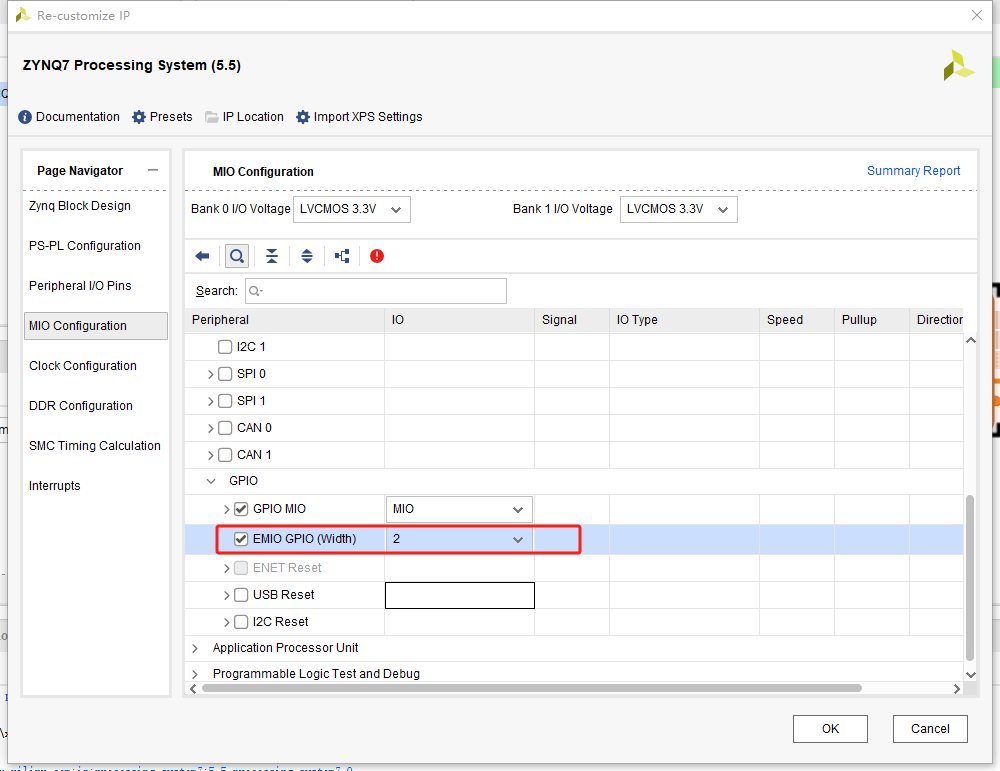

所以配置zynq核的时候,需要给2位的位宽

配置流程

1、添加mio和gpio

2、配置ddr

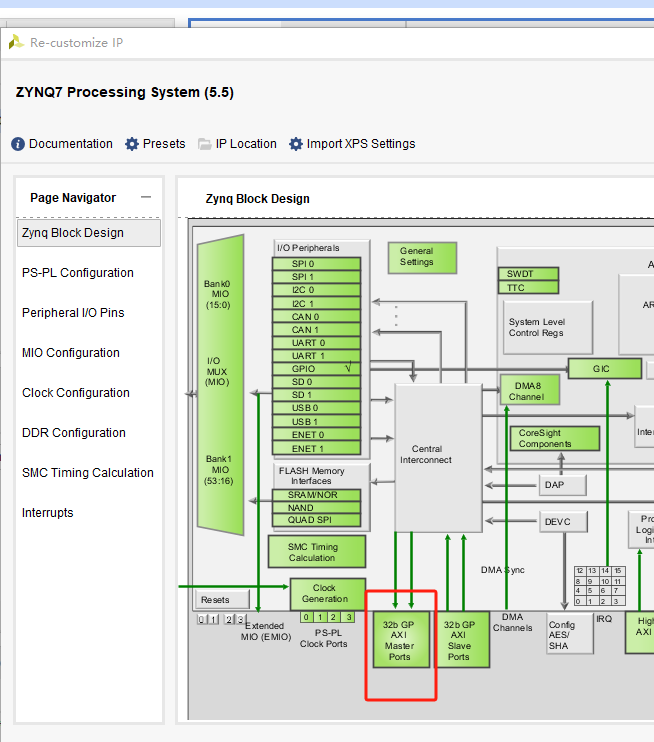

3、去掉不需要的GP接口

4、设置bank1的电压为CMOS1.8v,因为7000系芯片原厂说这样比较安全稳定

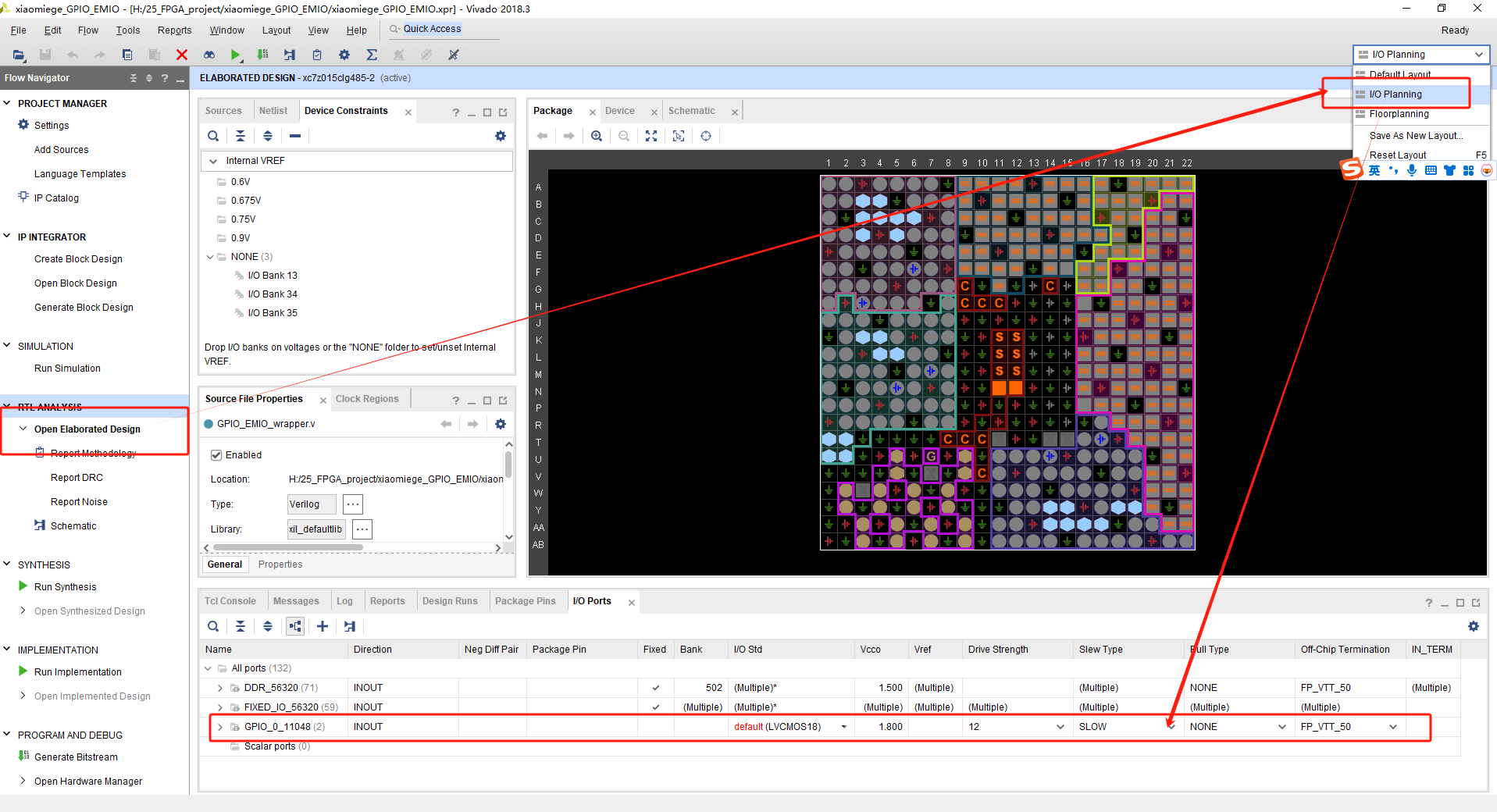

5、引出引脚

5、验证设计

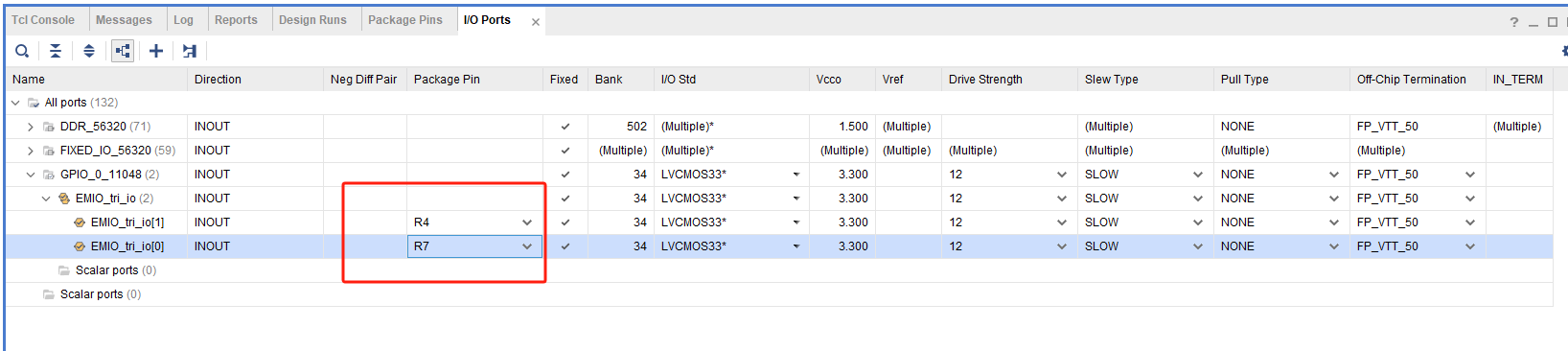

配置相应的管脚

R4是PL侧按键的管脚

R7 是PL侧LED0的管脚

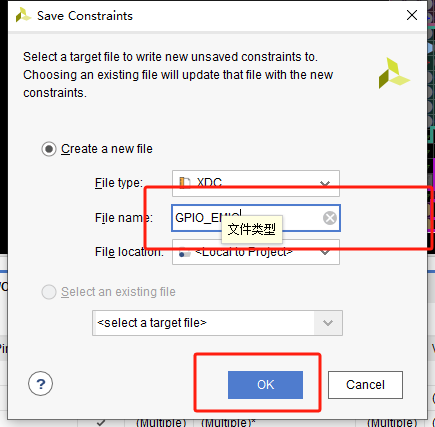

保存XDC文件

生成bitstream

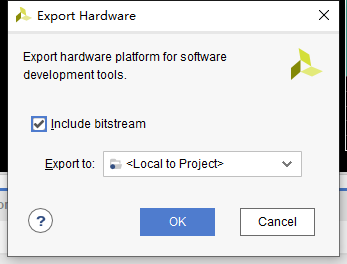

因为用到了FPGA侧的功能,例如管脚。

导出硬件,包含bitsteam

整体的逻辑梳理

在vivado中,将ZYNQ的IP核的EMIO管脚(能读,能写)引出,连接到了对应的PL侧的管脚上。

在SDK中,通过CPU控制管脚的输出,或者读取管脚上面的值,进行进一步的操作。

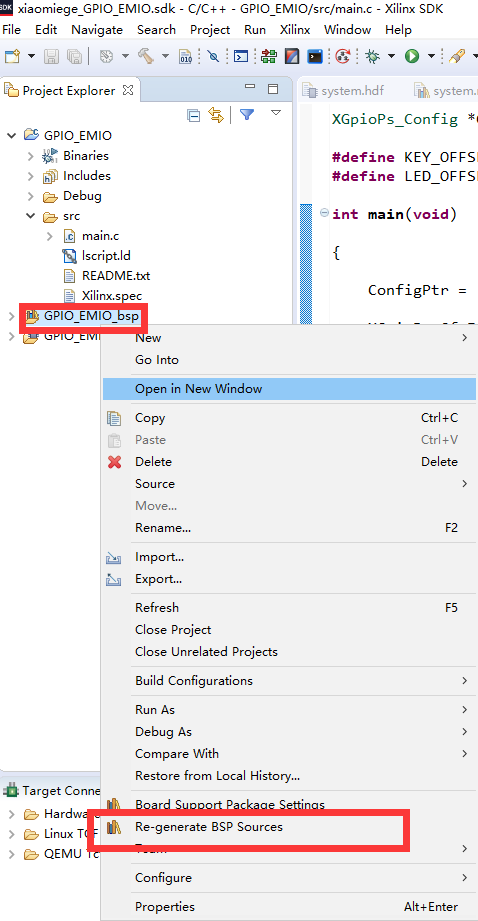

如果vivado更新了比特流文件,发现sdk的main.c报错

只需要更新bsp就可以了

517

517

被折叠的 条评论

为什么被折叠?

被折叠的 条评论

为什么被折叠?